About the Execution of LTSMin+red for SmallOperatingSystem-PT-MT4096DC2048

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 365.403 | 107625.00 | 237304.00 | 441.20 | ?????TFF??F????? | normal |

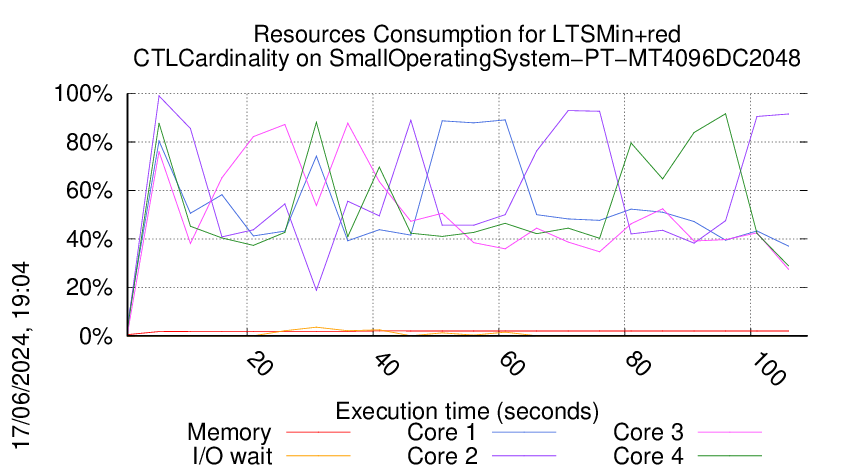

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r532-smll-171683811200313.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.......................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool ltsminxred

Input is SmallOperatingSystem-PT-MT4096DC2048, examination is CTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r532-smll-171683811200313

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 516K

-rw-r--r-- 1 mcc users 9.3K May 14 13:22 CTLCardinality.txt

-rw-r--r-- 1 mcc users 86K May 14 13:22 CTLCardinality.xml

-rw-r--r-- 1 mcc users 7.6K May 14 13:22 CTLFireability.txt

-rw-r--r-- 1 mcc users 64K May 14 13:22 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:43 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.7K May 18 16:43 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.6K Apr 23 07:57 LTLCardinality.txt

-rw-r--r-- 1 mcc users 26K Apr 23 07:57 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K Apr 23 07:57 LTLFireability.txt

-rw-r--r-- 1 mcc users 19K Apr 23 07:57 LTLFireability.xml

-rw-r--r-- 1 mcc users 13K Apr 12 14:20 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 106K Apr 12 14:20 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 13K Apr 12 14:19 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 92K Apr 12 14:19 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.1K Apr 23 07:57 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Apr 23 07:57 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 18 16:43 equiv_col

-rw-r--r-- 1 mcc users 13 May 18 16:43 instance

-rw-r--r-- 1 mcc users 6 May 18 16:43 iscolored

-rw-r--r-- 1 mcc users 8.1K May 18 16:43 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-00

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-01

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-02

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-03

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-04

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-05

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-06

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-07

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-08

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-09

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-10

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-11

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-12

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-13

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-14

FORMULA_NAME SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-15

=== Now, execution of the tool begins

BK_START 1717255811999

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=CTLCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=SmallOperatingSystem-PT-MT4096DC2048

BK_MEMORY_CONFINEMENT=16384

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202405141337

[2024-06-01 15:30:13] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLCardinality, -timeout, 360, -rebuildPNML]

[2024-06-01 15:30:13] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-06-01 15:30:14] [INFO ] Load time of PNML (sax parser for PT used): 193 ms

[2024-06-01 15:30:14] [INFO ] Transformed 9 places.

[2024-06-01 15:30:14] [INFO ] Transformed 8 transitions.

[2024-06-01 15:30:14] [INFO ] Parsed PT model containing 9 places and 8 transitions and 27 arcs in 414 ms.

Parsed 16 properties from file /home/mcc/execution/CTLCardinality.xml in 48 ms.

Support contains 9 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 18 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 9 cols

[2024-06-01 15:30:14] [INFO ] Computed 4 invariants in 5 ms

[2024-06-01 15:30:14] [INFO ] Implicit Places using invariants in 217 ms returned []

[2024-06-01 15:30:14] [INFO ] Invariant cache hit.

[2024-06-01 15:30:14] [INFO ] Implicit Places using invariants and state equation in 74 ms returned []

Implicit Place search using SMT with State Equation took 359 ms to find 0 implicit places.

Running 7 sub problems to find dead transitions.

[2024-06-01 15:30:14] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/8 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/8 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 2 (OVERLAPS) 1/9 variables, 1/4 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 6 (OVERLAPS) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 7 unsolved

No progress, stopping.

After SMT solving in domain Real declared 17/17 variables, and 13 constraints, problems are : Problem set: 0 solved, 7 unsolved in 225 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 7/7 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 7 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/8 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/8 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 2 (OVERLAPS) 1/9 variables, 1/4 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 7/20 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/17 variables, 0/20 constraints. Problems are: Problem set: 0 solved, 7 unsolved

At refinement iteration 7 (OVERLAPS) 0/17 variables, 0/20 constraints. Problems are: Problem set: 0 solved, 7 unsolved

No progress, stopping.

After SMT solving in domain Int declared 17/17 variables, and 20 constraints, problems are : Problem set: 0 solved, 7 unsolved in 148 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 7/7 constraints, Known Traps: 0/0 constraints]

After SMT, in 411ms problems are : Problem set: 0 solved, 7 unsolved

Search for dead transitions found 0 dead transitions in 430ms

Finished structural reductions in LTL mode , in 1 iterations and 866 ms. Remains : 9/9 places, 8/8 transitions.

Support contains 9 out of 9 places after structural reductions.

[2024-06-01 15:30:15] [INFO ] Flatten gal took : 19 ms

[2024-06-01 15:30:15] [INFO ] Flatten gal took : 7 ms

[2024-06-01 15:30:15] [INFO ] Input system was already deterministic with 8 transitions.

RANDOM walk for 40988 steps (8 resets) in 117 ms. (347 steps per ms) remains 69/86 properties

BEST_FIRST walk for 4004 steps (8 resets) in 433 ms. (9 steps per ms) remains 69/69 properties

BEST_FIRST walk for 4003 steps (8 resets) in 107 ms. (37 steps per ms) remains 63/69 properties

BEST_FIRST walk for 4004 steps (8 resets) in 165 ms. (24 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 61 ms. (64 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 102 ms. (38 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 17 ms. (222 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 45 ms. (87 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 41 ms. (95 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 55 ms. (71 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 26 ms. (148 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 20 ms. (190 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 39 ms. (100 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 15 ms. (250 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 43 ms. (91 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 36 ms. (108 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 19 ms. (200 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 34 ms. (114 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 11 ms. (333 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 49 ms. (80 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 25 ms. (154 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 28 ms. (138 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 16 ms. (235 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 50 ms. (78 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 72 ms. (54 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 32 ms. (121 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 44 ms. (88 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 13 ms. (286 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 14 ms. (266 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 11 ms. (333 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 29 ms. (133 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 18 ms. (210 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 19 ms. (200 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 13 ms. (286 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 18 ms. (210 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 27 ms. (143 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 38 ms. (102 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 11 ms. (333 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 14 ms. (266 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 20 ms. (190 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 29 ms. (133 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 15 ms. (250 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 17 ms. (222 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 15 ms. (250 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 27 ms. (143 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 16 ms. (235 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4002 steps (8 resets) in 18 ms. (210 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 18 ms. (210 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 25 ms. (153 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 28 ms. (138 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4003 steps (8 resets) in 27 ms. (142 steps per ms) remains 63/63 properties

BEST_FIRST walk for 4004 steps (8 resets) in 24 ms. (160 steps per ms) remains 63/63 properties

[2024-06-01 15:30:16] [INFO ] Invariant cache hit.

Problem AtomicPropp0 is UNSAT

Problem AtomicPropp1 is UNSAT

Problem AtomicPropp4 is UNSAT

Problem AtomicPropp12 is UNSAT

Problem AtomicPropp13 is UNSAT

Problem AtomicPropp15 is UNSAT

Problem AtomicPropp26 is UNSAT

Problem AtomicPropp35 is UNSAT

Problem AtomicPropp36 is UNSAT

Problem AtomicPropp38 is UNSAT

Problem AtomicPropp40 is UNSAT

Problem AtomicPropp45 is UNSAT

Problem AtomicPropp46 is UNSAT

Problem AtomicPropp49 is UNSAT

Problem AtomicPropp52 is UNSAT

Problem AtomicPropp53 is UNSAT

Problem AtomicPropp63 is UNSAT

Problem AtomicPropp68 is UNSAT

Problem AtomicPropp72 is UNSAT

Problem AtomicPropp80 is UNSAT

Problem AtomicPropp81 is UNSAT

Problem AtomicPropp85 is UNSAT

At refinement iteration 0 (INCLUDED_ONLY) 0/9 variables, 4/4 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 2 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/17 variables, 0/13 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 4 (OVERLAPS) 0/17 variables, 0/13 constraints. Problems are: Problem set: 22 solved, 41 unsolved

No progress, stopping.

After SMT solving in domain Real declared 17/17 variables, and 13 constraints, problems are : Problem set: 22 solved, 41 unsolved in 782 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 63/63 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 22 solved, 41 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/9 variables, 4/4 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 2 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/17 variables, 41/54 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 4 (INCLUDED_ONLY) 0/17 variables, 0/54 constraints. Problems are: Problem set: 22 solved, 41 unsolved

At refinement iteration 5 (OVERLAPS) 0/17 variables, 0/54 constraints. Problems are: Problem set: 22 solved, 41 unsolved

No progress, stopping.

After SMT solving in domain Int declared 17/17 variables, and 54 constraints, problems are : Problem set: 22 solved, 41 unsolved in 791 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 41/63 constraints, Known Traps: 0/0 constraints]

After SMT, in 1626ms problems are : Problem set: 22 solved, 41 unsolved

Parikh walk visited 28 properties in 30124 ms.

Support contains 8 out of 9 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 7 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 7 ms. Remains : 9/9 places, 8/8 transitions.

RANDOM walk for 40988 steps (8 resets) in 136 ms. (299 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 113 ms. (350 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 88 ms. (449 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 105 ms. (377 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40003 steps (8 resets) in 83 ms. (476 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 99 ms. (400 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40002 steps (8 resets) in 70 ms. (563 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40003 steps (8 resets) in 89 ms. (444 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 95 ms. (416 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40003 steps (8 resets) in 73 ms. (540 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 73 ms. (540 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 68 ms. (579 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40003 steps (8 resets) in 46 ms. (851 steps per ms) remains 13/13 properties

BEST_FIRST walk for 40004 steps (8 resets) in 58 ms. (678 steps per ms) remains 13/13 properties

Interrupted probabilistic random walk after 232982 steps, run timeout after 3001 ms. (steps per millisecond=77 ) properties seen :1 out of 13

Probabilistic random walk after 232982 steps, saw 127428 distinct states, run finished after 3034 ms. (steps per millisecond=76 ) properties seen :1

[2024-06-01 15:30:52] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/8 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/8 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 2 (OVERLAPS) 1/9 variables, 1/4 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 6 (OVERLAPS) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 12 unsolved

No progress, stopping.

After SMT solving in domain Real declared 17/17 variables, and 13 constraints, problems are : Problem set: 0 solved, 12 unsolved in 231 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 12/12 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 12 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/8 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/8 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 2 (OVERLAPS) 1/9 variables, 1/4 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 12/25 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/17 variables, 0/25 constraints. Problems are: Problem set: 0 solved, 12 unsolved

At refinement iteration 7 (OVERLAPS) 0/17 variables, 0/25 constraints. Problems are: Problem set: 0 solved, 12 unsolved

No progress, stopping.

After SMT solving in domain Int declared 17/17 variables, and 25 constraints, problems are : Problem set: 0 solved, 12 unsolved in 244 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 12/12 constraints, Known Traps: 0/0 constraints]

After SMT, in 486ms problems are : Problem set: 0 solved, 12 unsolved

Parikh walk visited 7 properties in 45476 ms.

Support contains 7 out of 9 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 2 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 2 ms. Remains : 9/9 places, 8/8 transitions.

RANDOM walk for 40988 steps (8 resets) in 11 ms. (3415 steps per ms) remains 5/5 properties

BEST_FIRST walk for 40004 steps (8 resets) in 37 ms. (1052 steps per ms) remains 5/5 properties

BEST_FIRST walk for 40004 steps (8 resets) in 28 ms. (1379 steps per ms) remains 5/5 properties

BEST_FIRST walk for 40004 steps (8 resets) in 23 ms. (1666 steps per ms) remains 5/5 properties

BEST_FIRST walk for 40003 steps (8 resets) in 25 ms. (1538 steps per ms) remains 5/5 properties

BEST_FIRST walk for 40004 steps (8 resets) in 23 ms. (1666 steps per ms) remains 5/5 properties

Interrupted probabilistic random walk after 366668 steps, run timeout after 3001 ms. (steps per millisecond=122 ) properties seen :0 out of 5

Probabilistic random walk after 366668 steps, saw 200954 distinct states, run finished after 3001 ms. (steps per millisecond=122 ) properties seen :0

[2024-06-01 15:31:41] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/7 variables, 2/2 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/7 variables, 0/2 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 2 (OVERLAPS) 2/9 variables, 2/4 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 6 (OVERLAPS) 0/17 variables, 0/13 constraints. Problems are: Problem set: 0 solved, 5 unsolved

No progress, stopping.

After SMT solving in domain Real declared 17/17 variables, and 13 constraints, problems are : Problem set: 0 solved, 5 unsolved in 90 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 5/5 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 5 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/7 variables, 2/2 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/7 variables, 0/2 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 2 (OVERLAPS) 2/9 variables, 2/4 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 4 (OVERLAPS) 8/17 variables, 9/13 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/17 variables, 5/18 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/17 variables, 0/18 constraints. Problems are: Problem set: 0 solved, 5 unsolved

At refinement iteration 7 (OVERLAPS) 0/17 variables, 0/18 constraints. Problems are: Problem set: 0 solved, 5 unsolved

No progress, stopping.

After SMT solving in domain Int declared 17/17 variables, and 18 constraints, problems are : Problem set: 0 solved, 5 unsolved in 81 ms.

Refiners :[Positive P Invariants (semi-flows): 4/4 constraints, State Equation: 9/9 constraints, PredecessorRefiner: 5/5 constraints, Known Traps: 0/0 constraints]

After SMT, in 189ms problems are : Problem set: 0 solved, 5 unsolved

Finished Parikh walk after 15630 steps, including 0 resets, run visited all 1 properties in 13 ms. (steps per millisecond=1202 )

Finished Parikh walk after 0 steps, including 0 resets, run visited all 0 properties in 1 ms. (steps per millisecond=0 )

Parikh walk visited 5 properties in 17381 ms.

Successfully simplified 22 atomic propositions for a total of 16 simplifications.

FORMULA SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-07 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 4 ms

[2024-06-01 15:31:58] [INFO ] Initial state reduction rules for CTL removed 1 formulas.

FORMULA SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-06 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 3 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Computed a total of 0 stabilizing places and 0 stable transitions

Starting structural reductions in SI_CTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Applied a total of 2 rules in 31 ms. Remains 8 /9 variables (removed 1) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 31 ms. Remains : 8/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 3 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 6 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 6 ms. Remains : 8/9 places, 8/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Discarding 1 places :

Symmetric choice reduction at 1 with 1 rule applications. Total rules 2 place count 7 transition count 7

Iterating global reduction 1 with 1 rules applied. Total rules applied 3 place count 7 transition count 7

Applied a total of 3 rules in 1 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 7/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 1 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 9/9 places, 8/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 3 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 1 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 8/9 places, 8/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 0 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 0 ms. Remains : 9/9 places, 8/8 transitions.

[2024-06-01 15:31:58] [INFO ] Initial state reduction rules for CTL removed 1 formulas.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 3 ms

FORMULA SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-05 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Support contains 0 out of 9 places (down from 5) after GAL structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Applied a total of 2 rules in 0 ms. Remains 8 /9 variables (removed 1) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 0 ms. Remains : 8/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 0 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 0 ms. Remains : 8/9 places, 8/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 8 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Drop transitions (Trivial Post-Agglo cleanup.) removed 2 transitions

Trivial Post-agglo rules discarded 2 transitions

Performed 2 trivial Post agglomeration. Transition count delta: 2

Iterating post reduction 0 with 2 rules applied. Total rules applied 2 place count 8 transition count 6

Reduce places removed 3 places and 0 transitions.

Graph (trivial) has 3 edges and 5 vertex of which 2 / 5 are part of one of the 1 SCC in 3 ms

Free SCC test removed 1 places

Iterating post reduction 1 with 4 rules applied. Total rules applied 6 place count 4 transition count 6

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 2 with 1 rules applied. Total rules applied 7 place count 4 transition count 5

Applied a total of 7 rules in 27 ms. Remains 4 /9 variables (removed 5) and now considering 5/8 (removed 3) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 27 ms. Remains : 4/9 places, 5/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 5 transitions.

RANDOM walk for 16388 steps (0 resets) in 36 ms. (442 steps per ms) remains 0/1 properties

FORMULA SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-10 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Starting structural reductions in SI_CTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 7 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 7 transition count 7

Applied a total of 2 rules in 2 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 2 ms. Remains : 7/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 7 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 7 transition count 7

Applied a total of 2 rules in 2 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 2 ms. Remains : 7/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Discarding 1 places :

Symmetric choice reduction at 1 with 1 rule applications. Total rules 2 place count 7 transition count 7

Iterating global reduction 1 with 1 rules applied. Total rules applied 3 place count 7 transition count 7

Applied a total of 3 rules in 1 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 7/9 places, 7/8 transitions.

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:58] [INFO ] Input system was already deterministic with 7 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 1 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 9/9 places, 8/8 transitions.

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:59] [INFO ] Input system was already deterministic with 8 transitions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Discarding 1 places :

Symmetric choice reduction at 1 with 1 rule applications. Total rules 2 place count 7 transition count 7

Iterating global reduction 1 with 1 rules applied. Total rules applied 3 place count 7 transition count 7

Applied a total of 3 rules in 1 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 1 ms. Remains : 7/9 places, 7/8 transitions.

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 1 ms

[2024-06-01 15:31:59] [INFO ] Input system was already deterministic with 7 transitions.

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 2 ms

[2024-06-01 15:31:59] [INFO ] Flatten gal took : 3 ms

[2024-06-01 15:31:59] [INFO ] Export to MCC of 12 properties in file /home/mcc/execution/CTLCardinality.sr.xml took 5 ms.

[2024-06-01 15:31:59] [INFO ] Export to PNML in file /home/mcc/execution/model.sr.pnml of net with 9 places, 8 transitions and 27 arcs took 2 ms.

Total runtime 105148 ms.

There are residual formulas that ITS could not solve within timeout

Usage: pnml2lts-sym [-gvqh] [--order=

[--mu-opt] [--saturation=

[--sat-granularity=

[--guidance=

[--action=

[--trace=

[--mu=

[--ctl=

[--save-levels=STRING] [--pg-solve] [--attr=

[--saturating-attractor] [--write-strategy=

[--check-strategy] [--interactive-play] [--player]

[--pg-write=

[--edge-label=

[--mucalc=

[--allow-undefined-edges] [--allow-undefined-values]

[-p|--por=

[--weak=[valmari] (default: uses stronger left-commutativity)]

[--leap] [-r|--regroup=<(T,)+>] [--sloan-w1=

[--cw-max-cols=

[--mh-timeout=

[--graph-metrics] [--regroup-exit] [--regroup-time]

[-g|--pins-guards] [--vset=

[--ldd32-cache=

[--cache-ratio=

[--min-free-nodes=

[--fdd-reorder=

[--vset-cache-diff=

[--next-union] [--peak-nodes] [--maxsum=

[--block-size=

[--debug=

[--timeout=INT] [--version] [-h|--help] [--usage]

[OPTIONS]

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-00

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-01

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-02

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-03

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-04

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-08

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-09

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-11

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-12

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-13

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-14

Could not compute solution for formula : SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-15

BK_STOP 1717255919624

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202405141337.jar

+ VERSION=202405141337

+ echo 'Running Version 202405141337'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination CTLCardinality -timeout 360 -rebuildPNML

mcc2024

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-00

ctl formula formula --ctl=/tmp/543/ctl_0_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-01

ctl formula formula --ctl=/tmp/543/ctl_1_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-02

ctl formula formula --ctl=/tmp/543/ctl_2_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-03

ctl formula formula --ctl=/tmp/543/ctl_3_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-04

ctl formula formula --ctl=/tmp/543/ctl_4_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-08

ctl formula formula --ctl=/tmp/543/ctl_5_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-09

ctl formula formula --ctl=/tmp/543/ctl_6_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2024-11

ctl formula formula --ctl=/tmp/543/ctl_7_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-12

ctl formula formula --ctl=/tmp/543/ctl_8_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-13

ctl formula formula --ctl=/tmp/543/ctl_9_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-14

ctl formula formula --ctl=/tmp/543/ctl_10_

ctl formula name SmallOperatingSystem-PT-MT4096DC2048-CTLCardinality-2023-15

ctl formula formula --ctl=/tmp/543/ctl_11_

pnml2lts-sym, ** error **: unknown vector set implementation lddmc

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="SmallOperatingSystem-PT-MT4096DC2048"

export BK_EXAMINATION="CTLCardinality"

export BK_TOOL="ltsminxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool ltsminxred"

echo " Input is SmallOperatingSystem-PT-MT4096DC2048, examination is CTLCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r532-smll-171683811200313"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/SmallOperatingSystem-PT-MT4096DC2048.tgz

mv SmallOperatingSystem-PT-MT4096DC2048 execution

cd execution

if [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "UpperBounds" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] || [ "CTLCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;