About the Execution of LTSMin+red for PermAdmissibility-PT-50

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 1189.607 | 211187.00 | 505578.00 | 561.90 | FFF?FTTFTTFFFFFF | normal |

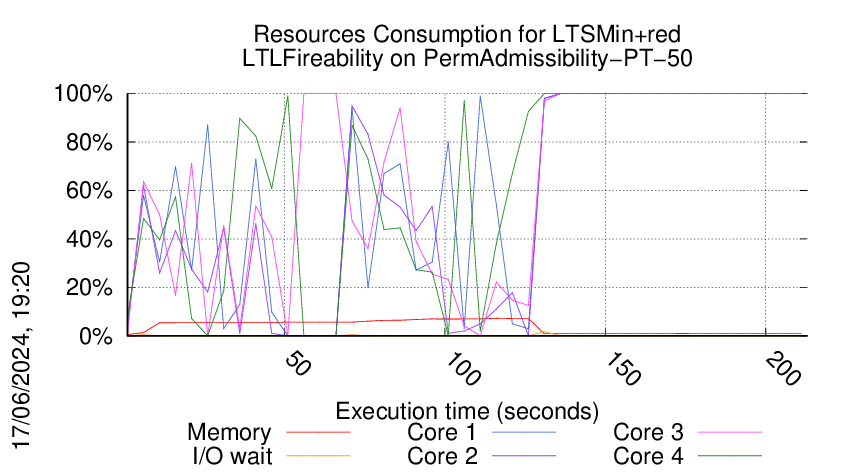

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r512-smll-171654407100196.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

...........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool ltsminxred

Input is PermAdmissibility-PT-50, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r512-smll-171654407100196

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.7M

-rw-r--r-- 1 mcc users 9.3K Apr 12 09:07 CTLCardinality.txt

-rw-r--r-- 1 mcc users 81K Apr 12 09:07 CTLCardinality.xml

-rw-r--r-- 1 mcc users 56K Apr 12 09:05 CTLFireability.txt

-rw-r--r-- 1 mcc users 296K Apr 12 09:05 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:43 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.3K May 18 16:43 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 5.3K Apr 23 07:42 LTLCardinality.txt

-rw-r--r-- 1 mcc users 33K Apr 23 07:42 LTLCardinality.xml

-rw-r--r-- 1 mcc users 13K Apr 23 07:42 LTLFireability.txt

-rw-r--r-- 1 mcc users 53K Apr 23 07:42 LTLFireability.xml

-rw-r--r-- 1 mcc users 13K Apr 12 09:15 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 108K Apr 12 09:15 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 98K Apr 12 09:14 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 501K Apr 12 09:14 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.0K Apr 23 07:42 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.6K Apr 23 07:42 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 18 16:43 equiv_col

-rw-r--r-- 1 mcc users 3 May 18 16:43 instance

-rw-r--r-- 1 mcc users 6 May 18 16:43 iscolored

-rw-r--r-- 1 mcc users 340K May 18 16:43 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-00

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-01

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-02

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-03

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-04

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-05

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-06

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-07

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-08

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-09

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-10

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-11

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-12

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-13

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-14

FORMULA_NAME PermAdmissibility-PT-50-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1717256878860

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=LTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=PermAdmissibility-PT-50

BK_MEMORY_CONFINEMENT=16384

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202405141337

[2024-06-01 15:48:01] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -timeout, 360, -rebuildPNML]

[2024-06-01 15:48:01] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-06-01 15:48:01] [INFO ] Load time of PNML (sax parser for PT used): 265 ms

[2024-06-01 15:48:02] [INFO ] Transformed 168 places.

[2024-06-01 15:48:02] [INFO ] Transformed 592 transitions.

[2024-06-01 15:48:02] [INFO ] Parsed PT model containing 168 places and 592 transitions and 3456 arcs in 605 ms.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 39 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 3 formulas.

FORMULA PermAdmissibility-PT-50-LTLFireability-00 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA PermAdmissibility-PT-50-LTLFireability-06 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA PermAdmissibility-PT-50-LTLFireability-09 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 87 out of 168 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 168/168 places, 592/592 transitions.

Reduce places removed 64 places and 0 transitions.

Iterating post reduction 0 with 64 rules applied. Total rules applied 64 place count 104 transition count 592

Applied a total of 64 rules in 69 ms. Remains 104 /168 variables (removed 64) and now considering 592/592 (removed 0) transitions.

// Phase 1: matrix 592 rows 104 cols

[2024-06-01 15:48:02] [INFO ] Computed 16 invariants in 77 ms

[2024-06-01 15:48:03] [INFO ] Implicit Places using invariants in 486 ms returned []

[2024-06-01 15:48:03] [INFO ] Invariant cache hit.

[2024-06-01 15:48:03] [INFO ] Implicit Places using invariants and state equation in 599 ms returned []

Implicit Place search using SMT with State Equation took 1158 ms to find 0 implicit places.

Running 588 sub problems to find dead transitions.

[2024-06-01 15:48:03] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/103 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/103 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 2 (OVERLAPS) 1/104 variables, 13/16 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/104 variables, 0/16 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 4 (OVERLAPS) 592/696 variables, 104/120 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/696 variables, 0/120 constraints. Problems are: Problem set: 0 solved, 588 unsolved

Error getting values : (error "ParserException while parsing response: (timeout

org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 6 (OVERLAPS) 0/696 variables, 0/120 constraints. Problems are: Problem set: 0 solved, 588 unsolved

No progress, stopping.

After SMT solving in domain Real declared 696/696 variables, and 120 constraints, problems are : Problem set: 0 solved, 588 unsolved in 30064 ms.

Refiners :[Generalized P Invariants (flows): 16/16 constraints, State Equation: 104/104 constraints, PredecessorRefiner: 588/588 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 588 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/103 variables, 3/3 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/103 variables, 0/3 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 2 (OVERLAPS) 1/104 variables, 13/16 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/104 variables, 0/16 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 4 (OVERLAPS) 592/696 variables, 104/120 constraints. Problems are: Problem set: 0 solved, 588 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/696 variables, 588/708 constraints. Problems are: Problem set: 0 solved, 588 unsolved

Solver is answering 'unknown', stopping.

After SMT solving in domain Int declared 696/696 variables, and 708 constraints, problems are : Problem set: 0 solved, 588 unsolved in 30046 ms.

Refiners :[Generalized P Invariants (flows): 16/16 constraints, State Equation: 104/104 constraints, PredecessorRefiner: 588/588 constraints, Known Traps: 0/0 constraints]

After SMT, in 62656ms problems are : Problem set: 0 solved, 588 unsolved

Search for dead transitions found 0 dead transitions in 62720ms

Starting structural reductions in LTL mode, iteration 1 : 104/168 places, 592/592 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 64006 ms. Remains : 104/168 places, 592/592 transitions.

Support contains 87 out of 104 places after structural reductions.

[2024-06-01 15:49:06] [INFO ] Flatten gal took : 130 ms

[2024-06-01 15:49:07] [INFO ] Flatten gal took : 89 ms

[2024-06-01 15:49:07] [INFO ] Input system was already deterministic with 592 transitions.

Reduction of identical properties reduced properties to check from 28 to 26

RANDOM walk for 40088 steps (48 resets) in 929 ms. (43 steps per ms) remains 2/26 properties

BEST_FIRST walk for 32895 steps (6 resets) in 1175 ms. (27 steps per ms) remains 0/2 properties

FORMULA PermAdmissibility-PT-50-LTLFireability-07 FALSE TECHNIQUES REACHABILITY_KNOWLEDGE

Computed a total of 104 stabilizing places and 592 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 104 transition count 592

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((p0 U ((X(p2)||p1) U p3)))'

Support contains 40 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 13 places :

Symmetric choice reduction at 0 with 13 rule applications. Total rules 13 place count 91 transition count 468

Iterating global reduction 0 with 13 rules applied. Total rules applied 26 place count 91 transition count 468

Applied a total of 26 rules in 21 ms. Remains 91 /104 variables (removed 13) and now considering 468/592 (removed 124) transitions.

// Phase 1: matrix 468 rows 91 cols

[2024-06-01 15:49:08] [INFO ] Computed 16 invariants in 9 ms

[2024-06-01 15:49:08] [INFO ] Implicit Places using invariants in 165 ms returned [18]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 168 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 90/104 places, 468/592 transitions.

Applied a total of 0 rules in 6 ms. Remains 90 /90 variables (removed 0) and now considering 468/468 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 195 ms. Remains : 90/104 places, 468/592 transitions.

Stuttering acceptance computed with spot in 345 ms :[true, (OR (NOT p2) (NOT p3)), (NOT p3), (NOT p3)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-01

Entered a terminal (fully accepting) state of product in 4 steps with 0 reset in 2 ms.

FORMULA PermAdmissibility-PT-50-LTLFireability-01 FALSE TECHNIQUES STUTTER_TEST

Treatment of property PermAdmissibility-PT-50-LTLFireability-01 finished in 633 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G((X(F((p1&&X(F(p1)))))||p0)))'

Support contains 9 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 26 places :

Symmetric choice reduction at 0 with 26 rule applications. Total rules 26 place count 78 transition count 344

Iterating global reduction 0 with 26 rules applied. Total rules applied 52 place count 78 transition count 344

Discarding 24 places :

Symmetric choice reduction at 0 with 24 rule applications. Total rules 76 place count 54 transition count 108

Iterating global reduction 0 with 24 rules applied. Total rules applied 100 place count 54 transition count 108

Discarding 2 places :

Symmetric choice reduction at 0 with 2 rule applications. Total rules 102 place count 52 transition count 92

Iterating global reduction 0 with 2 rules applied. Total rules applied 104 place count 52 transition count 92

Applied a total of 104 rules in 18 ms. Remains 52 /104 variables (removed 52) and now considering 92/592 (removed 500) transitions.

// Phase 1: matrix 92 rows 52 cols

[2024-06-01 15:49:09] [INFO ] Computed 16 invariants in 4 ms

[2024-06-01 15:49:09] [INFO ] Implicit Places using invariants in 123 ms returned [0, 5, 19, 26]

[2024-06-01 15:49:09] [INFO ] Actually due to overlaps returned [0, 5, 19]

Discarding 3 places :

Implicit Place search using SMT only with invariants took 125 ms to find 3 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 49/104 places, 92/592 transitions.

Applied a total of 0 rules in 2 ms. Remains 49 /49 variables (removed 0) and now considering 92/92 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 145 ms. Remains : 49/104 places, 92/592 transitions.

Stuttering acceptance computed with spot in 138 ms :[(AND (NOT p0) (NOT p1)), (NOT p1), (NOT p1)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-02

Product exploration explored 100000 steps with 4217 reset in 1042 ms.

Product exploration explored 100000 steps with 4259 reset in 664 ms.

Computed a total of 49 stabilizing places and 92 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 49 transition count 92

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p0) (NOT p1)), (X (NOT p1)), (X (X (NOT p1))), (F (G (NOT p0))), (F (G (NOT p1)))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 5 factoid took 130 ms. Reduced automaton from 3 states, 5 edges and 2 AP (stutter sensitive) to 5 states, 11 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 243 ms :[(AND (NOT p0) (NOT p1)), (NOT p1), (NOT p1), false, false]

Reduction of identical properties reduced properties to check from 4 to 2

RANDOM walk for 40068 steps (48 resets) in 116 ms. (342 steps per ms) remains 1/2 properties

BEST_FIRST walk for 40004 steps (8 resets) in 2364 ms. (16 steps per ms) remains 1/1 properties

// Phase 1: matrix 92 rows 49 cols

[2024-06-01 15:49:12] [INFO ] Computed 13 invariants in 5 ms

Problem apf3 is UNSAT

After SMT solving in domain Real declared 9/141 variables, and 0 constraints, problems are : Problem set: 1 solved, 0 unsolved in 20 ms.

Refiners :[Generalized P Invariants (flows): 0/13 constraints, State Equation: 0/49 constraints, PredecessorRefiner: 1/1 constraints, Known Traps: 0/0 constraints]

After SMT, in 40ms problems are : Problem set: 1 solved, 0 unsolved

Skipping Parikh replay, no witness traces provided.

Found 1 invariant AP formulas.

Knowledge obtained : [(AND (NOT p0) (NOT p1)), (X (NOT p1)), (X (X (NOT p1))), (F (G (NOT p0))), (F (G (NOT p1))), (G (OR p0 (NOT p1)))]

False Knowledge obtained : [(F p0), (F (NOT (OR (NOT p0) (NOT p1)))), (F p1)]

Property proved to be false thanks to negative knowledge :(F p0)

Knowledge based reduction with 6 factoid took 167 ms. Reduced automaton from 5 states, 11 edges and 2 AP (stutter insensitive) to 1 states, 1 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-02 FALSE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-02 finished in 3369 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((X((G(G(p0))||!(p1 U !p0)))&&F(p1)))'

Support contains 22 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 26 places :

Symmetric choice reduction at 0 with 26 rule applications. Total rules 26 place count 78 transition count 344

Iterating global reduction 0 with 26 rules applied. Total rules applied 52 place count 78 transition count 344

Discarding 10 places :

Symmetric choice reduction at 0 with 10 rule applications. Total rules 62 place count 68 transition count 234

Iterating global reduction 0 with 10 rules applied. Total rules applied 72 place count 68 transition count 234

Applied a total of 72 rules in 17 ms. Remains 68 /104 variables (removed 36) and now considering 234/592 (removed 358) transitions.

// Phase 1: matrix 234 rows 68 cols

[2024-06-01 15:49:12] [INFO ] Computed 16 invariants in 6 ms

[2024-06-01 15:49:12] [INFO ] Implicit Places using invariants in 378 ms returned [0, 5]

Discarding 2 places :

Implicit Place search using SMT only with invariants took 381 ms to find 2 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 66/104 places, 234/592 transitions.

Applied a total of 0 rules in 1 ms. Remains 66 /66 variables (removed 0) and now considering 234/234 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 400 ms. Remains : 66/104 places, 234/592 transitions.

Stuttering acceptance computed with spot in 162 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1), true]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-03

Product exploration explored 100000 steps with 4842 reset in 1064 ms.

Product exploration explored 100000 steps with 4891 reset in 1024 ms.

Computed a total of 66 stabilizing places and 234 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 66 transition count 234

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p1) p0), (X (NOT (AND p1 p0))), (X p0), (X (NOT p1)), (X (X (NOT (AND p1 p0)))), (X (X p0)), (X (X (NOT p1))), (F (G (NOT p1))), (F (G p0))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 9 factoid took 235 ms. Reduced automaton from 4 states, 6 edges and 2 AP (stutter sensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 84 ms :[(NOT p1), (NOT p1)]

RANDOM walk for 1353 steps (0 resets) in 7 ms. (169 steps per ms) remains 0/1 properties

Knowledge obtained : [(AND (NOT p1) p0), (X (NOT (AND p1 p0))), (X p0), (X (NOT p1)), (X (X (NOT (AND p1 p0)))), (X (X p0)), (X (X (NOT p1))), (F (G (NOT p1))), (F (G p0))]

False Knowledge obtained : [(F p1)]

Knowledge based reduction with 9 factoid took 371 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 84 ms :[(NOT p1), (NOT p1)]

Stuttering acceptance computed with spot in 78 ms :[(NOT p1), (NOT p1)]

// Phase 1: matrix 234 rows 66 cols

[2024-06-01 15:49:16] [INFO ] Computed 14 invariants in 2 ms

[2024-06-01 15:49:16] [INFO ] [Real]Absence check using 0 positive and 14 generalized place invariants in 24 ms returned sat

[2024-06-01 15:49:16] [INFO ] [Real]Absence check using state equation in 146 ms returned sat

[2024-06-01 15:49:16] [INFO ] Solution in real domain found non-integer solution.

[2024-06-01 15:49:17] [INFO ] [Nat]Absence check using 0 positive and 14 generalized place invariants in 13 ms returned sat

[2024-06-01 15:49:17] [INFO ] [Nat]Absence check using state equation in 112 ms returned sat

[2024-06-01 15:49:17] [INFO ] Computed and/alt/rep : 31/197/31 causal constraints (skipped 199 transitions) in 55 ms.

[2024-06-01 15:49:17] [INFO ] Added : 18 causal constraints over 4 iterations in 214 ms. Result :sat

Could not prove EG (NOT p1)

Support contains 17 out of 66 places. Attempting structural reductions.

Property had overlarge support with respect to TGBA, discarding it for now.

Starting structural reductions in SI_LTL mode, iteration 0 : 66/66 places, 234/234 transitions.

Graph (complete) has 349 edges and 66 vertex of which 58 are kept as prefixes of interest. Removing 8 places using SCC suffix rule.4 ms

Discarding 8 places :

Also discarding 8 output transitions

Drop transitions (Output transitions of discarded places.) removed 8 transitions

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 5 place count 54 transition count 210

Iterating global reduction 0 with 4 rules applied. Total rules applied 9 place count 54 transition count 210

Applied a total of 9 rules in 36 ms. Remains 54 /66 variables (removed 12) and now considering 210/234 (removed 24) transitions.

// Phase 1: matrix 210 rows 54 cols

[2024-06-01 15:49:17] [INFO ] Computed 12 invariants in 3 ms

[2024-06-01 15:49:17] [INFO ] Implicit Places using invariants in 114 ms returned [17, 34]

[2024-06-01 15:49:17] [INFO ] Actually due to overlaps returned [17]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 117 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 53/66 places, 210/234 transitions.

Applied a total of 0 rules in 14 ms. Remains 53 /53 variables (removed 0) and now considering 210/210 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 169 ms. Remains : 53/66 places, 210/234 transitions.

Computed a total of 53 stabilizing places and 210 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 53 transition count 210

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p1), (X (NOT p1)), (X (X (NOT p1))), (F (G (NOT p1)))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 124 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 87 ms :[(NOT p1), (NOT p1)]

RANDOM walk for 2044 steps (0 resets) in 7 ms. (255 steps per ms) remains 0/1 properties

Knowledge obtained : [(NOT p1), (X (NOT p1)), (X (X (NOT p1))), (F (G (NOT p1)))]

False Knowledge obtained : [(F p1)]

Knowledge based reduction with 4 factoid took 119 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 72 ms :[(NOT p1), (NOT p1)]

Stuttering acceptance computed with spot in 71 ms :[(NOT p1), (NOT p1)]

// Phase 1: matrix 210 rows 53 cols

[2024-06-01 15:49:18] [INFO ] Computed 11 invariants in 1 ms

[2024-06-01 15:49:19] [INFO ] [Real]Absence check using 0 positive and 11 generalized place invariants in 18 ms returned sat

[2024-06-01 15:49:19] [INFO ] [Real]Absence check using state equation in 110 ms returned sat

[2024-06-01 15:49:19] [INFO ] Solution in real domain found non-integer solution.

[2024-06-01 15:49:20] [INFO ] [Nat]Absence check using 0 positive and 11 generalized place invariants in 16 ms returned sat

[2024-06-01 15:49:20] [INFO ] [Nat]Absence check using state equation in 108 ms returned sat

[2024-06-01 15:49:20] [INFO ] Computed and/alt/rep : 92/752/92 causal constraints (skipped 114 transitions) in 54 ms.

[2024-06-01 15:49:20] [INFO ] Added : 40 causal constraints over 9 iterations in 235 ms. Result :sat

Could not prove EG (NOT p1)

Stuttering acceptance computed with spot in 89 ms :[(NOT p1), (NOT p1)]

Product exploration explored 100000 steps with 1409 reset in 1186 ms.

Product exploration explored 100000 steps with 1417 reset in 1181 ms.

Support contains 17 out of 53 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 53/53 places, 210/210 transitions.

Applied a total of 0 rules in 8 ms. Remains 53 /53 variables (removed 0) and now considering 210/210 (removed 0) transitions.

[2024-06-01 15:49:22] [INFO ] Invariant cache hit.

[2024-06-01 15:49:22] [INFO ] Implicit Places using invariants in 120 ms returned [33]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 121 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 52/53 places, 210/210 transitions.

Drop transitions (Trivial Post-Agglo cleanup.) removed 1 transitions

Trivial Post-agglo rules discarded 1 transitions

Performed 1 trivial Post agglomeration. Transition count delta: 1

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 52 transition count 209

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 1 with 1 rules applied. Total rules applied 2 place count 51 transition count 209

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 1 Pre rules applied. Total rules applied 2 place count 51 transition count 208

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 2 with 2 rules applied. Total rules applied 4 place count 50 transition count 208

Applied a total of 4 rules in 22 ms. Remains 50 /52 variables (removed 2) and now considering 208/210 (removed 2) transitions.

// Phase 1: matrix 208 rows 50 cols

[2024-06-01 15:49:22] [INFO ] Computed 10 invariants in 2 ms

[2024-06-01 15:49:23] [INFO ] Implicit Places using invariants in 81 ms returned []

[2024-06-01 15:49:23] [INFO ] Invariant cache hit.

[2024-06-01 15:49:23] [INFO ] Implicit Places using invariants and state equation in 140 ms returned []

Implicit Place search using SMT with State Equation took 226 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 50/53 places, 208/210 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 377 ms. Remains : 50/53 places, 208/210 transitions.

Treatment of property PermAdmissibility-PT-50-LTLFireability-03 finished in 10909 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(G(p0)))'

Support contains 17 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 13 places :

Symmetric choice reduction at 0 with 13 rule applications. Total rules 13 place count 91 transition count 468

Iterating global reduction 0 with 13 rules applied. Total rules applied 26 place count 91 transition count 468

Applied a total of 26 rules in 12 ms. Remains 91 /104 variables (removed 13) and now considering 468/592 (removed 124) transitions.

// Phase 1: matrix 468 rows 91 cols

[2024-06-01 15:49:23] [INFO ] Computed 16 invariants in 6 ms

[2024-06-01 15:49:23] [INFO ] Implicit Places using invariants in 208 ms returned [0]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 214 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 90/104 places, 468/592 transitions.

Applied a total of 0 rules in 5 ms. Remains 90 /90 variables (removed 0) and now considering 468/468 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 231 ms. Remains : 90/104 places, 468/592 transitions.

Stuttering acceptance computed with spot in 114 ms :[true, (NOT p0), (NOT p0)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-04

Entered a terminal (fully accepting) state of product in 32 steps with 0 reset in 1 ms.

FORMULA PermAdmissibility-PT-50-LTLFireability-04 FALSE TECHNIQUES STUTTER_TEST

Treatment of property PermAdmissibility-PT-50-LTLFireability-04 finished in 373 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(p0)))'

Support contains 9 out of 104 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Graph (complete) has 975 edges and 104 vertex of which 32 are kept as prefixes of interest. Removing 72 places using SCC suffix rule.4 ms

Discarding 72 places :

Also discarding 512 output transitions

Drop transitions (Output transitions of discarded places.) removed 512 transitions

Discarding 5 places :

Symmetric choice reduction at 0 with 5 rule applications. Total rules 6 place count 27 transition count 52

Iterating global reduction 0 with 5 rules applied. Total rules applied 11 place count 27 transition count 52

Applied a total of 11 rules in 12 ms. Remains 27 /104 variables (removed 77) and now considering 52/592 (removed 540) transitions.

// Phase 1: matrix 52 rows 27 cols

[2024-06-01 15:49:23] [INFO ] Computed 8 invariants in 1 ms

[2024-06-01 15:49:23] [INFO ] Implicit Places using invariants in 61 ms returned [12]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 63 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 26/104 places, 52/592 transitions.

Applied a total of 0 rules in 4 ms. Remains 26 /26 variables (removed 0) and now considering 52/52 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 79 ms. Remains : 26/104 places, 52/592 transitions.

Stuttering acceptance computed with spot in 36 ms :[(NOT p0)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-05

Product exploration explored 100000 steps with 249 reset in 1184 ms.

Product exploration explored 100000 steps with 249 reset in 822 ms.

Computed a total of 26 stabilizing places and 52 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 26 transition count 52

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [p0, (X p0), (X (X p0)), (F (G p0))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge (Minato strategy)

Knowledge based reduction with 4 factoid took 22 ms. Reduced automaton from 1 states, 2 edges and 1 AP (stutter insensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-05 TRUE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-05 finished in 2207 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((X(F(p0))&&F(p1)))'

Support contains 5 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 26 places :

Symmetric choice reduction at 0 with 26 rule applications. Total rules 26 place count 78 transition count 344

Iterating global reduction 0 with 26 rules applied. Total rules applied 52 place count 78 transition count 344

Discarding 24 places :

Symmetric choice reduction at 0 with 24 rule applications. Total rules 76 place count 54 transition count 108

Iterating global reduction 0 with 24 rules applied. Total rules applied 100 place count 54 transition count 108

Discarding 3 places :

Symmetric choice reduction at 0 with 3 rule applications. Total rules 103 place count 51 transition count 84

Iterating global reduction 0 with 3 rules applied. Total rules applied 106 place count 51 transition count 84

Applied a total of 106 rules in 10 ms. Remains 51 /104 variables (removed 53) and now considering 84/592 (removed 508) transitions.

// Phase 1: matrix 84 rows 51 cols

[2024-06-01 15:49:26] [INFO ] Computed 16 invariants in 1 ms

[2024-06-01 15:49:26] [INFO ] Implicit Places using invariants in 111 ms returned [0, 5, 18, 25]

[2024-06-01 15:49:26] [INFO ] Actually due to overlaps returned [0, 5, 18]

Discarding 3 places :

Implicit Place search using SMT only with invariants took 114 ms to find 3 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 48/104 places, 84/592 transitions.

Applied a total of 0 rules in 0 ms. Remains 48 /48 variables (removed 0) and now considering 84/84 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 125 ms. Remains : 48/104 places, 84/592 transitions.

Stuttering acceptance computed with spot in 143 ms :[(OR (NOT p1) (NOT p0)), (NOT p0), (NOT p1)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-08

Product exploration explored 100000 steps with 33159 reset in 191 ms.

Product exploration explored 100000 steps with 33357 reset in 208 ms.

Computed a total of 48 stabilizing places and 84 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 48 transition count 84

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p1) p0), (X p0), (X (NOT p1)), (X (X p0)), (F (G (NOT p1))), (F (G p0))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1))]

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 6 factoid took 230 ms. Reduced automaton from 3 states, 4 edges and 2 AP (stutter sensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 89 ms :[(NOT p1), (NOT p1)]

RANDOM walk for 208 steps (0 resets) in 4 ms. (41 steps per ms) remains 0/1 properties

Knowledge obtained : [(AND (NOT p1) p0), (X p0), (X (NOT p1)), (X (X p0)), (F (G (NOT p1))), (F (G p0))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1)), (F p1)]

Knowledge based reduction with 6 factoid took 281 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 90 ms :[(NOT p1), (NOT p1)]

Stuttering acceptance computed with spot in 89 ms :[(NOT p1), (NOT p1)]

// Phase 1: matrix 84 rows 48 cols

[2024-06-01 15:49:27] [INFO ] Computed 13 invariants in 1 ms

[2024-06-01 15:49:27] [INFO ] [Real]Absence check using 0 positive and 13 generalized place invariants in 13 ms returned sat

[2024-06-01 15:49:27] [INFO ] [Real]Absence check using state equation in 54 ms returned sat

[2024-06-01 15:49:27] [INFO ] Solution in real domain found non-integer solution.

[2024-06-01 15:49:27] [INFO ] [Nat]Absence check using 0 positive and 13 generalized place invariants in 11 ms returned sat

[2024-06-01 15:49:27] [INFO ] [Nat]Absence check using state equation in 52 ms returned sat

[2024-06-01 15:49:27] [INFO ] Computed and/alt/rep : 18/93/18 causal constraints (skipped 62 transitions) in 13 ms.

[2024-06-01 15:49:27] [INFO ] Added : 14 causal constraints over 3 iterations in 73 ms. Result :sat

Could not prove EG (NOT p1)

Support contains 3 out of 48 places. Attempting structural reductions.

Property had overlarge support with respect to TGBA, discarding it for now.

Starting structural reductions in SI_LTL mode, iteration 0 : 48/48 places, 84/84 transitions.

Graph (complete) has 207 edges and 48 vertex of which 12 are kept as prefixes of interest. Removing 36 places using SCC suffix rule.1 ms

Discarding 36 places :

Also discarding 68 output transitions

Drop transitions (Output transitions of discarded places.) removed 68 transitions

Discarding 2 places :

Symmetric choice reduction at 0 with 2 rule applications. Total rules 3 place count 10 transition count 10

Ensure Unique test removed 1 places

Iterating global reduction 0 with 3 rules applied. Total rules applied 6 place count 9 transition count 10

Applied a total of 6 rules in 5 ms. Remains 9 /48 variables (removed 39) and now considering 10/84 (removed 74) transitions.

// Phase 1: matrix 10 rows 9 cols

[2024-06-01 15:49:27] [INFO ] Computed 3 invariants in 1 ms

[2024-06-01 15:49:28] [INFO ] Implicit Places using invariants in 39 ms returned [8]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 41 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 8/48 places, 10/84 transitions.

Reduce places removed 1 places and 1 transitions.

Applied a total of 0 rules in 2 ms. Remains 7 /8 variables (removed 1) and now considering 9/10 (removed 1) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 48 ms. Remains : 7/48 places, 9/84 transitions.

Computed a total of 7 stabilizing places and 9 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 7 transition count 9

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p1), (X p1), (F (G (NOT p1)))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1))]

Property proved to be true thanks to knowledge (Minato strategy)

Knowledge based reduction with 3 factoid took 28 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-08 TRUE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-08 finished in 2080 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(X(F(p0)))))'

Support contains 6 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 24 places :

Symmetric choice reduction at 0 with 24 rule applications. Total rules 24 place count 80 transition count 352

Iterating global reduction 0 with 24 rules applied. Total rules applied 48 place count 80 transition count 352

Discarding 20 places :

Symmetric choice reduction at 0 with 20 rule applications. Total rules 68 place count 60 transition count 136

Iterating global reduction 0 with 20 rules applied. Total rules applied 88 place count 60 transition count 136

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 89 place count 59 transition count 128

Iterating global reduction 0 with 1 rules applied. Total rules applied 90 place count 59 transition count 128

Applied a total of 90 rules in 9 ms. Remains 59 /104 variables (removed 45) and now considering 128/592 (removed 464) transitions.

// Phase 1: matrix 128 rows 59 cols

[2024-06-01 15:49:28] [INFO ] Computed 16 invariants in 1 ms

[2024-06-01 15:49:28] [INFO ] Implicit Places using invariants in 89 ms returned [7]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 91 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 58/104 places, 128/592 transitions.

Applied a total of 0 rules in 1 ms. Remains 58 /58 variables (removed 0) and now considering 128/128 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 101 ms. Remains : 58/104 places, 128/592 transitions.

Stuttering acceptance computed with spot in 182 ms :[(NOT p0), (NOT p0), (NOT p0), (NOT p0)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-10

Stuttering criterion allowed to conclude after 3473 steps with 9 reset in 35 ms.

FORMULA PermAdmissibility-PT-50-LTLFireability-10 FALSE TECHNIQUES STUTTER_TEST

Treatment of property PermAdmissibility-PT-50-LTLFireability-10 finished in 334 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F((G(F(p0))||G(p1))))'

Support contains 4 out of 104 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 23 places :

Symmetric choice reduction at 0 with 23 rule applications. Total rules 23 place count 81 transition count 356

Iterating global reduction 0 with 23 rules applied. Total rules applied 46 place count 81 transition count 356

Discarding 18 places :

Symmetric choice reduction at 0 with 18 rule applications. Total rules 64 place count 63 transition count 158

Iterating global reduction 0 with 18 rules applied. Total rules applied 82 place count 63 transition count 158

Discarding 2 places :

Symmetric choice reduction at 0 with 2 rule applications. Total rules 84 place count 61 transition count 142

Iterating global reduction 0 with 2 rules applied. Total rules applied 86 place count 61 transition count 142

Applied a total of 86 rules in 28 ms. Remains 61 /104 variables (removed 43) and now considering 142/592 (removed 450) transitions.

// Phase 1: matrix 142 rows 61 cols

[2024-06-01 15:49:28] [INFO ] Computed 16 invariants in 2 ms

[2024-06-01 15:49:28] [INFO ] Implicit Places using invariants in 152 ms returned [8]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 154 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 60/104 places, 142/592 transitions.

Applied a total of 0 rules in 7 ms. Remains 60 /60 variables (removed 0) and now considering 142/142 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 189 ms. Remains : 60/104 places, 142/592 transitions.

Stuttering acceptance computed with spot in 87 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-11

Product exploration explored 100000 steps with 666 reset in 1087 ms.

Product exploration explored 100000 steps with 659 reset in 848 ms.

Computed a total of 60 stabilizing places and 142 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 60 transition count 142

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p1) (NOT p0)), (X (NOT (AND p1 (NOT p0)))), (X (NOT p0)), (X (AND (NOT p1) (NOT p0))), (X (NOT p1)), (X (X (NOT (AND p1 (NOT p0))))), (X (X (NOT p0))), (X (X (AND (NOT p1) (NOT p0)))), (X (X (NOT p1))), (F (G (NOT p1))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 11 factoid took 332 ms. Reduced automaton from 2 states, 4 edges and 2 AP (stutter insensitive) to 2 states, 4 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 83 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

RANDOM walk for 21888 steps (25 resets) in 53 ms. (405 steps per ms) remains 0/4 properties

Knowledge obtained : [(AND (NOT p1) (NOT p0)), (X (NOT (AND p1 (NOT p0)))), (X (NOT p0)), (X (AND (NOT p1) (NOT p0))), (X (NOT p1)), (X (X (NOT (AND p1 (NOT p0))))), (X (X (NOT p0))), (X (X (AND (NOT p1) (NOT p0)))), (X (X (NOT p1))), (F (G (NOT p1))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p1), (F (NOT (OR (NOT p1) p0))), (F p0), (F (NOT (AND (NOT p1) (NOT p0))))]

Property proved to be false thanks to negative knowledge :(F p1)

Knowledge based reduction with 11 factoid took 414 ms. Reduced automaton from 2 states, 4 edges and 2 AP (stutter insensitive) to 1 states, 1 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-11 FALSE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-11 finished in 3170 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(((p0||X((!p1||X(F(!p2))))) U p3)))'

Support contains 11 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 22 places :

Symmetric choice reduction at 0 with 22 rule applications. Total rules 22 place count 82 transition count 364

Iterating global reduction 0 with 22 rules applied. Total rules applied 44 place count 82 transition count 364

Discarding 14 places :

Symmetric choice reduction at 0 with 14 rule applications. Total rules 58 place count 68 transition count 190

Iterating global reduction 0 with 14 rules applied. Total rules applied 72 place count 68 transition count 190

Applied a total of 72 rules in 7 ms. Remains 68 /104 variables (removed 36) and now considering 190/592 (removed 402) transitions.

// Phase 1: matrix 190 rows 68 cols

[2024-06-01 15:49:31] [INFO ] Computed 16 invariants in 3 ms

[2024-06-01 15:49:31] [INFO ] Implicit Places using invariants in 171 ms returned [9]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 174 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 67/104 places, 190/592 transitions.

Applied a total of 0 rules in 1 ms. Remains 67 /67 variables (removed 0) and now considering 190/190 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 182 ms. Remains : 67/104 places, 190/592 transitions.

Stuttering acceptance computed with spot in 244 ms :[(NOT p3), (AND p1 p2), (NOT p3), p2]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-12

Product exploration explored 100000 steps with 28622 reset in 326 ms.

Product exploration explored 100000 steps with 28655 reset in 402 ms.

Computed a total of 67 stabilizing places and 190 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 67 transition count 190

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p3) (NOT p0) (NOT p1) (NOT p2)), (X (NOT p3)), (X (AND (NOT p3) (NOT p0))), (X (NOT p0)), (X (NOT p1)), (X (X (NOT p2))), (X (X (NOT p3))), (X (X (AND (NOT p3) (NOT p0)))), (X (X (NOT p0))), (X (X (NOT p1))), (F (G (NOT p3))), (F (G (NOT p0))), (F (G (NOT p1))), (F (G (NOT p2)))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 14 factoid took 191 ms. Reduced automaton from 4 states, 7 edges and 4 AP (stutter sensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 101 ms :[(NOT p3), (NOT p3)]

RANDOM walk for 7492 steps (6 resets) in 11 ms. (624 steps per ms) remains 0/1 properties

Knowledge obtained : [(AND (NOT p3) (NOT p0) (NOT p1) (NOT p2)), (X (NOT p3)), (X (AND (NOT p3) (NOT p0))), (X (NOT p0)), (X (NOT p1)), (X (X (NOT p2))), (X (X (NOT p3))), (X (X (AND (NOT p3) (NOT p0)))), (X (X (NOT p0))), (X (X (NOT p1))), (F (G (NOT p3))), (F (G (NOT p0))), (F (G (NOT p1))), (F (G (NOT p2)))]

False Knowledge obtained : [(F p3)]

Property proved to be false thanks to negative knowledge :(F p3)

Knowledge based reduction with 14 factoid took 183 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-12 FALSE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-12 finished in 1806 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G((F(G(!p0)) U (p1||G(p2)))))'

Support contains 11 out of 104 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Graph (complete) has 975 edges and 104 vertex of which 86 are kept as prefixes of interest. Removing 18 places using SCC suffix rule.5 ms

Discarding 18 places :

Also discarding 128 output transitions

Drop transitions (Output transitions of discarded places.) removed 128 transitions

Discarding 9 places :

Symmetric choice reduction at 0 with 9 rule applications. Total rules 10 place count 77 transition count 360

Iterating global reduction 0 with 9 rules applied. Total rules applied 19 place count 77 transition count 360

Discarding 16 places :

Symmetric choice reduction at 0 with 16 rule applications. Total rules 35 place count 61 transition count 168

Iterating global reduction 0 with 16 rules applied. Total rules applied 51 place count 61 transition count 168

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 52 place count 60 transition count 160

Iterating global reduction 0 with 1 rules applied. Total rules applied 53 place count 60 transition count 160

Applied a total of 53 rules in 26 ms. Remains 60 /104 variables (removed 44) and now considering 160/592 (removed 432) transitions.

// Phase 1: matrix 160 rows 60 cols

[2024-06-01 15:49:33] [INFO ] Computed 14 invariants in 2 ms

[2024-06-01 15:49:33] [INFO ] Implicit Places using invariants in 170 ms returned []

[2024-06-01 15:49:33] [INFO ] Invariant cache hit.

[2024-06-01 15:49:33] [INFO ] Implicit Places using invariants and state equation in 241 ms returned []

Implicit Place search using SMT with State Equation took 425 ms to find 0 implicit places.

[2024-06-01 15:49:33] [INFO ] Redundant transitions in 10 ms returned []

Running 156 sub problems to find dead transitions.

[2024-06-01 15:49:33] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/59 variables, 10/10 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/59 variables, 0/10 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 2 (OVERLAPS) 1/60 variables, 4/14 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/60 variables, 0/14 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 4 (OVERLAPS) 160/220 variables, 60/74 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/220 variables, 0/74 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 6 (OVERLAPS) 0/220 variables, 0/74 constraints. Problems are: Problem set: 0 solved, 156 unsolved

No progress, stopping.

After SMT solving in domain Real declared 220/220 variables, and 74 constraints, problems are : Problem set: 0 solved, 156 unsolved in 5410 ms.

Refiners :[Generalized P Invariants (flows): 14/14 constraints, State Equation: 60/60 constraints, PredecessorRefiner: 156/156 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 156 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/59 variables, 10/10 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/59 variables, 0/10 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 2 (OVERLAPS) 1/60 variables, 4/14 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/60 variables, 0/14 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 4 (OVERLAPS) 160/220 variables, 60/74 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/220 variables, 156/230 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/220 variables, 0/230 constraints. Problems are: Problem set: 0 solved, 156 unsolved

At refinement iteration 7 (OVERLAPS) 0/220 variables, 0/230 constraints. Problems are: Problem set: 0 solved, 156 unsolved

No progress, stopping.

After SMT solving in domain Int declared 220/220 variables, and 230 constraints, problems are : Problem set: 0 solved, 156 unsolved in 10091 ms.

Refiners :[Generalized P Invariants (flows): 14/14 constraints, State Equation: 60/60 constraints, PredecessorRefiner: 156/156 constraints, Known Traps: 0/0 constraints]

After SMT, in 15717ms problems are : Problem set: 0 solved, 156 unsolved

Search for dead transitions found 0 dead transitions in 15721ms

Starting structural reductions in SI_LTL mode, iteration 1 : 60/104 places, 160/592 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 16197 ms. Remains : 60/104 places, 160/592 transitions.

Stuttering acceptance computed with spot in 195 ms :[(AND (NOT p1) (NOT p2)), p0, (AND (NOT p1) (NOT p2)), (AND p0 (NOT p2))]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-13

Product exploration explored 100000 steps with 142 reset in 1093 ms.

Product exploration explored 100000 steps with 142 reset in 776 ms.

Computed a total of 60 stabilizing places and 160 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 60 transition count 160

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p1) (NOT p2) (NOT p0)), (X (NOT p2)), (X (NOT p0)), (X (AND (NOT p1) (NOT p2))), (X (NOT (AND (NOT p1) p2))), (X (NOT p1)), (X (X (NOT p2))), (X (X (NOT p0))), (X (X (AND (NOT p1) (NOT p2)))), (X (X (NOT (AND (NOT p1) p2)))), (X (X (NOT p1))), (F (G (NOT p1))), (F (G (NOT p2))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 14 factoid took 482 ms. Reduced automaton from 4 states, 12 edges and 3 AP (stutter insensitive) to 2 states, 4 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 72 ms :[(AND (NOT p1) (NOT p2)), (AND (NOT p1) (NOT p2))]

RANDOM walk for 30320 steps (39 resets) in 35 ms. (842 steps per ms) remains 0/4 properties

Knowledge obtained : [(AND (NOT p1) (NOT p2) (NOT p0)), (X (NOT p2)), (X (NOT p0)), (X (AND (NOT p1) (NOT p2))), (X (NOT (AND (NOT p1) p2))), (X (NOT p1)), (X (X (NOT p2))), (X (X (NOT p0))), (X (X (AND (NOT p1) (NOT p2)))), (X (X (NOT (AND (NOT p1) p2)))), (X (X (NOT p1))), (F (G (NOT p1))), (F (G (NOT p2))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p1), (F p2), (F (NOT (OR p1 (NOT p2)))), (F (NOT (AND (NOT p1) (NOT p2))))]

Property proved to be false thanks to negative knowledge :(F p1)

Knowledge based reduction with 14 factoid took 570 ms. Reduced automaton from 2 states, 4 edges and 2 AP (stutter insensitive) to 1 states, 1 edges and 0 AP (stutter insensitive).

FORMULA PermAdmissibility-PT-50-LTLFireability-13 FALSE TECHNIQUES KNOWLEDGE

Treatment of property PermAdmissibility-PT-50-LTLFireability-13 finished in 19499 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((F(G(p1))&&G(p2)&&p0)))'

Support contains 9 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 23 places :

Symmetric choice reduction at 0 with 23 rule applications. Total rules 23 place count 81 transition count 356

Iterating global reduction 0 with 23 rules applied. Total rules applied 46 place count 81 transition count 356

Discarding 18 places :

Symmetric choice reduction at 0 with 18 rule applications. Total rules 64 place count 63 transition count 150

Iterating global reduction 0 with 18 rules applied. Total rules applied 82 place count 63 transition count 150

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 83 place count 62 transition count 142

Iterating global reduction 0 with 1 rules applied. Total rules applied 84 place count 62 transition count 142

Applied a total of 84 rules in 7 ms. Remains 62 /104 variables (removed 42) and now considering 142/592 (removed 450) transitions.

// Phase 1: matrix 142 rows 62 cols

[2024-06-01 15:49:52] [INFO ] Computed 16 invariants in 2 ms

[2024-06-01 15:49:53] [INFO ] Implicit Places using invariants in 104 ms returned []

[2024-06-01 15:49:53] [INFO ] Invariant cache hit.

[2024-06-01 15:49:53] [INFO ] Implicit Places using invariants and state equation in 208 ms returned []

Implicit Place search using SMT with State Equation took 314 ms to find 0 implicit places.

Running 138 sub problems to find dead transitions.

[2024-06-01 15:49:53] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/61 variables, 4/4 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/61 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 2 (OVERLAPS) 1/62 variables, 12/16 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/62 variables, 0/16 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 4 (OVERLAPS) 142/204 variables, 62/78 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/204 variables, 0/78 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 6 (OVERLAPS) 0/204 variables, 0/78 constraints. Problems are: Problem set: 0 solved, 138 unsolved

No progress, stopping.

After SMT solving in domain Real declared 204/204 variables, and 78 constraints, problems are : Problem set: 0 solved, 138 unsolved in 4351 ms.

Refiners :[Generalized P Invariants (flows): 16/16 constraints, State Equation: 62/62 constraints, PredecessorRefiner: 138/138 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 138 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/61 variables, 4/4 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/61 variables, 0/4 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 2 (OVERLAPS) 1/62 variables, 12/16 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/62 variables, 0/16 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 4 (OVERLAPS) 142/204 variables, 62/78 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 5 (INCLUDED_ONLY) 0/204 variables, 138/216 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/204 variables, 0/216 constraints. Problems are: Problem set: 0 solved, 138 unsolved

At refinement iteration 7 (OVERLAPS) 0/204 variables, 0/216 constraints. Problems are: Problem set: 0 solved, 138 unsolved

No progress, stopping.

After SMT solving in domain Int declared 204/204 variables, and 216 constraints, problems are : Problem set: 0 solved, 138 unsolved in 8071 ms.

Refiners :[Generalized P Invariants (flows): 16/16 constraints, State Equation: 62/62 constraints, PredecessorRefiner: 138/138 constraints, Known Traps: 0/0 constraints]

After SMT, in 12586ms problems are : Problem set: 0 solved, 138 unsolved

Search for dead transitions found 0 dead transitions in 12589ms

Starting structural reductions in LTL mode, iteration 1 : 62/104 places, 142/592 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 12910 ms. Remains : 62/104 places, 142/592 transitions.

Stuttering acceptance computed with spot in 245 ms :[(OR (NOT p0) (NOT p2) (NOT p1)), (OR (NOT p0) (NOT p2) (NOT p1)), true, (NOT p1), (NOT p2)]

Running random walk in product with property : PermAdmissibility-PT-50-LTLFireability-14

Entered a terminal (fully accepting) state of product in 1 steps with 0 reset in 0 ms.

FORMULA PermAdmissibility-PT-50-LTLFireability-14 FALSE TECHNIQUES STUTTER_TEST

Treatment of property PermAdmissibility-PT-50-LTLFireability-14 finished in 13184 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(((G(p0) U (!p0 U X(p1))) U p1))'

Support contains 6 out of 104 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 104/104 places, 592/592 transitions.

Discarding 26 places :

Symmetric choice reduction at 0 with 26 rule applications. Total rules 26 place count 78 transition count 344

Iterating global reduction 0 with 26 rules applied. Total rules applied 52 place count 78 transition count 344

Discarding 22 places :

Symmetric choice reduction at 0 with 22 rule applications. Total rules 74 place count 56 transition count 122

Iterating global reduction 0 with 22 rules applied. Total rules applied 96 place count 56 transition count 122

Discarding 2 places :

Symmetric choice reduction at 0 with 2 rule applications. Total rules 98 place count 54 transition count 106

Iterating global reduction 0 with 2 rules applied. Total rules applied 100 place count 54 transition count 106

Applied a total of 100 rules in 8 ms. Remains 54 /104 variables (removed 50) and now considering 106/592 (removed 486) transitions.

// Phase 1: matrix 106 rows 54 cols

[2024-06-01 15:50:06] [INFO ] Computed 16 invariants in 1 ms

[2024-06-01 15:50:06] [INFO ] Implicit Places using invariants in 127 ms returned [0, 5, 18, 26]

[2024-06-01 15:50:06] [INFO ] Actually due to overlaps returned [0, 5, 18]

Discarding 3 places :

Implicit Place search using SMT only with invariants took 131 ms to find 3 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 51/104 places, 106/592 transitions.

Applied a total of 0 rules in 1 ms. Remains 51 /51 variables (removed 0) and now considering 106/106 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 141 ms. Remains : 51/104 places, 106/592 transitions.