About the Execution of LTSMin+red for Echo-PT-d03r05

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 2467.104 | 3600000.00 | 6038752.00 | 9799.00 | FF???TFTTFFFT?TF | normal |

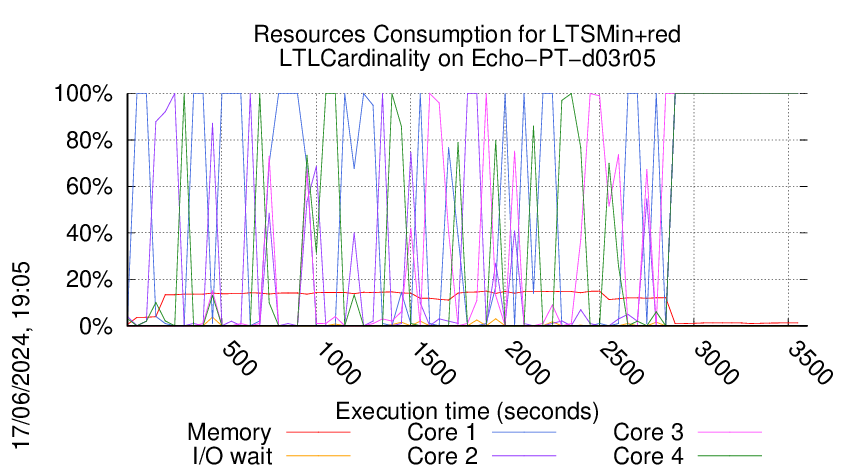

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r492-smll-171636266200115.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool ltsminxred

Input is Echo-PT-d03r05, examination is LTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r492-smll-171636266200115

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.2M

-rw-r--r-- 1 mcc users 5.7K May 14 13:22 CTLCardinality.txt

-rw-r--r-- 1 mcc users 55K May 14 13:22 CTLCardinality.xml

-rw-r--r-- 1 mcc users 4.6K May 14 13:22 CTLFireability.txt

-rw-r--r-- 1 mcc users 39K May 14 13:22 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:42 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K May 18 16:42 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.8K May 19 07:09 LTLCardinality.txt

-rw-r--r-- 1 mcc users 27K May 19 15:51 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K May 19 07:17 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K May 19 18:17 LTLFireability.xml

-rw-r--r-- 1 mcc users 15K Apr 12 04:45 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 160K Apr 12 04:45 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 7.1K Apr 12 04:44 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 59K Apr 12 04:44 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Apr 22 14:43 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Apr 22 14:43 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 18 16:42 equiv_col

-rw-r--r-- 1 mcc users 7 May 18 16:42 instance

-rw-r--r-- 1 mcc users 6 May 18 16:42 iscolored

-rw-r--r-- 1 mcc users 716K May 18 16:42 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-00

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-01

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-02

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-03

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-04

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-05

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-06

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-07

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-08

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-09

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-10

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-11

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-12

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-13

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-14

FORMULA_NAME Echo-PT-d03r05-LTLCardinality-15

=== Now, execution of the tool begins

BK_START 1717205142116

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=LTLCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=Echo-PT-d03r05

BK_MEMORY_CONFINEMENT=16384

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202405141337

[2024-06-01 01:25:44] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLCardinality, -timeout, 360, -rebuildPNML]

[2024-06-01 01:25:44] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-06-01 01:25:44] [INFO ] Load time of PNML (sax parser for PT used): 464 ms

[2024-06-01 01:25:44] [INFO ] Transformed 1445 places.

[2024-06-01 01:25:44] [INFO ] Transformed 1190 transitions.

[2024-06-01 01:25:44] [INFO ] Found NUPN structural information;

[2024-06-01 01:25:44] [INFO ] Parsed PT model containing 1445 places and 1190 transitions and 8260 arcs in 737 ms.

Parsed 16 properties from file /home/mcc/execution/LTLCardinality.xml in 106 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 3 formulas.

Initial state reduction rules removed 1 formulas.

FORMULA Echo-PT-d03r05-LTLCardinality-07 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-10 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-14 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-15 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-05 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-06 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Echo-PT-d03r05-LTLCardinality-12 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 34 out of 1445 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1445/1445 places, 1190/1190 transitions.

Reduce places removed 124 places and 0 transitions.

Iterating post reduction 0 with 124 rules applied. Total rules applied 124 place count 1321 transition count 1190

Applied a total of 124 rules in 255 ms. Remains 1321 /1445 variables (removed 124) and now considering 1190/1190 (removed 0) transitions.

// Phase 1: matrix 1190 rows 1321 cols

[2024-06-01 01:25:48] [INFO ] Computed 601 invariants in 2360 ms

[2024-06-01 01:26:33] [INFO ] Performed 619/1321 implicitness test of which 0 returned IMPLICIT in 40 seconds.

[2024-06-01 01:27:09] [INFO ] Performed 678/1321 implicitness test of which 0 returned IMPLICIT in 76 seconds.

[2024-06-01 01:27:42] [INFO ] Performed 708/1321 implicitness test of which 0 returned IMPLICIT in 109 seconds.

[2024-06-01 01:28:06] [INFO ] Implicit Places using invariants in 141081 ms returned []

[2024-06-01 01:28:06] [INFO ] Invariant cache hit.

[2024-06-01 01:28:20] [INFO ] Implicit Places using invariants and state equation in 13431 ms returned []

Implicit Place search using SMT with State Equation took 154685 ms to find 0 implicit places.

Running 1189 sub problems to find dead transitions.

[2024-06-01 01:28:20] [INFO ] Invariant cache hit.

Error getting values : (error "ParserException while parsing response: (timeout

org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 0 (INCLUDED_ONLY) 0/1319 variables, 1319/1319 constraints. Problems are: Problem set: 0 solved, 1189 unsolved

SMT process timed out in 31604ms, After SMT, problems are : Problem set: 0 solved, 1189 unsolved

Search for dead transitions found 0 dead transitions in 31673ms

Starting structural reductions in LTL mode, iteration 1 : 1321/1445 places, 1190/1190 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 186674 ms. Remains : 1321/1445 places, 1190/1190 transitions.

Support contains 34 out of 1321 places after structural reductions.

[2024-06-01 01:28:52] [INFO ] Flatten gal took : 366 ms

[2024-06-01 01:28:53] [INFO ] Flatten gal took : 163 ms

[2024-06-01 01:28:53] [INFO ] Input system was already deterministic with 1190 transitions.

Reduction of identical properties reduced properties to check from 20 to 18

RANDOM walk for 6182 steps (23 resets) in 1003 ms. (6 steps per ms) remains 0/18 properties

FORMULA Echo-PT-d03r05-LTLCardinality-09 FALSE TECHNIQUES REACHABILITY_KNOWLEDGE

Computed a total of 1321 stabilizing places and 1190 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1321 transition count 1190

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(p0))'

Support contains 2 out of 1321 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1321/1321 places, 1190/1190 transitions.

Graph (complete) has 4733 edges and 1321 vertex of which 1313 are kept as prefixes of interest. Removing 8 places using SCC suffix rule.16 ms

Discarding 8 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Reduce places removed 1 places and 1 transitions.

Applied a total of 1 rules in 175 ms. Remains 1312 /1321 variables (removed 9) and now considering 1188/1190 (removed 2) transitions.

// Phase 1: matrix 1188 rows 1312 cols

[2024-06-01 01:28:56] [INFO ] Computed 594 invariants in 2156 ms

[2024-06-01 01:29:43] [INFO ] Performed 605/1312 implicitness test of which 0 returned IMPLICIT in 41 seconds.

[2024-06-01 01:30:09] [INFO ] Implicit Places using invariants in 75699 ms returned [615, 716, 737, 742, 763, 864]

Discarding 6 places :

Implicit Place search using SMT only with invariants took 75709 ms to find 6 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 1306/1321 places, 1188/1190 transitions.

Applied a total of 0 rules in 85 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 75971 ms. Remains : 1306/1321 places, 1188/1190 transitions.

Stuttering acceptance computed with spot in 247 ms :[(NOT p0)]

Running random walk in product with property : Echo-PT-d03r05-LTLCardinality-00

Stuttering criterion allowed to conclude after 20690 steps with 474 reset in 527 ms.

FORMULA Echo-PT-d03r05-LTLCardinality-00 FALSE TECHNIQUES STUTTER_TEST

Treatment of property Echo-PT-d03r05-LTLCardinality-00 finished in 76827 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((p0&&F((p1&&X(p0))))))'

Support contains 3 out of 1321 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1321/1321 places, 1190/1190 transitions.

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 1320 transition count 1190

Applied a total of 1 rules in 35 ms. Remains 1320 /1321 variables (removed 1) and now considering 1190/1190 (removed 0) transitions.

// Phase 1: matrix 1190 rows 1320 cols

[2024-06-01 01:30:13] [INFO ] Computed 600 invariants in 2279 ms

[2024-06-01 01:30:56] [INFO ] Performed 493/1320 implicitness test of which 0 returned IMPLICIT in 38 seconds.

[2024-06-01 01:31:34] [INFO ] Performed 599/1320 implicitness test of which 0 returned IMPLICIT in 76 seconds.

[2024-06-01 01:32:07] [INFO ] Performed 610/1320 implicitness test of which 0 returned IMPLICIT in 109 seconds.

[2024-06-01 01:32:44] [INFO ] Performed 706/1320 implicitness test of which 0 returned IMPLICIT in 145 seconds.

[2024-06-01 01:32:44] [INFO ] Timeout of Implicit test with SMT after 145 seconds.

[2024-06-01 01:32:44] [INFO ] Implicit Places using invariants in 153351 ms returned []

[2024-06-01 01:32:44] [INFO ] Invariant cache hit.

[2024-06-01 01:33:13] [INFO ] Implicit Places using invariants and state equation in 28911 ms returned []

Implicit Place search using SMT with State Equation took 182267 ms to find 0 implicit places.

Running 1189 sub problems to find dead transitions.

[2024-06-01 01:33:13] [INFO ] Invariant cache hit.

Error getting values : (error "ParserException while parsing response: ((s0 1.0)

(s1 1.0)

(s2 1.0)

(s3 1.0)

(s4 1.0)

(s5 1.0)

(s6 1.0)

(s7 1.0)

(s8 1.0)

(s9 1.0)

(s10 1.0)

(s11 1.0)

(s12 1.0)

(s13 1.0)

(s14 1.0)

(s15 1.0)

(s16 1.0)

(s17 1.0)

(s18 1.0)

(s19 1.0)

(s20 1.0)

(s21 1.0)

(s22 1.0)

(s23 1.0)

(s24 1.0)

(s25 1.0)

(s26 1.0)

(s27 1.0)

(s28 1.0)

(s29 1.0)

(s30 1.0)

(s31 1.0)

(s32 1.0)

(s33 1.0)

(s34 1.0)

(s35 1.0)

(s36 1.0)

(s37 1.0)

(s38 1.0)

(s39 1.0)

(s40 1.0)

(s41 1.0)

(s42 1.0)

(s43 1.0)

(s44 1.0)

(s45 1.0)

(s46 1.0)

(s47 1.0)

(s48 1.0)

(s49 1.0)

(s50 1.0)

(s51 1.0)

(s52 1.0)

(s53 1.0)

(s54 1.0)

(s55 1.0)

(s56 1.0)

(s57 1.0)

(s58 1.0)

(s59 1.0)

(s60 1.0)

(s61 1.0)

(s62 1.0)

(s63 1.0)

(s64 1.0)

(s65 1.0)

(s66 1.0)

(s67 1.0)

(s68 1.0)

(s69 1.0)

(s70 1.0)

(s71 1.0)

(s72 1.0)

(s73 1.0)

(s74 1.0)

(s75 1.0)

(s76 1.0)

(s77 1.0)

(s78 1.0)

(s79 1.0)

(s80 1.0)

(s81 1.0)

(s82 1.0)

(s83 1.0)

(s84 1.0)

(s85 1.0)

(s86 1.0)

(s87 1.0)

(s88 1.0)

(s89 1.0)

(s90 1.0)

(s91 1.0)

(s92 1.0)

(s93 1.0)

(s94 1.0)

(s95 1.0)

(s96 1.0)

(s97 1.0)

(s98 1.0)

(s99 1.0)

(s100 1.0)

(s101 timeout

org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 0 (INCLUDED_ONLY) 0/1319 variables, 1319/1319 constraints. Problems are: Problem set: 0 solved, 1189 unsolved

SMT process timed out in 30983ms, After SMT, problems are : Problem set: 0 solved, 1189 unsolved

Search for dead transitions found 0 dead transitions in 31003ms

Starting structural reductions in LTL mode, iteration 1 : 1320/1321 places, 1190/1190 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 213313 ms. Remains : 1320/1321 places, 1190/1190 transitions.

Stuttering acceptance computed with spot in 209 ms :[(NOT p0), (OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p1) (NOT p0)), true]

Running random walk in product with property : Echo-PT-d03r05-LTLCardinality-01

Stuttering criterion allowed to conclude after 250 steps with 0 reset in 16 ms.

FORMULA Echo-PT-d03r05-LTLCardinality-01 FALSE TECHNIQUES STUTTER_TEST

Treatment of property Echo-PT-d03r05-LTLCardinality-01 finished in 213574 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(X(G((X(X(p0)) U p1))))))'

Support contains 4 out of 1321 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1321/1321 places, 1190/1190 transitions.

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 1320 transition count 1190

Applied a total of 1 rules in 43 ms. Remains 1320 /1321 variables (removed 1) and now considering 1190/1190 (removed 0) transitions.

[2024-06-01 01:33:44] [INFO ] Invariant cache hit.

[2024-06-01 01:34:31] [INFO ] Performed 586/1320 implicitness test of which 0 returned IMPLICIT in 41 seconds.

[2024-06-01 01:35:04] [INFO ] Performed 610/1320 implicitness test of which 0 returned IMPLICIT in 74 seconds.

[2024-06-01 01:35:44] [INFO ] Performed 756/1320 implicitness test of which 0 returned IMPLICIT in 114 seconds.

[2024-06-01 01:36:08] [INFO ] Implicit Places using invariants in 143787 ms returned []

[2024-06-01 01:36:08] [INFO ] Invariant cache hit.

[2024-06-01 01:36:34] [INFO ] Implicit Places using invariants and state equation in 26739 ms returned []

Implicit Place search using SMT with State Equation took 170532 ms to find 0 implicit places.

Running 1189 sub problems to find dead transitions.

[2024-06-01 01:36:35] [INFO ] Invariant cache hit.

Error getting values : (error "ParserException while parsing response: ((s0 1.0)

(s1 1.0)

(s2 1.0)

(s3 1.0)

(s4 1.0)

(s5 1.0)

(s6 1.0)

(s7 1.0)

(s8 1.0)

(s9 1.0)

(s10 1.0)

(s11 1.0)

(s12 1.0)

(s13 1.0)

(s14 1.0)

(s15 1.0)

(s16 1.0)

(s17 1.0)

(s18 1.0)

(s19 1.0)

(s20 1.0)

(s21 1.0)

(s22 1.0)

(s23 1.0)

(s24 1.0)

(s25 1.0)

(s26 1.0)

(s27 1.0)

(s28 1.0)

(s29 1.0)

(s30 1.0)

(s31 1.0)

(s32 1.0)

(s33 1.0)

(s34 1.0)

(s35 1.0)

(s36 1.0)

(s37 1.0)

(s38 1.0)

(s39 1.0)

(s40 1.0)

(s41 1.0)

(s42 1.0)

(s43 1.0)

(s44 1.0)

(s45 1.0)

(s46 1.0)

(s47 1.0)

(s48 1.0)

(s49 1.0)

(s50 1.0)

(s51 1.0)

(s52 1.0)

(s53 1.0)

(s54 1.0)

(s55 1.0)

(s56 1.0)

(s57 1.0)

(s58 1.0)

(s59 1.0)

(s60 1.0)

(s61 1.0)

(s62 1.0)

(s63 1.0)

(s64 1.0)

(s65 1.0)

(s66 1.0)

(s67 1.0)

(s68 1.0)

(s69 1.0)

(s70 1.0)

(s71 1.0)

(s72 1.0)

(s73 1.0)

(s74 1.0)

(s75 1.0)

(s76 1.0)

(s77 1.0)

(s78 1.0)

(s79 1.0)

(s80 1.0)

(s81 1.0)

(s82 1.0)

(s83 1.0)

(s84 1.0)

(s85 1.0)

(s86 1.0)

(s87 1.0)

(s88 1.0)

(s89 1.0)

(s90 1.0)

(s91 1.0)

(s92 1.0)

(s93 1.0)

(s94 1.0)

(s95 1.0)

(s96 1.0)

(s97 1.0)

(s98 1.0)

(s99 1.0)

(s100 1.0)

(s101 1.0)

(s102 1.0)

(s103 1.0)

(s104 1.0)

(s105 1.0)

(s106 1.0)

(s107 1.0)

(s108 1.0)

(s109 1.0)

(s110 1.0)

(s111 1.0)

(s112 1.0)

(s113 1.0)

(s114 1.0)

(s115 1.0)

(s116 1.0)

(s117 1.0)

(s118 1.0)

(s119 1.0)

(s120 1.0)

(s121 1.0)

(s122 1.0)

(s123 1.0)

(s124 1.0)

(s125 1.0)

(s126 1.0)

(s127 1.0)

(s128 1.0)

(s129 1.0)

(s130 1.0)

(s131 1.0)

(s132 1.0)

(s133 1.0)

(s134 1.0)

(s135 1.0)

(s136 1.0)

(s137 1.0)

(s138 1.0)

(s139 1.0)

(s140 1.0)

(s141 1.0)

(s142 1.0)

(s143 1.0)

(s144 1.0)

(s145 1.0)

(s146 1.0)

(s147 1.0)

(s148 1.0)

(s149 1.0)

(s150 1.0)

(s151 1.0)

(s152 1.0)

(s153 1.0)

(s154 1.0)

(s155 1.0)

(s156 1.0)

(s157 1.0)

(s158 1.0)

(s159 1.0)

(s160 1.0)

(s161 1.0)

(s162 1.0)

(s163 1.0)

(s164 1.0)

(s165 1.0)

(s166 1.0)

(s167 1.0)

(s168 1.0)

(s169 1.0)

(s170 1.0)

(s171 1.0)

(s172 1.0)

(s173 1.0)

(s174 1.0)

(s175 1.0)

(s176 1.0)

(s177 1.0)

(s178 1.0)

(s179 1.0)

(s180 1.0)

(s181 1.0)

(s182 1.0)

(s183 1.0)

(s184 1.0)

(s185 1.0)

(s186 1.0)

(s187 1.0)

(s188 1.0)

(s189 1.0)

(s190 1.0)

(s191 1.0)

(s192 1.0)

(s193 1.0)

(s194 1.0)

(s195 1.0)

(s196 1.0)

(s197 1.0)

(s198 1.0)

(s199 1.0)

(s200 1.0)

(s201 1.0)

(s202 1.0)

(s203 1.0)

(s204 1.0)

(s205 1.0)

(s206 1.0)

(s207 1.0)

(s208 1.0)

(s209 1.0)

(s210 1.0)

(s211 1.0)

(s212 1.0)

(s213 1.0)

(s214 1.0)

(s215 1.0)

(s216 1.0)

(s217 1.0)

(s218 1.0)

(s219 1.0)

(s220 1.0)

(s221 1.0)

(s222 1.0)

(s223 1.0)

(s224 1.0)

(s225 1.0)

(s226 1.0)

(s227 1.0)

(s228 1.0)

(s229 1.0)

(s230 1.0)

(s231 1.0)

(s232 1.0)

(s233 1.0)

(s234 1.0)

(s235 1.0)

(s236 1.0)

(s237 1.0)

(s238 1.0)

(s239 1.0)

(s240 1.0)

(s241 1.0)

(s242 1.0)

(s243 1.0)

(s244 1.0)

(s245 1.0)

(s246 1.0)

(s247 1.0)

(s248 1.0)

(s249 1.0)

(s250 1.0)

(s251 1.0)

(s252 1.0)

(s253 1.0)

(s254 1.0)

(s255 1.0)

(s256 1.0)

(s257 1.0)

(s258 1.0)

(s259 1.0)

(s260 1.0)

(s261 1.0)

(s262 1.0)

(s263 1.0)

(s264 1.0)

(s265 1.0)

(s266 1.0)

(s267 1.0)

(s268 1.0)

(s269 1.0)

(s270 1.0)

(s271 1.0)

(s272 1.0)

(s273 1.0)

(s274 1.0)

(s275 1.0)

(s276 1.0)

(s277 1.0)

(s278 1.0)

(s279 1.0)

(s280 1.0)

(s281 1.0)

(s282 1.0)

(s283 1.0)

(s284 1.0)

(s285 1.0)

(s286 1.0)

(s287 1.0)

(s288 1.0)

(s289 1.0)

(s290 1.0)

(s291 1.0)

(s292 1.0)

(s293 1.0)

(s294 1.0)

(s295 1.0)

(s296 1.0)

(s297 1.0)

(s298 1.0)

(s299 1.0)

(s300 1.0)

(s301 1.0)

(s302 1.0)

(s303 1.0)

(s304 1.0)

(s305 1.0)

(s306 1.0)

(s307 1.0)

(s308 1.0)

(s309 1.0)

(s310 1.0)

(s311 1.0)

(s312 1.0)

(s313 1.0)

(s314 1.0)

(s315 1.0)

(s316 1.0)

(s317 1.0)

(s318 1.0)

(s319 1.0)

(s320 1.0)

(s321 1.0)

(s322 1.0)

(s323 1.0)

(s324 1.0)

(s325 1.0)

(s327 1.0)

(s328 1.0)

(s329 1.0)

(s330 1.0)

(s331 1.0)

(s332 1.0)

(s333 1.0)

(s334 1.0)

(s335 1.0)

(s336 1.0)

(s337 1.0)

(s338 1.0)

(s339 1.0)

(s340 1.0)

(s341 1.0)

(s342 1.0)

(s343 1.0)

(s344 1.0)

(s345 1.0)

(s346 1.0)

(s347 1.0)

(s348 1.0)

(s349 1.0)

(s350 1.0)

(s351 1.0)

(s352 1.0)

(s353 1.0)

(s354 1.0)

(s355 1.0)

(s356 1.0)

(s357 1.0)

(s358 1.0)

(s359 1.0)

(s360 1.0)

(s361 1.0)

(s362 1.0)

(s363 1.0)

(s364 1.0)

(s365 1.0)

(s366 1.0)

(s367 1.0)

(s368 1.0)

(s369 1.0)

(s370 1.0)

(s371 1.0)

(s372 1.0)

(s373 1.0)

(s374 1.0)

(s375 1.0)

(s376 1.0)

(s377 1.0)

(s378 1.0)

(s379 1.0)

(s380 1.0)

(s381 1.0)

(s382 1.0)

(s383 1.0)

(s384 1.0)

(s385 1.0)

(s386 1.0)timeout

org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 0 (INCLUDED_ONLY) 0/1319 variables, 1319/1319 constraints. Problems are: Problem set: 0 solved, 1189 unsolved

SMT process timed out in 30709ms, After SMT, problems are : Problem set: 0 solved, 1189 unsolved

Search for dead transitions found 0 dead transitions in 30725ms

Starting structural reductions in LTL mode, iteration 1 : 1320/1321 places, 1190/1190 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 201303 ms. Remains : 1320/1321 places, 1190/1190 transitions.

Stuttering acceptance computed with spot in 138 ms :[(NOT p1), (NOT p1), (AND (NOT p1) (NOT p0))]

Running random walk in product with property : Echo-PT-d03r05-LTLCardinality-02

Product exploration explored 100000 steps with 439 reset in 1611 ms.

Product exploration explored 100000 steps with 462 reset in 1819 ms.

Computed a total of 1320 stabilizing places and 1190 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1320 transition count 1190

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p1 p0), (X p1), (X (X p0)), (X (X (NOT (AND (NOT p1) (NOT p0))))), (X (X p1)), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 7 factoid took 210 ms. Reduced automaton from 3 states, 6 edges and 2 AP (stutter sensitive) to 3 states, 10 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 158 ms :[(NOT p1), (NOT p1), (AND (NOT p1) (NOT p0))]

Reduction of identical properties reduced properties to check from 7 to 6

RANDOM walk for 4983 steps (19 resets) in 233 ms. (21 steps per ms) remains 0/6 properties

Knowledge obtained : [(AND p1 p0), (X p1), (X (X p0)), (X (X (NOT (AND (NOT p1) (NOT p0))))), (X (X p1)), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : [(F (NOT p0)), (F (NOT (OR p1 p0))), (F (NOT (OR p1 (NOT p0)))), (F (NOT p1)), (F (NOT (OR p1 p0))), (F (NOT (AND p1 p0))), (F (NOT (OR (NOT p1) p0)))]

Knowledge based reduction with 7 factoid took 686 ms. Reduced automaton from 3 states, 10 edges and 2 AP (stutter insensitive) to 3 states, 10 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 129 ms :[(NOT p1), (NOT p1), (AND (NOT p1) (NOT p0))]

Stuttering acceptance computed with spot in 131 ms :[(NOT p1), (NOT p1), (AND (NOT p1) (NOT p0))]

Support contains 4 out of 1320 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1320/1320 places, 1190/1190 transitions.

Graph (complete) has 4723 edges and 1320 vertex of which 1313 are kept as prefixes of interest. Removing 7 places using SCC suffix rule.12 ms

Discarding 7 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Reduce places removed 1 places and 1 transitions.

Applied a total of 1 rules in 114 ms. Remains 1312 /1320 variables (removed 8) and now considering 1188/1190 (removed 2) transitions.

// Phase 1: matrix 1188 rows 1312 cols

[2024-06-01 01:37:13] [INFO ] Computed 594 invariants in 1883 ms

[2024-06-01 01:38:00] [INFO ] Performed 594/1312 implicitness test of which 0 returned IMPLICIT in 41 seconds.

[2024-06-01 01:38:09] [INFO ] Implicit Places using invariants in 58101 ms returned [615, 716, 737, 742, 763, 864]

Discarding 6 places :

Implicit Place search using SMT only with invariants took 58149 ms to find 6 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 1306/1320 places, 1188/1190 transitions.

Applied a total of 0 rules in 61 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 58324 ms. Remains : 1306/1320 places, 1188/1190 transitions.

Computed a total of 1306 stabilizing places and 1188 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1306 transition count 1188

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p1 p0), (X (OR p1 p0)), (X (NOT (AND p1 (NOT p0)))), (X (AND p1 p0)), (X (NOT (AND (NOT p1) (NOT p0)))), (X p0), (X p1), (X (NOT (AND (NOT p1) p0))), (X (X (OR p1 p0))), (X (X (NOT (AND (NOT p1) (NOT p0))))), (X (X p1)), (X (X (NOT (AND (NOT p1) p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : [(X (X (AND p1 (NOT p0)))), (X (X (NOT (AND p1 (NOT p0))))), (X (X (AND p1 p0))), (X (X (NOT (AND p1 p0)))), (X (X p0)), (X (X (NOT p0)))]

Knowledge based reduction with 14 factoid took 915 ms. Reduced automaton from 3 states, 10 edges and 2 AP (stutter insensitive) to 3 states, 10 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 127 ms :[(NOT p1), (NOT p1), (AND (NOT p0) (NOT p1))]

Reduction of identical properties reduced properties to check from 7 to 6

RANDOM walk for 6204 steps (23 resets) in 130 ms. (47 steps per ms) remains 0/6 properties

Knowledge obtained : [(AND p1 p0), (X (OR p1 p0)), (X (NOT (AND p1 (NOT p0)))), (X (AND p1 p0)), (X (NOT (AND (NOT p1) (NOT p0)))), (X p0), (X p1), (X (NOT (AND (NOT p1) p0))), (X (X (OR p1 p0))), (X (X (NOT (AND (NOT p1) (NOT p0))))), (X (X p1)), (X (X (NOT (AND (NOT p1) p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : [(X (X (AND p1 (NOT p0)))), (X (X (NOT (AND p1 (NOT p0))))), (X (X (AND p1 p0))), (X (X (NOT (AND p1 p0)))), (X (X p0)), (X (X (NOT p0))), (F (NOT (AND p0 p1))), (F (NOT (OR p0 (NOT p1)))), (F (NOT p1)), (F (NOT p0)), (F (NOT (OR p0 p1))), (F (NOT (OR (NOT p0) p1))), (F (NOT (OR p0 p1)))]

Knowledge based reduction with 14 factoid took 1751 ms. Reduced automaton from 3 states, 10 edges and 2 AP (stutter insensitive) to 3 states, 10 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 144 ms :[(NOT p1), (NOT p1), (AND (NOT p0) (NOT p1))]

Stuttering acceptance computed with spot in 134 ms :[(NOT p1), (NOT p1), (AND (NOT p0) (NOT p1))]

Stuttering acceptance computed with spot in 143 ms :[(NOT p1), (NOT p1), (AND (NOT p0) (NOT p1))]

Product exploration explored 100000 steps with 402 reset in 1568 ms.

Product exploration explored 100000 steps with 402 reset in 1724 ms.

Support contains 4 out of 1306 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1306/1306 places, 1188/1188 transitions.

Applied a total of 0 rules in 51 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

// Phase 1: matrix 1188 rows 1306 cols

[2024-06-01 01:38:19] [INFO ] Computed 588 invariants in 2123 ms

[2024-06-01 01:39:04] [INFO ] Performed 616/1306 implicitness test of which 0 returned IMPLICIT in 42 seconds.

[2024-06-01 01:39:36] [INFO ] Performed 623/1306 implicitness test of which 0 returned IMPLICIT in 74 seconds.

[2024-06-01 01:40:10] [INFO ] Performed 644/1306 implicitness test of which 0 returned IMPLICIT in 108 seconds.

[2024-06-01 01:40:52] [INFO ] Performed 1024/1306 implicitness test of which 0 returned IMPLICIT in 150 seconds.

[2024-06-01 01:40:52] [INFO ] Timeout of Implicit test with SMT after 150 seconds.

[2024-06-01 01:40:52] [INFO ] Implicit Places using invariants in 155227 ms returned []

[2024-06-01 01:40:52] [INFO ] Invariant cache hit.

[2024-06-01 01:41:00] [INFO ] Implicit Places using invariants and state equation in 7942 ms returned []

Implicit Place search using SMT with State Equation took 163173 ms to find 0 implicit places.

[2024-06-01 01:41:00] [INFO ] Redundant transitions in 107 ms returned []

Running 1182 sub problems to find dead transitions.

[2024-06-01 01:41:00] [INFO ] Invariant cache hit.

Error getting values : (error "Error writing to Z3 solver: java.io.IOException: Broken pipe")

At refinement iteration 0 (INCLUDED_ONLY) 0/1306 variables, 1306/1306 constraints. Problems are: Problem set: 0 solved, 1182 unsolved

SMT process timed out in 30718ms, After SMT, problems are : Problem set: 0 solved, 1182 unsolved

Search for dead transitions found 0 dead transitions in 30737ms

Finished structural reductions in SI_LTL mode , in 1 iterations and 194081 ms. Remains : 1306/1306 places, 1188/1188 transitions.

Treatment of property Echo-PT-d03r05-LTLCardinality-02 finished in 467566 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G((F(p0)&&F(G(p1)))))'

Support contains 4 out of 1321 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1321/1321 places, 1190/1190 transitions.

Graph (complete) has 4733 edges and 1321 vertex of which 1313 are kept as prefixes of interest. Removing 8 places using SCC suffix rule.6 ms

Discarding 8 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Reduce places removed 1 places and 1 transitions.

Applied a total of 1 rules in 89 ms. Remains 1312 /1321 variables (removed 9) and now considering 1188/1190 (removed 2) transitions.

// Phase 1: matrix 1188 rows 1312 cols

[2024-06-01 01:41:34] [INFO ] Computed 594 invariants in 2576 ms

[2024-06-01 01:42:18] [INFO ] Performed 490/1312 implicitness test of which 0 returned IMPLICIT in 38 seconds.

[2024-06-01 01:42:32] [INFO ] Implicit Places using invariants in 60559 ms returned [615, 716, 737, 742, 763, 864]

Discarding 6 places :

Implicit Place search using SMT only with invariants took 60568 ms to find 6 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 1306/1321 places, 1188/1190 transitions.

Applied a total of 0 rules in 55 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 60716 ms. Remains : 1306/1321 places, 1188/1190 transitions.

Stuttering acceptance computed with spot in 122 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Running random walk in product with property : Echo-PT-d03r05-LTLCardinality-03

Product exploration explored 100000 steps with 643 reset in 1951 ms.

Product exploration explored 100000 steps with 616 reset in 2079 ms.

Computed a total of 1306 stabilizing places and 1188 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1306 transition count 1188

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 p1), (X p0), (X p1), (X (X p0)), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 7 factoid took 232 ms. Reduced automaton from 3 states, 6 edges and 2 AP (stutter insensitive) to 3 states, 6 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 127 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

RANDOM walk for 906 steps (1 resets) in 24 ms. (36 steps per ms) remains 0/2 properties

Knowledge obtained : [(AND p0 p1), (X p0), (X p1), (X (X p0)), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : [(F (NOT p0)), (F (NOT p1))]

Knowledge based reduction with 7 factoid took 273 ms. Reduced automaton from 3 states, 6 edges and 2 AP (stutter insensitive) to 3 states, 6 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 127 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Stuttering acceptance computed with spot in 120 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Support contains 4 out of 1306 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1306/1306 places, 1188/1188 transitions.

Applied a total of 0 rules in 51 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

// Phase 1: matrix 1188 rows 1306 cols

[2024-06-01 01:42:40] [INFO ] Computed 588 invariants in 1929 ms

[2024-06-01 01:43:21] [INFO ] Performed 555/1306 implicitness test of which 0 returned IMPLICIT in 37 seconds.

[2024-06-01 01:43:59] [INFO ] Performed 625/1306 implicitness test of which 0 returned IMPLICIT in 75 seconds.

[2024-06-01 01:44:33] [INFO ] Performed 647/1306 implicitness test of which 0 returned IMPLICIT in 108 seconds.

[2024-06-01 01:45:06] [INFO ] Performed 672/1306 implicitness test of which 0 returned IMPLICIT in 142 seconds.

[2024-06-01 01:45:06] [INFO ] Timeout of Implicit test with SMT after 142 seconds.

[2024-06-01 01:45:06] [INFO ] Implicit Places using invariants in 147888 ms returned []

[2024-06-01 01:45:06] [INFO ] Invariant cache hit.

[2024-06-01 01:45:16] [INFO ] Implicit Places using invariants and state equation in 9996 ms returned []

Implicit Place search using SMT with State Equation took 157888 ms to find 0 implicit places.

[2024-06-01 01:45:16] [INFO ] Redundant transitions in 102 ms returned []

Running 1182 sub problems to find dead transitions.

[2024-06-01 01:45:16] [INFO ] Invariant cache hit.

Error getting values : (error "ParserException while parsing response: ((s0 1.0)

(s1 1.0)

(s2 1.0)

(s3 1.0)

(s4 1.0)

(s5 1.0)

(s6 1.0)

(s7 1.0)

(s8 1.0)

(s9 1.0)

(s10 1.0)

(s11 1.0)

(s12 1.0)

(s13 1.0)

(s14 1.0)

(s15 1.0)

(s16 1.0)

(s17 1.0)

(s18 1.0)

(s19 1.0)

(s20 1.0)

(s21 1.0)

(s22 1.0)

(s23 1.0)

(s24 1.0)

(s25 1.0)

(s26 1.0)

(s27 1.0)

(s28 1.0)

(s29 1.0)

(s30 1.0)

(s31 1.0)

(s32 1.0)

(s33 1.0)

(s34 1.0)

(s35 1.0)

(s36 1.0)

(s37 1.0)

(s38 1.0)

(s39 1.0)

(s40 1.0)

(s41 1.0)

(s42 1.0)

(s43 1.0)

(s44 1.0)

(s45 1.0)

(s46 1.0)

(s47 1.0)

(s48 1.0)

(s49 1.0)

(s50 1.0)

(s51 1.0)

(s52 1.0)

(s53 1.0)

(s54 1.0)

(s55 1.0)

(s56 1.0)

(s57 1.0)

(s58 1.0)

(s59 1.0)

(s60 1.0)

(s61 1.0)

(s62 1.0)

(s63 1.0)

(s64 1.0)

(s65 1.0)

(s66 1.0)

(s67 1.0)

(s68 1.0)

(s69 1.0)

(s70 1.0)

(s71 1.0)

(s72 1.0)

(s73 1.0)

(s74 1.0)

(s75 1.0)

(s76 1.0)

(s77 1.0)

(s78 1.0)

(s79 1.0)

(s80 1.0)

(s81 1.0)

(s82 1.0)

(s83 1.0)

(s84 1.0)

(s85 1.0)

(s86 1.0)

(s87 1.0)

(s88 1.0)

(s89 1.0)

(s90 1.0)

(s91 1.0)

(s92 1.0)

(s93 1.0)

(s94 1.0)

(s95 1.0)

(s96 1.0)

(s97 1.0)

(s98 1.0)

(s99 1.0)

(s100 1.0)

(s101 1.0)

(s102 1.0)

(s103 1.0)

(s104 1.0)

(s105 1.0)

(s106 1.0)

(s107 1.0)

(s108 timeout

org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 0 (INCLUDED_ONLY) 0/1306 variables, 1306/1306 constraints. Problems are: Problem set: 0 solved, 1182 unsolved

SMT process timed out in 30977ms, After SMT, problems are : Problem set: 0 solved, 1182 unsolved

Search for dead transitions found 0 dead transitions in 31002ms

Finished structural reductions in SI_LTL mode , in 1 iterations and 189056 ms. Remains : 1306/1306 places, 1188/1188 transitions.

Computed a total of 1306 stabilizing places and 1188 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1306 transition count 1188

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 p1), (X p0), (X p1), (X (X p0)), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 7 factoid took 161 ms. Reduced automaton from 3 states, 6 edges and 2 AP (stutter insensitive) to 3 states, 6 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 110 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

RANDOM walk for 856 steps (1 resets) in 23 ms. (35 steps per ms) remains 0/2 properties

Knowledge obtained : [(AND p0 p1), (X p0), (X p1), (X (X p0)), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : [(F (NOT p0)), (F (NOT p1))]

Knowledge based reduction with 7 factoid took 281 ms. Reduced automaton from 3 states, 6 edges and 2 AP (stutter insensitive) to 3 states, 6 edges and 2 AP (stutter insensitive).

Stuttering acceptance computed with spot in 121 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Stuttering acceptance computed with spot in 146 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Stuttering acceptance computed with spot in 136 ms :[(OR (NOT p0) (NOT p1)), (NOT p0), (NOT p1)]

Product exploration explored 100000 steps with 651 reset in 2143 ms.

Product exploration explored 100000 steps with 638 reset in 1917 ms.

Support contains 4 out of 1306 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1306/1306 places, 1188/1188 transitions.

Applied a total of 0 rules in 101 ms. Remains 1306 /1306 variables (removed 0) and now considering 1188/1188 (removed 0) transitions.

[2024-06-01 01:45:53] [INFO ] Invariant cache hit.

[2024-06-01 01:46:27] [INFO ] Performed 712/1306 implicitness test of which 0 returned IMPLICIT in 30 seconds.

[2024-06-01 01:46:37] [INFO ] Implicit Places using invariants in 43812 ms returned []

[2024-06-01 01:46:37] [INFO ] Invariant cache hit.

[2024-06-01 01:46:45] [INFO ] Implicit Places using invariants and state equation in 8147 ms returned []

Implicit Place search using SMT with State Equation took 51969 ms to find 0 implicit places.

[2024-06-01 01:46:45] [INFO ] Redundant transitions in 48 ms returned []

Running 1182 sub problems to find dead transitions.

[2024-06-01 01:46:45] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/1306 variables, 1306/1306 constraints. Problems are: Problem set: 0 solved, 1182 unsolved

SMT process timed out in 30965ms, After SMT, problems are : Problem set: 0 solved, 1182 unsolved

Search for dead transitions found 0 dead transitions in 30989ms

Finished structural reductions in SI_LTL mode , in 1 iterations and 83125 ms. Remains : 1306/1306 places, 1188/1188 transitions.

Treatment of property Echo-PT-d03r05-LTLCardinality-03 finished in 344888 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G((p0 U X((G((!p2||F(p3)))||p1)))))'

Support contains 8 out of 1321 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1321/1321 places, 1190/1190 transitions.

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 1320 transition count 1190

Applied a total of 1 rules in 29 ms. Remains 1320 /1321 variables (removed 1) and now considering 1190/1190 (removed 0) transitions.

// Phase 1: matrix 1190 rows 1320 cols

[2024-06-01 01:47:19] [INFO ] Computed 600 invariants in 2214 ms

[2024-06-01 01:48:05] [INFO ] Performed 582/1320 implicitness test of which 0 returned IMPLICIT in 41 seconds.

[2024-06-01 01:48:42] [INFO ] Performed 647/1320 implicitness test of which 0 returned IMPLICIT in 78 seconds.

[2024-06-01 01:49:16] [INFO ] Performed 669/1320 implicitness test of which 0 returned IMPLICIT in 112 seconds.

[2024-06-01 01:49:51] [INFO ] Performed 726/1320 implicitness test of which 0 returned IMPLICIT in 146 seconds.

[2024-06-01 01:49:51] [INFO ] Timeout of Implicit test with SMT after 146 seconds.

[2024-06-01 01:49:51] [INFO ] Implicit Places using invariants in 154205 ms returned []

[2024-06-01 01:49:51] [INFO ] Invariant cache hit.

[2024-06-01 01:50:19] [INFO ] Implicit Places using invariants and state equation in 28294 ms returned []

Implicit Place search using SMT with State Equation took 182510 ms to find 0 implicit places.

Running 1189 sub problems to find dead transitions.

[2024-06-01 01:50:19] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/1319 variables, 1319/1319 constraints. Problems are: Problem set: 0 solved, 1189 unsolved

SMT process timed out in 30982ms, After SMT, problems are : Problem set: 0 solved, 1189 unsolved

Search for dead transitions found 0 dead transitions in 31008ms

Starting structural reductions in LTL mode, iteration 1 : 1320/1321 places, 1190/1190 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 213561 ms. Remains : 1320/1321 places, 1190/1190 transitions.

Stuttering acceptance computed with spot in 417 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Running random walk in product with property : Echo-PT-d03r05-LTLCardinality-04

Product exploration explored 100000 steps with 33226 reset in 707 ms.

Product exploration explored 100000 steps with 33464 reset in 890 ms.

Computed a total of 1320 stabilizing places and 1190 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1320 transition count 1190

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 p1 p2 p3), (X p2), (X p3), (X (NOT (AND p0 (NOT p1) p2 (NOT p3)))), (X p0), (X (NOT (AND (NOT p1) p2 (NOT p3)))), (X p1), (X (X p2)), (X (X (NOT (AND (NOT p0) (NOT p1) (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) p2 (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) (NOT p2) (NOT p3))))), (X (X p3)), (X (X p0)), (X (X (NOT (AND p2 (NOT p3))))), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p3) (G (NOT p3))))]

False Knowledge obtained : []

Knowledge based reduction with 19 factoid took 1285 ms. Reduced automaton from 8 states, 16 edges and 4 AP (stutter sensitive) to 8 states, 16 edges and 4 AP (stutter sensitive).

Stuttering acceptance computed with spot in 352 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Reduction of identical properties reduced properties to check from 11 to 9

RANDOM walk for 23971 steps (93 resets) in 1780 ms. (13 steps per ms) remains 0/9 properties

Knowledge obtained : [(AND p0 p1 p2 p3), (X p2), (X p3), (X (NOT (AND p0 (NOT p1) p2 (NOT p3)))), (X p0), (X (NOT (AND (NOT p1) p2 (NOT p3)))), (X p1), (X (X p2)), (X (X (NOT (AND (NOT p0) (NOT p1) (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) p2 (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) (NOT p2) (NOT p3))))), (X (X p3)), (X (X p0)), (X (X (NOT (AND p2 (NOT p3))))), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p3) (G (NOT p3))))]

False Knowledge obtained : [(F (NOT (OR p2 p3))), (F (NOT (OR p0 p1 p3))), (F (NOT (OR p1 p2 p3))), (F (NOT (OR (NOT p0) p1 (NOT p2) p3))), (F (NOT p2)), (F (NOT p0)), (F (NOT p3)), (F (NOT (OR p1 (NOT p2) p3))), (F (NOT (OR (NOT p2) p3))), (F (NOT (OR (NOT p0) p1 p2 p3))), (F (NOT p1))]

Knowledge based reduction with 19 factoid took 6336 ms. Reduced automaton from 8 states, 16 edges and 4 AP (stutter sensitive) to 8 states, 16 edges and 4 AP (stutter sensitive).

Stuttering acceptance computed with spot in 411 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Stuttering acceptance computed with spot in 434 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Support contains 8 out of 1320 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1320/1320 places, 1190/1190 transitions.

Applied a total of 0 rules in 46 ms. Remains 1320 /1320 variables (removed 0) and now considering 1190/1190 (removed 0) transitions.

[2024-06-01 01:51:02] [INFO ] Invariant cache hit.

[2024-06-01 01:51:37] [INFO ] Performed 615/1320 implicitness test of which 0 returned IMPLICIT in 30 seconds.

[2024-06-01 01:52:15] [INFO ] Performed 709/1320 implicitness test of which 0 returned IMPLICIT in 68 seconds.

[2024-06-01 01:52:49] [INFO ] Performed 824/1320 implicitness test of which 0 returned IMPLICIT in 102 seconds.

[2024-06-01 01:53:10] [INFO ] Implicit Places using invariants in 127187 ms returned []

[2024-06-01 01:53:10] [INFO ] Invariant cache hit.

[2024-06-01 01:53:41] [INFO ] Implicit Places using invariants and state equation in 31564 ms returned []

Implicit Place search using SMT with State Equation took 158757 ms to find 0 implicit places.

Running 1189 sub problems to find dead transitions.

[2024-06-01 01:53:41] [INFO ] Invariant cache hit.

Error getting values : (error "Error writing to Z3 solver: java.io.IOException: Broken pipe")

At refinement iteration 0 (INCLUDED_ONLY) 0/1319 variables, 1319/1319 constraints. Problems are: Problem set: 0 solved, 1189 unsolved

SMT process timed out in 30869ms, After SMT, problems are : Problem set: 0 solved, 1189 unsolved

Search for dead transitions found 0 dead transitions in 30893ms

Finished structural reductions in LTL mode , in 1 iterations and 189705 ms. Remains : 1320/1320 places, 1190/1190 transitions.

Computed a total of 1320 stabilizing places and 1190 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 1320 transition count 1190

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 p1 p2 p3), (X p2), (X p3), (X (NOT (AND p0 (NOT p1) p2 (NOT p3)))), (X p0), (X (NOT (AND (NOT p1) p2 (NOT p3)))), (X p1), (X (X p2)), (X (X (NOT (AND (NOT p0) (NOT p1) (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) p2 (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) (NOT p2) (NOT p3))))), (X (X p3)), (X (X p0)), (X (X (NOT (AND p2 (NOT p3))))), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p3) (G (NOT p3))))]

False Knowledge obtained : []

Knowledge based reduction with 19 factoid took 1815 ms. Reduced automaton from 8 states, 16 edges and 4 AP (stutter sensitive) to 8 states, 16 edges and 4 AP (stutter sensitive).

Stuttering acceptance computed with spot in 441 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Reduction of identical properties reduced properties to check from 11 to 9

RANDOM walk for 15839 steps (61 resets) in 957 ms. (16 steps per ms) remains 0/9 properties

Knowledge obtained : [(AND p0 p1 p2 p3), (X p2), (X p3), (X (NOT (AND p0 (NOT p1) p2 (NOT p3)))), (X p0), (X (NOT (AND (NOT p1) p2 (NOT p3)))), (X p1), (X (X p2)), (X (X (NOT (AND (NOT p0) (NOT p1) (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) p2 (NOT p3))))), (X (X (NOT (AND p0 (NOT p1) (NOT p2) (NOT p3))))), (X (X p3)), (X (X p0)), (X (X (NOT (AND p2 (NOT p3))))), (X (X p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p3) (G (NOT p3))))]

False Knowledge obtained : [(F (NOT (OR p2 p3))), (F (NOT (OR p0 p1 p3))), (F (NOT (OR p1 p2 p3))), (F (NOT (OR (NOT p0) p1 (NOT p2) p3))), (F (NOT p2)), (F (NOT p0)), (F (NOT p3)), (F (NOT (OR p1 (NOT p2) p3))), (F (NOT (OR (NOT p2) p3))), (F (NOT (OR (NOT p0) p1 p2 p3))), (F (NOT p1))]

Knowledge based reduction with 19 factoid took 6629 ms. Reduced automaton from 8 states, 16 edges and 4 AP (stutter sensitive) to 8 states, 16 edges and 4 AP (stutter sensitive).

Stuttering acceptance computed with spot in 522 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Stuttering acceptance computed with spot in 443 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Stuttering acceptance computed with spot in 454 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Product exploration explored 100000 steps with 33181 reset in 1072 ms.

Product exploration explored 100000 steps with 33390 reset in 855 ms.

Applying partial POR strategy [false, true, false, true, true, true, false, true]

Stuttering acceptance computed with spot in 406 ms :[(AND (NOT p1) p2 (NOT p3)), (AND (NOT p1) p2 (NOT p3)), (AND p0 (NOT p1) p2 (NOT p3)), (NOT p3), (AND (NOT p3) p2), (AND (NOT p3) p2 (NOT p1)), (AND (NOT p1) p2 (NOT p3)), (AND (NOT p3) p2)]

Support contains 8 out of 1320 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 1320/1320 places, 1190/1190 transitions.

Graph (complete) has 4723 edges and 1320 vertex of which 1313 are kept as prefixes of interest. Removing 7 places using SCC suffix rule.5 ms

Discarding 7 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Applied a total of 1 rules in 159 ms. Remains 1313 /1320 variables (removed 7) and now considering 1189/1190 (removed 1) transitions.

[2024-06-01 01:54:27] [INFO ] Redundant transitions in 40 ms returned []

Running 1188 sub problems to find dead transitions.

// Phase 1: matrix 1189 rows 1313 cols

[2024-06-01 01:54:30] [INFO ] Computed 594 invariants in 3106 ms

Error getting values : (error "ParserException while parsing response: ((s0 1.0)

(s1 1.0)

(s2 1.0)

(s3 1.0)

(s4 1.0)

(s5 1.0)

(s6 1.0)

(s7 1.0)

(s8 1.0)

(s9 1.0)

(s10 1.0)

(s11 1.0)

(s12 1.0)

(s13 1.0)

(s14 1.0)

(s15 1.0)

(s16 1.0)

(s17 1.0)

(s18 1.0)

(s19 1.0)

(s20 1.0)

(s21 1.0)

(s22 1.0)

(s23 1.0)

(s24 1.0)

(s25 1.0)

(s26 1.0)

(s27 1.0)

(s28 1.0)

(s29 1.0)

(s30 1.0)

(s31 1.0)

(s32 1.0)

(s33 1.0)

(s34 1.0)

(s35 1.0)

(s36 1.0)

(s37 1.0)

(s38 1.0)

(s39 1.0)

(s40 1.0)

(s41 1.0)

(s42 1.0)

(s43 1.0)

(s44 1.0)

(s45 1.0)

(s46 1.0)

(s47 1.0)

(s48 1.0)

(s49 1.0)

(s50 1.0)

(s51 1.0)

(s52 1.0)

(s53 1.0)

(s54 1.0)

(s55 1.0)

(s56 1.0)

(s57 1.0)

(s58 1.0)

(s59 1.0)

(s60 1.0)

(s61 1.0)

(s62 1.0)

(s63 1.0)

(s64 1.0)

(s65 1.0)

(s66 1.0)

(s67 1.0)

(s68 1.0)

(s69 1.0)

(s70 1.0)

(s71 1.0)

(s72 1.0)

(s73 1.0)

(s74 1.0)

(s75 1.0)

(s76 1.0)

(s77 1.0)

(s78 1.0)

(s79 1.0)

(s80 1.0)

(s81 1.0)

(s82 1.0)

(s83 1.0)

(s84 1.0)

(s85 1.0)

(s86 1.0)

(s87 1.0)

(s88 1.0)

(s89 1.0)

(s90 1.0)

(s91 1.0)

(s92 1.0)

(s93 1.0)

(s94 1.0)

(s95 1.0)

(s96 1.0)

(s97 1.0)

(s98 1.0)

(s99 1.0)

(s100 1.0)

(s101 1.0)

(s102 1.0)

(s103 1.0)

(s104 1.0)

(s105 1.0)

(s106 1.0)

(s107 1.0)

(s108 1.0)

(s109 1.0)

(s110 1.0)

(s111 1.0)

(s112 1.0)

(s113 1.0)

(s114 1.0)

(s115 1.0)

(s116 1.0)

(s117 1.0)

(s118 1.0)

(s119 1.0)

(s120 1.0)

(s121 1.0)

(s122 1.0)

(s123 1.0)

(s124 1.0)

(s125 1.0)

(s126 1.0)

(s127 1.0)

(s128 1.0)

(s129 1.0)

(s130 1.0)

(s131 1.0)

(s132 1.0)

(s133 1.0)

(s134 1.0)

(s135 1.0)

(s136 1.0)

(s137 1.0)

(s138 1.0)

(s139 1.0)

(s140 1.0)

(s141 1.0)

(s142 1.0)

(s143 1.0)

(s144 1.0)

(s145 1.0)

(s146 1.0)

(s147 1.0)

(s148 1.0)

(s149 1.0)

(s150 1.0)

(s151 1.0)

(s152 1.0)

(s153 1.0)

(s154 1.0)

(s155 1.0)

(s156 1.0)

(s157 1.0)

(s158 1.0)

(s159 1.0)

(s160 1.0)

(s161 1.0)

(s162 1.0)

(s163 1.0)

(s164 1.0)

(s165 1.0)

(s166 1.0)

(s167 1.0)

(s168 1.0)

(s169 1.0)

(s170 1.0)

(s171 1.0)

(s172 1.0)

(s173 1.0)

(s174 1.0)

(s175 1.0)

(s176 1.0)

(s177 1.0)

(s178 1.0)

(s179 1.0)

(s180 1.0)

(s181 1.0)

(s182 1.0)

(s183 1.0)

(s184 1.0)

(s185 1.0)

(s186 1.0)

(s187 1.0)

(s188 1.0)

(s189 1.0)

(s190 1.0)

(s191 1.0)

(s192 1.0)

(s193 1.0)

(s194 1.0)

(s195 1.0)

(s196 1.0)

(s197 1.0)

(s198 1.0)

(s199 1.0)

(s200 1.0)

(s201 1.0)

(s202 1.0)

(s203 1.0)

(s204 1.0)

(s205 1.0)

(s206 1.0)

(s207 1.0)

(s208 1.0)

(s209 1.0)

(s210 1.0)

(s211 1.0)

(s212 1.0)

(s213 1.0)

(s214 1.0)

(s215 1.0)

(s216 1.0)

(s217 1.0)

(s218 1.0)

(s219 1.0)

(s220 1.0)

(s221 1.0)

(s222 1.0)

(s223 1.0)

(s224 1.0)

(s225 1.0)

(s226 1.0)

(s227 1.0)

(s228 1.0)

(s229 1.0)

(s230 1.0)

(s231 1.0)

(s232 1.0)

(s233 1.0)

(s234 1.0)

(s235 1.0)

(s236 1.0)

(s237 1.0)

(s238 1.0)

(s239 1.0)

(s240 1.0)

(s241 1.0)

(s242 1.0)

(s243 1.0)

(s244 1.0)

(s245 1.0)

(s246 1.0)

(s247 1.0)

(s248 1.0)

(s249 1.0)

(s250 1.0)

(s251 1.0)

(s252 1.0)

(s253 1.0)

(s254 1.0)

(s255 1.0)

(s256 1.0)

(s257 1.0)

(s258 1.0)

(s259 1.0)

(s260 1.0)

(s261 1.0)

(s262 1.0)

(s263 1.0)

(s264 1.0)

(s265 1.0)

(s266 1.0)

(s267 1.0)

(s268 1.0)

(s269 1.0)

(s270 1.0)

(s271 1.0)

(s272 1.0)

(s273 1.0)

(s274 1.0)

(s275 1.0)

(s276 1.0)

(s277 1.0)

(s278 1.0)

(s279 1.0)

(s280 1.0)

(s281 1.0)

(s282 1.0)

(s283 1.0)

(s284 1.0)

(s285 1.0)

(s286 1.0)

(s287 1.0)

(s288 1.0)

(s289 1.0)

(s290 1.0)

(s291 1.0)

(s292 1.0)

(s293 1.0)

(s294 1.0)

(s295 1.0)

(s296 1.0)

(s297 1.0)

(s298 1.0)

(s299 1.0)

(s300 1.0)

(s301 1.0)

(s302 1.0)

(s303 1.0)

(s304 1.0)

(s305 1.0)

(s306 1.0)

(s307 1.0)

(s308 1.0)

(s309 1.0)

(s310 1.0)

(s311 1.0)

(s312 1.0)

(s313 1.0)

(s314 1.0)

(s315 1.0)

(s316 1.0)

(s317 1.0)

(s318 1.0)

(s319 1.0)

(s320 1.0)

(s321 1.0)

(s322 1.0)

(s323 1.0)

(s324 1.0)

(s325 1.0)

(s327 1.0)

(s328 1.0)

(s329 1.0)

(s330 1.0)

(s331 1.0)

(s332 1.0)

(s333 1.0)

(s334 1.0)

(s335 1.0)

(s336 1.0)

(s337 1.0)

(s338 1.0)

(s339 1.0)

(s340 1.0)

(s341 1.0)

(s342 1.0)

(s343 1.0)

(s344 1.0)

(s345 1.0)

(s346 1.0)

(s347 1.0)

(s348 1.0)

(s349 1.0)

(s350 1.0)

(s351 1.0)

(s352 1.0)

(s353 1.0)

(s354 1.0)

(s355 1.0)

(s356 1.0)

(s357 1.0)

(s358 1.0)

(s359 1.0)

(s360 1.0)

(s361 1.0)

(s362 1.0)

(s363 1.0)

(s364 1.0)

(s365 1.0)

(s366 1.0)

(s367 1.0)

(s368 1.0)

(s369 1.0)

(s370 1.0)

(s371 1.0)

(s372 1.0)

(s373 1.0)

(s374 1.0)

(s375 1.0)

(s376 1.0)

(s377 1.0)

(s378 1.0)

(s379 1.0)

(s380 1.0)

(s381 1.0)

(s382 1.0)

(s383 1.0)

(s384 1.0)

(s385 1.0)

(s386 1.0)

(s387 1.0)

(s388 1.0)

(s389 1.0)

(s390 1.0)

(s391 1.0)

(s392 1.0)

(s393 1.0)

(s394 1.0)

(s395 1.0)

(s396 1.0)

(s397 1.0)

(s398 1.0)

(s399 1.0)

(s400 1.0)

(s401 1.0)

(s402 1.0)

(s403 1.0)

(s404 1.0)

(s405 1.0)

(s406 1.0)

(s407 1.0)

(s408 1.0)

(s409 1.0)

(s410 1.0)

(s411 1.0)

(s412 1.0)

(s413 1.0)

(s414 1.0)

(s415 1.0)

(s416 1.0)

(s417 1.0)

(s418 1.0)

(s419 1.0)

(s420 1.0)

(s421 1.0)

(s422 1.0)

(s423 1.0)

(s424 1.0)

(s425 1.0)

(s426 1.0)

(s427 1.0)

(s428 1.0)

(s429 1.0)

(s430 1.0)

(s431 1.0)

(s432 1.0)

(s433 1.0)

(s434 1.0)

(s435 1.0)

(s436 1.0)

(s437 1.0)

(s438 1.0)

(s439 1.0)

(s440 1.0)

(s441 1.0)

(s442 1.0)

(s443 1.0)

(s444 1.0)

(s445 1.0)

(s446 1.0)

(s447 1.0)

(s448 1.0)

(s449 1.0)

(s450 1.0)

(s451 1.0)

(s452 1.0)

(s453 1.0)

(s454 1.0)

(s455 1.0)

(s456 1.0)

(s457 1.0)

(s458 1.0)

(s459 1.0)

(s460 1.0)

(s461 1.0)

(s462 1.0)

(s463 1.0)

(s464 1.0)

(s465 1.0)

(s466 1.0)

(s467 1.0)

(s468 1.0)

(s469 1.0)

(s470 1.0)

(s471 1.0)

(s472 1.0)

(s473 1.0)

(s474 1.0)

(s475 1.0)

(s476 1.0)

(s477 1.0)

(s478 1.0)

(s479 1.0)

(s480 1.0)

(s481 1.0)

(s482 1.0)

(s483 1.0)

(s484 1.0)

(s485 1.0)

(s486 1.0)

(s487 1.0)

(s488 1.0)

(s489 1.0)

(s490 1.0)

(s491 1.0)

(s492 1.0)

(s493 1.0)

(s494 1.0)

(s495 1.0)

(s496 1.0)

(s497 1.0)

(s498 1.0)

(s499 1.0)

(s500 1.0)

(s501 1.0)

(s502 1.0)

(s503 1.0)

(s504 1.0)

(s505 1.0)

(s506 1.0)

(s507 1.0)

(s508 1.0)

(s509 1.0)

(s510 1.0)

(s511 1.0)

(s512 1.0)

(s513 1.0)

(s514 1.0)

(s515 1.0)

(s516 1.0)

(s517 1.0)

(s518 1.0)

(s519 1.0)

(s520 1.0)

(s521 1.0)

(s522 1.0)

(s523 1.0)

(s524 1.0)

(s525 1.0)

(s526 1.0)

(s527 1.0)

(s528 1.0)

(s529 1.0)

(s530 1.0)

(s531 1.0)

(s532 1.0)

(s533 1.0)

(s534 1.0)

(s535 1.0)

(s536 1.0)

(s537 1.0)

(s538 1.0)

(s539 1.0)

(s540 1.0)

(s541 1.0)

(s542 1.0)

(s543 1.0)

(s544 1.0)

(s545 1.0)

(s546 1.0)

(s547 1.0)

(s548 1.0)

(s549 1.0)

(s550 1.0)

(s551 1.0)

(s552 1.0)

(s553 1.0)

(s554 1.0)

(s555 1.0)

(s556 1.0)

(s557 1.0)

(s558 1.0)

(s559 1.0)

(s560 1.0)

(s561 1.0)

(s562 1.0)

(s563 1.0)

(s564 1.0)

(s565 1.0)

(s566 1.0)

(s567 1.0)

(s568 1.0)

(s569 1.0)

(s570 1.0)

(s571 1.0)

(s572 1.0)

(s573 1.0)

(s574 1.0)

(s575 1.0)

(s576 1.0)

(s577 1.0)

(s578 1.0)

(s579 timeout

1.0 org.smtlib.IParser$ParserException: Unbalanced parentheses at end of input")

At refinement iteration 0 (INCLUDED_ONLY) 0/1312 variables, 1312/1312 constraints. Problems are: Problem set: 0 solved, 1188 unsolved

SMT process timed out in 33867ms, After SMT, problems are : Problem set: 0 solved, 1188 unsolved

Search for dead transitions found 0 dead transitions in 33889ms

Starting structural reductions in SI_LTL mode, iteration 1 : 1313/1320 places, 1189/1190 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 34104 ms. Remains : 1313/1320 places, 1189/1190 transitions.

Support contains 8 out of 1320 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1320/1320 places, 1190/1190 transitions.