About the Execution of LTSMin+red for AirplaneLD-PT-4000

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 14775.088 | 1226161.00 | 1626254.00 | 3713.80 | FTFFFFTFFFFTFFTF | normal |

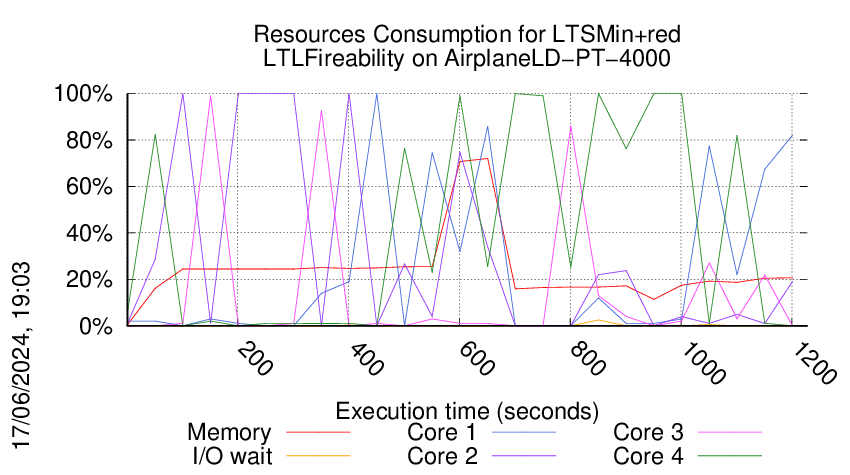

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r464-smll-171620118300308.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

...............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool ltsminxred

Input is AirplaneLD-PT-4000, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r464-smll-171620118300308

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 88M

-rw-r--r-- 1 mcc users 1.9M Apr 12 10:01 CTLCardinality.txt

-rw-r--r-- 1 mcc users 5.6M Apr 12 10:01 CTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9M Apr 12 07:07 CTLFireability.txt

-rw-r--r-- 1 mcc users 11M Apr 12 07:07 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:42 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.5K May 18 16:42 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 1.4M Apr 22 14:27 LTLCardinality.txt

-rw-r--r-- 1 mcc users 3.4M Apr 22 14:27 LTLCardinality.xml

-rw-r--r-- 1 mcc users 900K Apr 22 14:27 LTLFireability.txt

-rw-r--r-- 1 mcc users 3.7M Apr 22 14:27 LTLFireability.xml

-rw-r--r-- 1 mcc users 5.0M Apr 12 16:19 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 16M Apr 12 16:19 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 3.3M Apr 12 13:51 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 18M Apr 12 13:51 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 191K Apr 22 14:27 UpperBounds.txt

-rw-r--r-- 1 mcc users 358K Apr 22 14:27 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 18 16:42 equiv_col

-rw-r--r-- 1 mcc users 5 May 18 16:42 instance

-rw-r--r-- 1 mcc users 6 May 18 16:42 iscolored

-rw-r--r-- 1 mcc users 18M May 18 16:42 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-00

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-01

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-02

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-03

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-04

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-05

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-06

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-07

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-08

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-09

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-10

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-11

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-12

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-13

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-14

FORMULA_NAME AirplaneLD-PT-4000-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1717253397009

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=LTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=AirplaneLD-PT-4000

BK_MEMORY_CONFINEMENT=16384

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202405141337

[2024-06-01 14:49:59] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -timeout, 360, -rebuildPNML]

[2024-06-01 14:49:59] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-06-01 14:50:01] [INFO ] Load time of PNML (sax parser for PT used): 1885 ms

[2024-06-01 14:50:01] [INFO ] Transformed 28019 places.

[2024-06-01 14:50:01] [INFO ] Transformed 32008 transitions.

[2024-06-01 14:50:01] [INFO ] Found NUPN structural information;

[2024-06-01 14:50:01] [INFO ] Parsed PT model containing 28019 places and 32008 transitions and 122028 arcs in 2256 ms.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 282 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 5 formulas.

Reduce places removed 12002 places and 0 transitions.

FORMULA AirplaneLD-PT-4000-LTLFireability-01 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA AirplaneLD-PT-4000-LTLFireability-02 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA AirplaneLD-PT-4000-LTLFireability-06 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA AirplaneLD-PT-4000-LTLFireability-09 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA AirplaneLD-PT-4000-LTLFireability-15 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 16011 out of 16017 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16017/16017 places, 32008/32008 transitions.

Reduce places removed 3 places and 0 transitions.

Iterating post reduction 0 with 3 rules applied. Total rules applied 3 place count 16014 transition count 32008

Applied a total of 3 rules in 176 ms. Remains 16014 /16017 variables (removed 3) and now considering 32008/32008 (removed 0) transitions.

// Phase 1: matrix 32008 rows 16014 cols

[2024-06-01 14:50:42] [INFO ] Computed 1 invariants in 32383 ms

[2024-06-01 14:50:48] [INFO ] Implicit Places using invariants in 38211 ms returned []

Implicit Place search using SMT only with invariants took 38270 ms to find 0 implicit places.

Running 16004 sub problems to find dead transitions.

[2024-06-01 14:50:49] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/16009 variables, 16009/16009 constraints. Problems are: Problem set: 0 solved, 16004 unsolved

Solver is answering 'unknown', stopping.

After SMT solving in domain Real declared 16009/48022 variables, and 16009 constraints, problems are : Problem set: 0 solved, 16004 unsolved in 30908 ms.

Refiners :[Domain max(s): 16009/16014 constraints, Generalized P Invariants (flows): 0/1 constraints, State Equation: 0/16014 constraints, PredecessorRefiner: 16004/4 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 16004 unsolved

At refinement iteration 0 (INCLUDED_ONLY) 0/16009 variables, 16009/16009 constraints. Problems are: Problem set: 0 solved, 16004 unsolved

Solver is answering 'unknown', stopping.

After SMT solving in domain Int declared 16009/48022 variables, and 16009 constraints, problems are : Problem set: 0 solved, 16004 unsolved in 30329 ms.

Refiners :[Domain max(s): 16009/16014 constraints, Generalized P Invariants (flows): 0/1 constraints, State Equation: 0/16014 constraints, PredecessorRefiner: 16000/4 constraints, Known Traps: 0/0 constraints]

After SMT, in 340976ms problems are : Problem set: 0 solved, 16004 unsolved

Search for dead transitions found 0 dead transitions in 341334ms

Starting structural reductions in LTL mode, iteration 1 : 16014/16017 places, 32008/32008 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 379949 ms. Remains : 16014/16017 places, 32008/32008 transitions.

Support contains 16011 out of 16014 places after structural reductions.

[2024-06-01 14:56:33] [INFO ] Flatten gal took : 1441 ms

[2024-06-01 14:56:35] [INFO ] Flatten gal took : 1068 ms

[2024-06-01 14:56:37] [INFO ] Input system was already deterministic with 32008 transitions.

Reduction of identical properties reduced properties to check from 20 to 18

RANDOM walk for 34466 steps (4348 resets) in 120042 ms. (0 steps per ms) remains 3/18 properties

BEST_FIRST walk for 40004 steps (0 resets) in 181 ms. (219 steps per ms) remains 3/3 properties

BEST_FIRST walk for 40004 steps (0 resets) in 171 ms. (232 steps per ms) remains 3/3 properties

BEST_FIRST walk for 40004 steps (0 resets) in 102 ms. (388 steps per ms) remains 3/3 properties

[2024-06-01 14:57:08] [INFO ] Invariant cache hit.

At refinement iteration 0 (INCLUDED_ONLY) 0/7 variables, 7/7 constraints. Problems are: Problem set: 0 solved, 3 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/7 variables, 0/7 constraints. Problems are: Problem set: 0 solved, 3 unsolved

At refinement iteration 2 (OVERLAPS) 2/9 variables, 1/8 constraints. Problems are: Problem set: 0 solved, 3 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/9 variables, 2/10 constraints. Problems are: Problem set: 0 solved, 3 unsolved

At refinement iteration 4 (INCLUDED_ONLY) 0/9 variables, 0/10 constraints. Problems are: Problem set: 0 solved, 3 unsolved

Problem AtomicPropp17 is UNSAT

At refinement iteration 5 (OVERLAPS) 6010/6019 variables, 9/19 constraints. Problems are: Problem set: 1 solved, 2 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/6019 variables, 0/19 constraints. Problems are: Problem set: 1 solved, 2 unsolved

SMT process timed out in 5173ms, After SMT, problems are : Problem set: 1 solved, 2 unsolved

Skipping Parikh replay, no witness traces provided.

Support contains 3 out of 16014 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Graph (complete) has 22012 edges and 16014 vertex of which 10014 are kept as prefixes of interest. Removing 6000 places using SCC suffix rule.52 ms

Discarding 6000 places :

Also discarding 0 output transitions

Drop transitions (Empty/Sink Transition effects.) removed 12000 transitions

Reduce isomorphic transitions removed 12000 transitions.

Iterating post reduction 0 with 12000 rules applied. Total rules applied 12001 place count 10014 transition count 20008

Performed 4 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 1 with 4 Pre rules applied. Total rules applied 12001 place count 10014 transition count 20004

Deduced a syphon composed of 4 places in 7 ms

Ensure Unique test removed 2 places

Reduce places removed 6 places and 0 transitions.

Iterating global reduction 1 with 10 rules applied. Total rules applied 12011 place count 10008 transition count 20004

Free-agglomeration rule applied 10000 times.

Iterating global reduction 1 with 10000 rules applied. Total rules applied 22011 place count 10008 transition count 10004

Ensure Unique test removed 1 places

Reduce places removed 10001 places and 0 transitions.

Ensure Unique test removed 9997 transitions

Reduce isomorphic transitions removed 9997 transitions.

Iterating post reduction 1 with 19998 rules applied. Total rules applied 42009 place count 7 transition count 7

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 1 Pre rules applied. Total rules applied 42009 place count 7 transition count 6

Deduced a syphon composed of 1 places in 0 ms

Ensure Unique test removed 1 places

Reduce places removed 2 places and 0 transitions.

Iterating global reduction 2 with 3 rules applied. Total rules applied 42012 place count 5 transition count 6

Applied a total of 42012 rules in 8442 ms. Remains 5 /16014 variables (removed 16009) and now considering 6/32008 (removed 32002) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 8442 ms. Remains : 5/16014 places, 6/32008 transitions.

RANDOM walk for 63 steps (14 resets) in 7 ms. (7 steps per ms) remains 0/2 properties

FORMULA AirplaneLD-PT-4000-LTLFireability-04 FALSE TECHNIQUES REACHABILITY_KNOWLEDGE

Successfully simplified 1 atomic propositions for a total of 10 simplifications.

FORMULA AirplaneLD-PT-4000-LTLFireability-11 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Computed a total of 16014 stabilizing places and 32008 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 16014 transition count 32008

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(F((p0&&F(p1)))))'

Support contains 4001 out of 16014 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 102 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

[2024-06-01 14:57:27] [INFO ] Invariant cache hit.

[2024-06-01 14:57:51] [INFO ] Implicit Places using invariants in 24149 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 24172 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 81 ms. Remains 16013 /16013 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 24362 ms. Remains : 16013/16014 places, 32008/32008 transitions.

Stuttering acceptance computed with spot in 312 ms :[(OR (NOT p0) (NOT p1)), (NOT p1), (OR (NOT p0) (NOT p1))]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-00

Stuttering criterion allowed to conclude after 10 steps with 0 reset in 88 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-00 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-00 finished in 24923 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((F(G(p0))||(p1 U X(p2))))'

Support contains 2005 out of 16014 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 51 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

[2024-06-01 14:57:52] [INFO ] Invariant cache hit.

[2024-06-01 14:58:20] [INFO ] Implicit Places using invariants in 27566 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 27588 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 63 ms. Remains 16013 /16013 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 27704 ms. Remains : 16013/16014 places, 32008/32008 transitions.

Stuttering acceptance computed with spot in 226 ms :[(AND (NOT p0) (NOT p2)), (AND (NOT p0) (NOT p2)), (AND (NOT p2) (NOT p0)), (NOT p0)]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-03

Stuttering criterion allowed to conclude after 8 steps with 1 reset in 90 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-03 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-03 finished in 28110 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((G(F((G(F(p1))||p0)))||G(p2))))'

Support contains 8004 out of 16014 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Discarding 7996 places :

Symmetric choice reduction at 0 with 7996 rule applications. Total rules 7996 place count 8018 transition count 24012

Iterating global reduction 0 with 7996 rules applied. Total rules applied 15992 place count 8018 transition count 24012

Ensure Unique test removed 7996 transitions

Reduce isomorphic transitions removed 7996 transitions.

Iterating post reduction 0 with 7996 rules applied. Total rules applied 23988 place count 8018 transition count 16016

Applied a total of 23988 rules in 955 ms. Remains 8018 /16014 variables (removed 7996) and now considering 16016/32008 (removed 15992) transitions.

// Phase 1: matrix 16016 rows 8018 cols

[2024-06-01 14:58:27] [INFO ] Computed 1 invariants in 6135 ms

[2024-06-01 14:58:29] [INFO ] Implicit Places using invariants in 7923 ms returned [8017]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 7930 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 8017/16014 places, 16016/32008 transitions.

Applied a total of 0 rules in 26 ms. Remains 8017 /8017 variables (removed 0) and now considering 16016/16016 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 8912 ms. Remains : 8017/16014 places, 16016/32008 transitions.

Stuttering acceptance computed with spot in 196 ms :[(AND (NOT p2) (NOT p1) (NOT p0)), (AND (NOT p2) (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-05

Product exploration timeout after 6540 steps with 843 reset in 10013 ms.

Product exploration timeout after 7170 steps with 927 reset in 10001 ms.

Computed a total of 8017 stabilizing places and 16016 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 8017 transition count 16016

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p2 (NOT p1) (NOT p0)), (X p2), (X (NOT (AND (NOT p1) (NOT p0) (NOT p2)))), (X (NOT p0)), (X (NOT p1)), (F (G p2)), (F (G (NOT p1))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 8 factoid took 278 ms. Reduced automaton from 4 states, 7 edges and 3 AP (stutter sensitive) to 3 states, 6 edges and 3 AP (stutter insensitive).

Stuttering acceptance computed with spot in 122 ms :[(AND (NOT p2) (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

RANDOM walk for 40000 steps (5161 resets) in 49888 ms. (0 steps per ms) remains 3/5 properties

BEST_FIRST walk for 40004 steps (8 resets) in 6692 ms. (5 steps per ms) remains 3/3 properties

BEST_FIRST walk for 32004 steps (0 resets) in 21978 ms. (1 steps per ms) remains 3/3 properties

BEST_FIRST walk for 40004 steps (8 resets) in 6473 ms. (6 steps per ms) remains 3/3 properties

// Phase 1: matrix 16016 rows 8017 cols

[2024-06-01 14:59:34] [INFO ] Computed 0 invariants in 6346 ms

At refinement iteration 0 (INCLUDED_ONLY) 0/8004 variables, 0/0 constraints. Problems are: Problem set: 0 solved, 3 unsolved

SMT process timed out in 30891ms, After SMT, problems are : Problem set: 0 solved, 3 unsolved

Fused 3 Parikh solutions to 1 different solutions.

Parikh walk visited 0 properties in 0 ms.

Support contains 8004 out of 8017 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 8017/8017 places, 16016/16016 transitions.

Graph (complete) has 10015 edges and 8017 vertex of which 8015 are kept as prefixes of interest. Removing 2 places using SCC suffix rule.11 ms

Discarding 2 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Drop transitions (Empty/Sink Transition effects.) removed 3 transitions

Reduce isomorphic transitions removed 3 transitions.

Drop transitions (Trivial Post-Agglo cleanup.) removed 1 transitions

Trivial Post-agglo rules discarded 1 transitions

Performed 1 trivial Post agglomeration. Transition count delta: 1

Iterating post reduction 0 with 4 rules applied. Total rules applied 5 place count 8015 transition count 16011

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 1 with 1 rules applied. Total rules applied 6 place count 8014 transition count 16011

Performed 2 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 2 Pre rules applied. Total rules applied 6 place count 8014 transition count 16009

Deduced a syphon composed of 2 places in 3 ms

Ensure Unique test removed 1 places

Reduce places removed 3 places and 0 transitions.

Iterating global reduction 2 with 5 rules applied. Total rules applied 11 place count 8011 transition count 16009

Free-agglomeration rule applied 3 times.

Iterating global reduction 2 with 3 rules applied. Total rules applied 14 place count 8011 transition count 16006

Reduce places removed 3 places and 0 transitions.

Iterating post reduction 2 with 3 rules applied. Total rules applied 17 place count 8008 transition count 16006

Applied a total of 17 rules in 1217 ms. Remains 8008 /8017 variables (removed 9) and now considering 16006/16016 (removed 10) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 1219 ms. Remains : 8008/8017 places, 16006/16016 transitions.

RANDOM walk for 40000 steps (6664 resets) in 57733 ms. (0 steps per ms) remains 3/3 properties

BEST_FIRST walk for 40004 steps (8 resets) in 6247 ms. (6 steps per ms) remains 3/3 properties

BEST_FIRST walk for 32004 steps (0 resets) in 20155 ms. (1 steps per ms) remains 3/3 properties

BEST_FIRST walk for 40004 steps (8 resets) in 6686 ms. (5 steps per ms) remains 3/3 properties

Finished probabilistic random walk after 180011 steps, run visited all 3 properties in 33188 ms. (steps per millisecond=5 )

Probabilistic random walk after 180011 steps, saw 78990 distinct states, run finished after 33206 ms. (steps per millisecond=5 ) properties seen :3

Knowledge obtained : [(AND p2 (NOT p1) (NOT p0)), (X p2), (X (NOT (AND (NOT p1) (NOT p0) (NOT p2)))), (X (NOT p0)), (X (NOT p1)), (F (G p2)), (F (G (NOT p1))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p1), (F p0), (F (NOT p2)), (F (NOT (AND (NOT p0) (NOT p1)))), (F (NOT (OR p2 p0 p1)))]

Property proved to be false thanks to negative knowledge :(F (NOT p2))

Knowledge based reduction with 8 factoid took 360 ms. Reduced automaton from 3 states, 6 edges and 3 AP (stutter insensitive) to 1 states, 1 edges and 0 AP (stutter insensitive).

FORMULA AirplaneLD-PT-4000-LTLFireability-05 FALSE TECHNIQUES KNOWLEDGE

Treatment of property AirplaneLD-PT-4000-LTLFireability-05 finished in 156811 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(F((p0&&(p1 U G((G(p3)||p2)))))))'

Support contains 6005 out of 16014 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Graph (complete) has 22012 edges and 16014 vertex of which 12012 are kept as prefixes of interest. Removing 4002 places using SCC suffix rule.72 ms

Discarding 4002 places :

Also discarding 8000 output transitions

Drop transitions (Output transitions of discarded places.) removed 8000 transitions

Discarding 5998 places :

Symmetric choice reduction at 0 with 5998 rule applications. Total rules 5999 place count 6014 transition count 18010

Iterating global reduction 0 with 5998 rules applied. Total rules applied 11997 place count 6014 transition count 18010

Ensure Unique test removed 5998 transitions

Reduce isomorphic transitions removed 5998 transitions.

Iterating post reduction 0 with 5998 rules applied. Total rules applied 17995 place count 6014 transition count 12012

Applied a total of 17995 rules in 2367 ms. Remains 6014 /16014 variables (removed 10000) and now considering 12012/32008 (removed 19996) transitions.

// Phase 1: matrix 12012 rows 6014 cols

[2024-06-01 15:01:04] [INFO ] Computed 1 invariants in 4585 ms

[2024-06-01 15:01:05] [INFO ] Implicit Places using invariants in 5960 ms returned []

Implicit Place search using SMT only with invariants took 5962 ms to find 0 implicit places.

Running 6006 sub problems to find dead transitions.

[2024-06-01 15:01:05] [INFO ] Invariant cache hit.

Solver is answering 'unknown', stopping.

After SMT solving in domain Real declared 6010/18026 variables, and 0 constraints, problems are : Problem set: 0 solved, 6006 unsolved in 30099 ms.

Refiners :[Generalized P Invariants (flows): 0/1 constraints, State Equation: 0/6014 constraints, PredecessorRefiner: 6006/4 constraints, Known Traps: 0/0 constraints]

Escalating to Integer solving :Problem set: 0 solved, 6006 unsolved

Solver is answering 'unknown', stopping.

After SMT solving in domain Int declared 6010/18026 variables, and 0 constraints, problems are : Problem set: 0 solved, 6006 unsolved in 30158 ms.

Refiners :[Generalized P Invariants (flows): 0/1 constraints, State Equation: 0/6014 constraints, PredecessorRefiner: 6002/4 constraints, Known Traps: 0/0 constraints]

After SMT, in 164778ms problems are : Problem set: 0 solved, 6006 unsolved

Search for dead transitions found 0 dead transitions in 164875ms

Starting structural reductions in SI_LTL mode, iteration 1 : 6014/16014 places, 12012/32008 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 173249 ms. Remains : 6014/16014 places, 12012/32008 transitions.

Stuttering acceptance computed with spot in 462 ms :[(OR (NOT p0) (AND (NOT p2) (NOT p3))), (OR (NOT p0) (AND (NOT p2) (NOT p3))), (AND (NOT p2) (NOT p3)), (OR (AND (NOT p0) (NOT p3)) (AND (NOT p2) (NOT p3))), (AND (NOT p2) (NOT p3)), (AND (NOT p2) (NOT p3)), (AND (NOT p2) (NOT p3))]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-07

Stuttering criterion allowed to conclude after 8 steps with 0 reset in 42 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-07 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-07 finished in 175880 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((X(G(p0))&&F(p1))))'

Support contains 5 out of 16014 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 68 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

// Phase 1: matrix 32008 rows 16014 cols

[2024-06-01 15:04:26] [INFO ] Computed 1 invariants in 32764 ms

[2024-06-01 15:05:00] [INFO ] Implicit Places using invariants in 67520 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 67554 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 75 ms. Remains 16013 /16013 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 67700 ms. Remains : 16013/16014 places, 32008/32008 transitions.

Stuttering acceptance computed with spot in 330 ms :[(NOT p0), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), true, (OR (NOT p1) (NOT p0))]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-08

Entered a terminal (fully accepting) state of product in 2 steps with 0 reset in 46 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-08 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-08 finished in 68172 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(p0)))'

Support contains 4 out of 16014 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 283 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

[2024-06-01 15:05:01] [INFO ] Invariant cache hit.

[2024-06-01 15:05:32] [INFO ] Implicit Places using invariants in 30605 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 30643 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Graph (complete) has 22011 edges and 16013 vertex of which 16012 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.28 ms

Discarding 1 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Applied a total of 1 rules in 294 ms. Remains 16012 /16013 variables (removed 1) and now considering 32007/32008 (removed 1) transitions.

// Phase 1: matrix 32007 rows 16012 cols

[2024-06-01 15:06:03] [INFO ] Computed 0 invariants in 30970 ms

[2024-06-01 15:06:33] [INFO ] Implicit Places using invariants in 61318 ms returned []

Implicit Place search using SMT only with invariants took 61332 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 16012/16014 places, 32007/32008 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 92555 ms. Remains : 16012/16014 places, 32007/32008 transitions.

Stuttering acceptance computed with spot in 40 ms :[(NOT p0)]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-10

Stuttering criterion allowed to conclude after 7 steps with 0 reset in 33 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-10 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-10 finished in 92691 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(p0)))'

Support contains 2 out of 16014 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Graph (complete) has 22012 edges and 16014 vertex of which 8 are kept as prefixes of interest. Removing 16006 places using SCC suffix rule.16 ms

Discarding 16006 places :

Also discarding 32000 output transitions

Drop transitions (Output transitions of discarded places.) removed 32000 transitions

Applied a total of 1 rules in 43 ms. Remains 8 /16014 variables (removed 16006) and now considering 8/32008 (removed 32000) transitions.

// Phase 1: matrix 8 rows 8 cols

[2024-06-01 15:06:34] [INFO ] Computed 1 invariants in 0 ms

[2024-06-01 15:06:34] [INFO ] Implicit Places using invariants in 26 ms returned [7]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 28 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 7/16014 places, 8/32008 transitions.

Graph (complete) has 5 edges and 7 vertex of which 6 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.0 ms

Discarding 1 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Applied a total of 1 rules in 4 ms. Remains 6 /7 variables (removed 1) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 6 cols

[2024-06-01 15:06:34] [INFO ] Computed 0 invariants in 0 ms

[2024-06-01 15:06:34] [INFO ] Implicit Places using invariants in 18 ms returned []

[2024-06-01 15:06:34] [INFO ] Invariant cache hit.

[2024-06-01 15:06:34] [INFO ] Implicit Places using invariants and state equation in 24 ms returned []

Implicit Place search using SMT with State Equation took 45 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 6/16014 places, 7/32008 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 120 ms. Remains : 6/16014 places, 7/32008 transitions.

Stuttering acceptance computed with spot in 38 ms :[(NOT p0)]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-12

Stuttering criterion allowed to conclude after 4 steps with 0 reset in 0 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-12 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-12 finished in 184 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(X(X(F(p0))))))'

Support contains 2 out of 16014 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 53 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

// Phase 1: matrix 32008 rows 16014 cols

[2024-06-01 15:07:06] [INFO ] Computed 1 invariants in 32619 ms

[2024-06-01 15:07:40] [INFO ] Implicit Places using invariants in 66384 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 66412 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 58 ms. Remains 16013 /16013 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 66524 ms. Remains : 16013/16014 places, 32008/32008 transitions.

Stuttering acceptance computed with spot in 322 ms :[(NOT p0), (NOT p0), (NOT p0), (NOT p0), (NOT p0)]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-13

Stuttering criterion allowed to conclude after 10 steps with 0 reset in 32 ms.

FORMULA AirplaneLD-PT-4000-LTLFireability-13 FALSE TECHNIQUES STUTTER_TEST

Treatment of property AirplaneLD-PT-4000-LTLFireability-13 finished in 66932 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202405141337/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(F(p0)))'

Support contains 2 out of 16014 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 16014/16014 places, 32008/32008 transitions.

Applied a total of 0 rules in 248 ms. Remains 16014 /16014 variables (removed 0) and now considering 32008/32008 (removed 0) transitions.

[2024-06-01 15:07:41] [INFO ] Invariant cache hit.

[2024-06-01 15:08:13] [INFO ] Implicit Places using invariants in 32230 ms returned [16013]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 32252 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 16013/16014 places, 32008/32008 transitions.

Graph (complete) has 22011 edges and 16013 vertex of which 16012 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.26 ms

Discarding 1 places :

Also discarding 1 output transitions

Drop transitions (Output transitions of discarded places.) removed 1 transitions

Drop transitions (Trivial Post-Agglo cleanup.) removed 1 transitions

Trivial Post-agglo rules discarded 1 transitions

Performed 1 trivial Post agglomeration. Transition count delta: 1

Iterating post reduction 0 with 1 rules applied. Total rules applied 2 place count 16012 transition count 32006

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 1 with 1 rules applied. Total rules applied 3 place count 16011 transition count 32006

Applied a total of 3 rules in 424 ms. Remains 16011 /16013 variables (removed 2) and now considering 32006/32008 (removed 2) transitions.

// Phase 1: matrix 32006 rows 16011 cols

[2024-06-01 15:08:44] [INFO ] Computed 0 invariants in 30734 ms

[2024-06-01 15:09:17] [INFO ] Implicit Places using invariants in 63298 ms returned []

Implicit Place search using SMT only with invariants took 63309 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 16011/16014 places, 32006/32008 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 96234 ms. Remains : 16011/16014 places, 32006/32008 transitions.

Stuttering acceptance computed with spot in 73 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : AirplaneLD-PT-4000-LTLFireability-14

Product exploration timeout after 2630 steps with 380 reset in 10052 ms.

Product exploration timeout after 2560 steps with 371 reset in 10036 ms.

Computed a total of 16011 stabilizing places and 32006 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 16011 transition count 32006

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [p0, (X p0), (F (G p0))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge (Minato strategy)

Knowledge based reduction with 3 factoid took 25 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA AirplaneLD-PT-4000-LTLFireability-14 TRUE TECHNIQUES KNOWLEDGE

Treatment of property AirplaneLD-PT-4000-LTLFireability-14 finished in 161601 ms.

All properties solved by simple procedures.

Total runtime 1223506 ms.

ITS solved all properties within timeout

BK_STOP 1717254623170

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202405141337.jar

+ VERSION=202405141337

+ echo 'Running Version 202405141337'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination LTLFireability -timeout 360 -rebuildPNML

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="AirplaneLD-PT-4000"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="ltsminxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool ltsminxred"

echo " Input is AirplaneLD-PT-4000, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r464-smll-171620118300308"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/AirplaneLD-PT-4000.tgz

mv AirplaneLD-PT-4000 execution

cd execution

if [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "UpperBounds" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] || [ "LTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME LTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;