About the Execution of 2023-gold for SmallOperatingSystem-PT-MT8192DC4096

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 404.243 | 13635.00 | 24033.00 | 331.10 | FFFFFFFFFTFFTFFT | normal |

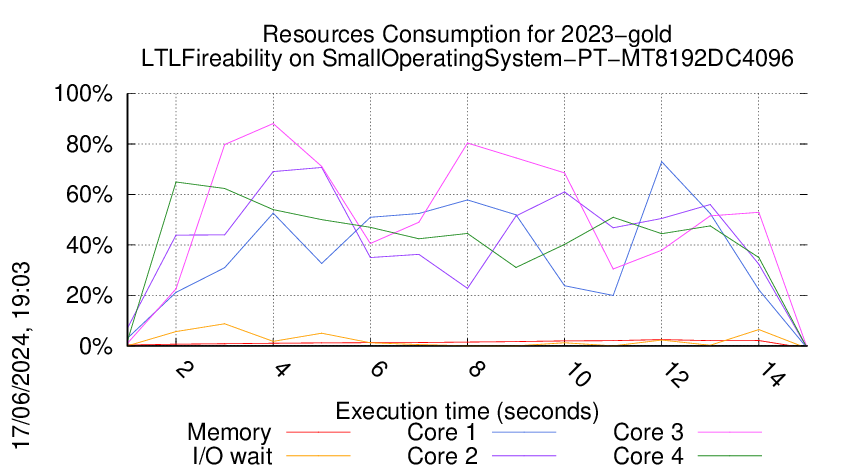

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r395-smll-171683824200208.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

......................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool gold2023

Input is SmallOperatingSystem-PT-MT8192DC4096, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r395-smll-171683824200208

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 492K

-rw-r--r-- 1 mcc users 11K May 14 13:22 CTLCardinality.txt

-rw-r--r-- 1 mcc users 95K May 14 13:22 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.0K May 14 13:22 CTLFireability.txt

-rw-r--r-- 1 mcc users 46K May 14 13:22 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:43 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.7K May 18 16:43 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.5K Apr 23 07:57 LTLCardinality.txt

-rw-r--r-- 1 mcc users 26K Apr 23 07:57 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.8K Apr 23 07:57 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Apr 23 07:57 LTLFireability.xml

-rw-r--r-- 1 mcc users 14K Apr 12 14:13 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 115K Apr 12 14:13 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 9.6K Apr 12 14:12 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 69K Apr 12 14:12 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.1K Apr 23 07:57 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Apr 23 07:57 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 18 16:43 equiv_col

-rw-r--r-- 1 mcc users 13 May 18 16:43 instance

-rw-r--r-- 1 mcc users 6 May 18 16:43 iscolored

-rw-r--r-- 1 mcc users 8.1K May 18 16:43 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-00

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-01

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-02

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-03

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-04

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-05

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-06

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-07

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-08

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-09

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-10

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-11

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-12

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-13

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-14

FORMULA_NAME SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1716974348538

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=gold2023

BK_EXAMINATION=LTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=SmallOperatingSystem-PT-MT8192DC4096

Not applying reductions.

Model is PT

LTLFireability PT

Running Version 202304061127

[2024-05-29 09:19:11] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2024-05-29 09:19:11] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-05-29 09:19:11] [INFO ] Load time of PNML (sax parser for PT used): 30 ms

[2024-05-29 09:19:11] [INFO ] Transformed 9 places.

[2024-05-29 09:19:11] [INFO ] Transformed 8 transitions.

[2024-05-29 09:19:11] [INFO ] Parsed PT model containing 9 places and 8 transitions and 27 arcs in 126 ms.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 12 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 5 formulas.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-00 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-01 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-04 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-09 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-11 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 8 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 12 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 9 cols

[2024-05-29 09:19:12] [INFO ] Computed 4 invariants in 5 ms

[2024-05-29 09:19:12] [INFO ] Implicit Places using invariants in 182 ms returned []

[2024-05-29 09:19:12] [INFO ] Invariant cache hit.

[2024-05-29 09:19:12] [INFO ] Implicit Places using invariants and state equation in 51 ms returned []

Implicit Place search using SMT with State Equation took 281 ms to find 0 implicit places.

[2024-05-29 09:19:12] [INFO ] Invariant cache hit.

[2024-05-29 09:19:12] [INFO ] Dead Transitions using invariants and state equation in 57 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 352 ms. Remains : 9/9 places, 8/8 transitions.

Support contains 8 out of 9 places after structural reductions.

[2024-05-29 09:19:12] [INFO ] Flatten gal took : 25 ms

[2024-05-29 09:19:12] [INFO ] Flatten gal took : 7 ms

[2024-05-29 09:19:12] [INFO ] Input system was already deterministic with 8 transitions.

Incomplete random walk after 12293 steps, including 2 resets, run finished after 56 ms. (steps per millisecond=219 ) properties (out of 8) seen :2

Finished Best-First random walk after 90 steps, including 0 resets, run visited all 6 properties in 4 ms. (steps per millisecond=22 )

Parikh walk visited 0 properties in 4 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-10 FALSE TECHNIQUES REACHABILITY_KNOWLEDGE

Computed a total of 0 stabilizing places and 0 stable transitions

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(p0)))'

Support contains 3 out of 9 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 2 places and 0 transitions.

Iterating global reduction 0 with 3 rules applied. Total rules applied 5 place count 6 transition count 6

Partial Post-agglomeration rule applied 1 times.

Drop transitions removed 1 transitions

Iterating global reduction 0 with 1 rules applied. Total rules applied 6 place count 6 transition count 6

Applied a total of 6 rules in 16 ms. Remains 6 /9 variables (removed 3) and now considering 6/8 (removed 2) transitions.

// Phase 1: matrix 6 rows 6 cols

[2024-05-29 09:19:13] [INFO ] Computed 3 invariants in 1 ms

[2024-05-29 09:19:13] [INFO ] Implicit Places using invariants in 30 ms returned []

[2024-05-29 09:19:13] [INFO ] Invariant cache hit.

[2024-05-29 09:19:13] [INFO ] State equation strengthened by 1 read => feed constraints.

[2024-05-29 09:19:13] [INFO ] Implicit Places using invariants and state equation in 57 ms returned []

Implicit Place search using SMT with State Equation took 91 ms to find 0 implicit places.

[2024-05-29 09:19:13] [INFO ] Redundant transitions in 0 ms returned []

[2024-05-29 09:19:13] [INFO ] Invariant cache hit.

[2024-05-29 09:19:13] [INFO ] Dead Transitions using invariants and state equation in 37 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 6/9 places, 6/8 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 155 ms. Remains : 6/9 places, 6/8 transitions.

ANTLR Tool version 4.9.3 used for code generation does not match the current runtime version 4.7.2ANTLR Runtime version 4.9.3 used for parser compilation does not match the current runtime version 4.7.2ANTLR Tool version 4.9.3 used for code generation does not match the current runtime version 4.7.2ANTLR Runtime version 4.9.3 used for parser compilation does not match the current runtime version 4.7.2Stuttering acceptance computed with spot in 261 ms :[(NOT p0)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-02 automaton TGBA Formula[mat=[[{ cond=p0, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={0} source=0 dest: 0}]], initial=0, aps=[p0:(OR (LT s0 1) (LT s1 1) (LT s2 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, complete, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-invariant], stateDesc=[null][true]]

Stuttering criterion allowed to conclude after 11 steps with 0 reset in 3 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-02 FALSE TECHNIQUES STUTTER_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-02 finished in 513 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(((X(p1)||F(p2))&&p0)))'

Support contains 3 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 1 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 8 cols

[2024-05-29 09:19:13] [INFO ] Computed 3 invariants in 1 ms

[2024-05-29 09:19:13] [INFO ] Implicit Places using invariants in 41 ms returned []

[2024-05-29 09:19:13] [INFO ] Invariant cache hit.

[2024-05-29 09:19:13] [INFO ] Implicit Places using invariants and state equation in 51 ms returned []

Implicit Place search using SMT with State Equation took 95 ms to find 0 implicit places.

[2024-05-29 09:19:13] [INFO ] Invariant cache hit.

[2024-05-29 09:19:14] [INFO ] Dead Transitions using invariants and state equation in 51 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 8/9 places, 8/8 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 151 ms. Remains : 8/9 places, 8/8 transitions.

Stuttering acceptance computed with spot in 203 ms :[(OR (AND (NOT p0) (NOT p2)) (AND (NOT p1) (NOT p2))), (OR (NOT p0) (AND (NOT p1) (NOT p2))), (AND (NOT p1) (NOT p2))]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-03 automaton TGBA Formula[mat=[[{ cond=(AND (NOT p0) (NOT p2)), acceptance={0} source=0 dest: 0}, { cond=(AND p0 (NOT p2)), acceptance={0} source=0 dest: 2}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}, { cond=(AND p0 (NOT p2)), acceptance={0} source=1 dest: 2}], [{ cond=(AND (NOT p0) (NOT p2) (NOT p1)), acceptance={0} source=2 dest: 0}, { cond=(AND p0 (NOT p2) (NOT p1)), acceptance={0} source=2 dest: 2}]], initial=1, aps=[p0:(AND (GEQ s3 1) (GEQ s5 1)), p2:(GEQ s2 1), p1:(AND (GEQ s3 1) (GEQ s5 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, colored, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, weak, inherently-weak], stateDesc=[null, null, null][false, false, false]]

Product exploration explored 100000 steps with 11615 reset in 539 ms.

Stack based approach found an accepted trace after 51 steps with 6 reset with depth 6 and stack size 6 in 2 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-03 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-03 finished in 934 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((!p0 U p1))'

Support contains 5 out of 9 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Applied a total of 2 rules in 4 ms. Remains 8 /9 variables (removed 1) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 8 cols

[2024-05-29 09:19:14] [INFO ] Computed 4 invariants in 0 ms

[2024-05-29 09:19:14] [INFO ] Implicit Places using invariants in 33 ms returned []

[2024-05-29 09:19:14] [INFO ] Invariant cache hit.

[2024-05-29 09:19:14] [INFO ] Implicit Places using invariants and state equation in 39 ms returned []

Implicit Place search using SMT with State Equation took 77 ms to find 0 implicit places.

[2024-05-29 09:19:14] [INFO ] Redundant transitions in 0 ms returned []

[2024-05-29 09:19:14] [INFO ] Invariant cache hit.

[2024-05-29 09:19:14] [INFO ] Dead Transitions using invariants and state equation in 39 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 8/9 places, 7/8 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 130 ms. Remains : 8/9 places, 7/8 transitions.

Stuttering acceptance computed with spot in 85 ms :[true, (NOT p1)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-05 automaton TGBA Formula[mat=[[{ cond=true, acceptance={0} source=0 dest: 0}], [{ cond=(AND (NOT p1) p0), acceptance={0} source=1 dest: 0}, { cond=(AND (NOT p1) (NOT p0)), acceptance={0} source=1 dest: 1}]], initial=1, aps=[p1:(AND (GEQ s5 1) (GEQ s6 1)), p0:(OR (LT s0 1) (LT s1 1) (LT s2 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, colored, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-invariant, very-weak, weak, inherently-weak], stateDesc=[null, null][true, true]]

Product exploration explored 100000 steps with 7787 reset in 311 ms.

Stack based approach found an accepted trace after 7 steps with 0 reset with depth 8 and stack size 8 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-05 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-05 finished in 547 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(F((F(!(p0 U p1))&&F(X(G(F(p0))))))))'

Support contains 2 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 1 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 8 cols

[2024-05-29 09:19:15] [INFO ] Computed 3 invariants in 3 ms

[2024-05-29 09:19:15] [INFO ] Implicit Places using invariants in 43 ms returned [5]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 47 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 7/9 places, 8/8 transitions.

Applied a total of 0 rules in 0 ms. Remains 7 /7 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 52 ms. Remains : 7/9 places, 8/8 transitions.

Stuttering acceptance computed with spot in 282 ms :[(OR (NOT p0) p1), (OR (NOT p0) p1), p1, (NOT p0), (NOT p0)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-06 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 1}], [{ cond=(OR p0 p1), acceptance={} source=1 dest: 2}, { cond=(NOT p0), acceptance={} source=1 dest: 3}, { cond=true, acceptance={} source=1 dest: 4}], [{ cond=(AND p0 (NOT p1)), acceptance={} source=2 dest: 2}, { cond=p1, acceptance={0} source=2 dest: 2}], [{ cond=(NOT p0), acceptance={0} source=3 dest: 3}], [{ cond=(NOT p0), acceptance={} source=4 dest: 3}, { cond=true, acceptance={} source=4 dest: 4}]], initial=0, aps=[p0:(GEQ s6 1), p1:(GEQ s2 1)], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-sensitive], stateDesc=[null, null, null, null, null][false, false, false, false, false]]

Product exploration explored 100000 steps with 23 reset in 228 ms.

Stack based approach found an accepted trace after 33 steps with 3 reset with depth 16 and stack size 12 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-06 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-06 finished in 596 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G((F(p0)&&F(!p1))))'

Support contains 4 out of 9 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Applied a total of 2 rules in 3 ms. Remains 8 /9 variables (removed 1) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 8 cols

[2024-05-29 09:19:15] [INFO ] Computed 4 invariants in 1 ms

[2024-05-29 09:19:15] [INFO ] Implicit Places using invariants in 28 ms returned [6]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 32 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 7/9 places, 7/8 transitions.

Partial Post-agglomeration rule applied 1 times.

Drop transitions removed 1 transitions

Iterating global reduction 0 with 1 rules applied. Total rules applied 1 place count 7 transition count 7

Applied a total of 1 rules in 1 ms. Remains 7 /7 variables (removed 0) and now considering 7/7 (removed 0) transitions.

// Phase 1: matrix 7 rows 7 cols

[2024-05-29 09:19:15] [INFO ] Computed 3 invariants in 0 ms

[2024-05-29 09:19:15] [INFO ] Implicit Places using invariants in 20 ms returned []

[2024-05-29 09:19:15] [INFO ] Invariant cache hit.

[2024-05-29 09:19:16] [INFO ] Implicit Places using invariants and state equation in 32 ms returned []

Implicit Place search using SMT with State Equation took 53 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 7/9 places, 7/8 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 90 ms. Remains : 7/9 places, 7/8 transitions.

Stuttering acceptance computed with spot in 103 ms :[(OR (NOT p0) p1), (NOT p0), p1]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-07 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={} source=0 dest: 1}, { cond=p1, acceptance={} source=0 dest: 2}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}], [{ cond=p1, acceptance={0} source=2 dest: 2}]], initial=0, aps=[p0:(AND (GEQ s0 1) (GEQ s2 1) (GEQ s5 1)), p1:(OR (LT s0 1) (LT s1 1) (LT s2 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-invariant, very-weak, weak, inherently-weak], stateDesc=[null, null, null][true, true, true]]

Product exploration explored 100000 steps with 10199 reset in 140 ms.

Stack based approach found an accepted trace after 5 steps with 0 reset with depth 6 and stack size 6 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-07 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-07 finished in 354 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(F(p0)))'

Support contains 1 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Applied a total of 1 rules in 1 ms. Remains 8 /9 variables (removed 1) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 8 cols

[2024-05-29 09:19:16] [INFO ] Computed 3 invariants in 1 ms

[2024-05-29 09:19:16] [INFO ] Implicit Places using invariants in 42 ms returned [5]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 43 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 7/9 places, 8/8 transitions.

Applied a total of 0 rules in 1 ms. Remains 7 /7 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 45 ms. Remains : 7/9 places, 8/8 transitions.

Stuttering acceptance computed with spot in 122 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-08 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 1}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p0:(GEQ s2 1)], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null][false, false]]

Product exploration explored 100000 steps with 4858 reset in 123 ms.

Stack based approach found an accepted trace after 11 steps with 0 reset with depth 12 and stack size 12 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-08 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-08 finished in 311 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(X((!X(p0) U (p1 U p1)))))'

Support contains 1 out of 9 places. Attempting structural reductions.

Property had overlarge support with respect to TGBA, discarding it for now.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 8

Discarding 1 places :

Symmetric choice reduction at 1 with 1 rule applications. Total rules 2 place count 7 transition count 7

Iterating global reduction 1 with 1 rules applied. Total rules applied 3 place count 7 transition count 7

Applied a total of 3 rules in 1 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 7 cols

[2024-05-29 09:19:16] [INFO ] Computed 3 invariants in 0 ms

[2024-05-29 09:19:16] [INFO ] Implicit Places using invariants in 33 ms returned []

[2024-05-29 09:19:16] [INFO ] Invariant cache hit.

[2024-05-29 09:19:16] [INFO ] Implicit Places using invariants and state equation in 57 ms returned []

Implicit Place search using SMT with State Equation took 96 ms to find 0 implicit places.

[2024-05-29 09:19:16] [INFO ] Invariant cache hit.

[2024-05-29 09:19:16] [INFO ] Dead Transitions using invariants and state equation in 26 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 7/9 places, 7/8 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 125 ms. Remains : 7/9 places, 7/8 transitions.

Stuttering acceptance computed with spot in 71 ms :[(NOT p1), (NOT p1)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-12 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 1}], [{ cond=(NOT p1), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p1:(GEQ s3 1)], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null][false, false]]

Product exploration explored 100000 steps with 25005 reset in 56 ms.

Product exploration explored 100000 steps with 24931 reset in 99 ms.

Computed a total of 0 stabilizing places and 0 stable transitions

Computed a total of 0 stabilizing places and 0 stable transitions

Knowledge obtained : [(NOT p1), (X (NOT p1))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1))]

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 2 factoid took 185 ms. Reduced automaton from 2 states, 2 edges and 1 AP (stutter sensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 34 ms :[(NOT p1)]

Incomplete random walk after 12293 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=1756 ) properties (out of 1) seen :0

Finished Best-First random walk after 4 steps, including 0 resets, run visited all 1 properties in 1 ms. (steps per millisecond=4 )

Parikh walk visited 0 properties in 0 ms.

Knowledge obtained : [(NOT p1), (X (NOT p1))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1)), (F p1)]

Knowledge based reduction with 2 factoid took 210 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 50 ms :[(NOT p1)]

Stuttering acceptance computed with spot in 51 ms :[(NOT p1)]

[2024-05-29 09:19:17] [INFO ] Invariant cache hit.

[2024-05-29 09:19:17] [INFO ] [Real]Absence check using 3 positive place invariants in 2 ms returned sat

[2024-05-29 09:19:17] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2024-05-29 09:19:17] [INFO ] [Real]Absence check using state equation in 13 ms returned sat

[2024-05-29 09:19:17] [INFO ] Computed and/alt/rep : 6/8/6 causal constraints (skipped 0 transitions) in 5 ms.

[2024-05-29 09:19:17] [INFO ] Added : 0 causal constraints over 0 iterations in 22 ms. Result :sat

Could not prove EG (NOT p1)

Support contains 1 out of 7 places. Attempting structural reductions.

Property had overlarge support with respect to TGBA, discarding it for now.

Starting structural reductions in SI_LTL mode, iteration 0 : 7/7 places, 7/7 transitions.

Applied a total of 0 rules in 1 ms. Remains 7 /7 variables (removed 0) and now considering 7/7 (removed 0) transitions.

[2024-05-29 09:19:17] [INFO ] Invariant cache hit.

[2024-05-29 09:19:17] [INFO ] Implicit Places using invariants in 33 ms returned []

[2024-05-29 09:19:17] [INFO ] Invariant cache hit.

[2024-05-29 09:19:17] [INFO ] Implicit Places using invariants and state equation in 42 ms returned []

Implicit Place search using SMT with State Equation took 77 ms to find 0 implicit places.

[2024-05-29 09:19:17] [INFO ] Redundant transitions in 0 ms returned []

[2024-05-29 09:19:17] [INFO ] Invariant cache hit.

[2024-05-29 09:19:17] [INFO ] Dead Transitions using invariants and state equation in 45 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 134 ms. Remains : 7/7 places, 7/7 transitions.

Computed a total of 0 stabilizing places and 0 stable transitions

Computed a total of 0 stabilizing places and 0 stable transitions

Knowledge obtained : [(NOT p1), (X (NOT p1))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1))]

Knowledge based reduction with 2 factoid took 176 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 50 ms :[(NOT p1)]

Incomplete random walk after 12293 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=1756 ) properties (out of 1) seen :0

Finished Best-First random walk after 4 steps, including 0 resets, run visited all 1 properties in 2 ms. (steps per millisecond=2 )

Parikh walk visited 0 properties in 0 ms.

Knowledge obtained : [(NOT p1), (X (NOT p1))]

False Knowledge obtained : [(X (X (NOT p1))), (X (X p1)), (F p1)]

Knowledge based reduction with 2 factoid took 198 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 49 ms :[(NOT p1)]

Stuttering acceptance computed with spot in 49 ms :[(NOT p1)]

[2024-05-29 09:19:18] [INFO ] Invariant cache hit.

[2024-05-29 09:19:18] [INFO ] [Real]Absence check using 3 positive place invariants in 2 ms returned sat

[2024-05-29 09:19:18] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2024-05-29 09:19:18] [INFO ] [Real]Absence check using state equation in 20 ms returned sat

[2024-05-29 09:19:18] [INFO ] Computed and/alt/rep : 6/8/6 causal constraints (skipped 0 transitions) in 3 ms.

[2024-05-29 09:19:18] [INFO ] Added : 0 causal constraints over 0 iterations in 11 ms. Result :sat

Could not prove EG (NOT p1)

Stuttering acceptance computed with spot in 50 ms :[(NOT p1)]

Product exploration explored 100000 steps with 24979 reset in 170 ms.

Product exploration explored 100000 steps with 24901 reset in 105 ms.

Built C files in :

/tmp/ltsmin14015394519401140334

[2024-05-29 09:19:18] [INFO ] Computing symmetric may disable matrix : 7 transitions.

[2024-05-29 09:19:18] [INFO ] Computation of Complete disable matrix. took 1 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2024-05-29 09:19:18] [INFO ] Computing symmetric may enable matrix : 7 transitions.

[2024-05-29 09:19:18] [INFO ] Computation of Complete enable matrix. took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2024-05-29 09:19:18] [INFO ] Computing Do-Not-Accords matrix : 7 transitions.

[2024-05-29 09:19:18] [INFO ] Computation of Completed DNA matrix. took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2024-05-29 09:19:18] [INFO ] Built C files in 9ms conformant to PINS (ltsmin variant)in folder :/tmp/ltsmin14015394519401140334

Running compilation step : cd /tmp/ltsmin14015394519401140334;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202304061127/bin/limit_time.pl' '3' 'gcc' '-c' '-I/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202304061127/bin/include/' '-I.' '-std=c99' '-fPIC' '-O0' 'model.c'

Compilation finished in 354 ms.

Running link step : cd /tmp/ltsmin14015394519401140334;'gcc' '-shared' '-o' 'gal.so' 'model.o'

Link finished in 62 ms.

Running LTSmin : cd /tmp/ltsmin14015394519401140334;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202304061127/bin/pins2lts-mc-linux64' './gal.so' '--threads=8' '-p' '--pins-guards' '--when' '--hoa' '/tmp/stateBased810257312059713341.hoa' '--buchi-type=spotba'

LTSmin run took 668 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-12 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-12 finished in 3302 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(G(p0)))'

Support contains 3 out of 9 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 8 transition count 7

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 8 transition count 7

Applied a total of 2 rules in 2 ms. Remains 8 /9 variables (removed 1) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 8 cols

[2024-05-29 09:19:19] [INFO ] Computed 4 invariants in 1 ms

[2024-05-29 09:19:19] [INFO ] Implicit Places using invariants in 31 ms returned [6]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 33 ms to find 1 implicit places.

Starting structural reductions in SI_LTL mode, iteration 1 : 7/9 places, 7/8 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 0 with 2 rules applied. Total rules applied 2 place count 6 transition count 6

Applied a total of 2 rules in 2 ms. Remains 6 /7 variables (removed 1) and now considering 6/7 (removed 1) transitions.

// Phase 1: matrix 6 rows 6 cols

[2024-05-29 09:19:19] [INFO ] Computed 3 invariants in 1 ms

[2024-05-29 09:19:19] [INFO ] Implicit Places using invariants in 27 ms returned []

[2024-05-29 09:19:19] [INFO ] Invariant cache hit.

[2024-05-29 09:19:19] [INFO ] Implicit Places using invariants and state equation in 36 ms returned []

Implicit Place search using SMT with State Equation took 65 ms to find 0 implicit places.

Starting structural reductions in SI_LTL mode, iteration 2 : 6/9 places, 6/8 transitions.

Finished structural reductions in SI_LTL mode , in 2 iterations and 102 ms. Remains : 6/9 places, 6/8 transitions.

Stuttering acceptance computed with spot in 50 ms :[(NOT p0)]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-13 automaton TGBA Formula[mat=[[{ cond=p0, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={0} source=0 dest: 0}]], initial=0, aps=[p0:(AND (GEQ s0 1) (GEQ s2 1) (GEQ s4 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, complete, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-invariant], stateDesc=[null][true]]

Product exploration explored 100000 steps with 0 reset in 153 ms.

Stack based approach found an accepted trace after 1 steps with 0 reset with depth 2 and stack size 2 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-13 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-13 finished in 327 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F((G(p0)||G(p1))))'

Support contains 3 out of 9 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Ensure Unique test removed 1 places

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Iterating post reduction 0 with 1 rules applied. Total rules applied 1 place count 8 transition count 7

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 1 with 1 rules applied. Total rules applied 2 place count 7 transition count 7

Applied a total of 2 rules in 3 ms. Remains 7 /9 variables (removed 2) and now considering 7/8 (removed 1) transitions.

// Phase 1: matrix 7 rows 7 cols

[2024-05-29 09:19:20] [INFO ] Computed 3 invariants in 1 ms

[2024-05-29 09:19:20] [INFO ] Implicit Places using invariants in 37 ms returned []

[2024-05-29 09:19:20] [INFO ] Invariant cache hit.

[2024-05-29 09:19:20] [INFO ] Implicit Places using invariants and state equation in 39 ms returned []

Implicit Place search using SMT with State Equation took 79 ms to find 0 implicit places.

[2024-05-29 09:19:20] [INFO ] Redundant transitions in 0 ms returned []

[2024-05-29 09:19:20] [INFO ] Invariant cache hit.

[2024-05-29 09:19:20] [INFO ] Dead Transitions using invariants and state equation in 49 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 7/9 places, 7/8 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 140 ms. Remains : 7/9 places, 7/8 transitions.

Stuttering acceptance computed with spot in 57 ms :[(AND (NOT p0) (NOT p1))]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-14 automaton TGBA Formula[mat=[[{ cond=(AND p0 p1), acceptance={} source=0 dest: 0}, { cond=(AND (NOT p0) p1), acceptance={0} source=0 dest: 0}, { cond=(AND p0 (NOT p1)), acceptance={1} source=0 dest: 0}, { cond=(AND (NOT p0) (NOT p1)), acceptance={0, 1} source=0 dest: 0}]], initial=0, aps=[p0:(AND (GEQ s3 1) (GEQ s4 1)), p1:(GEQ s6 1)], nbAcceptance=2, properties=[trans-labels, explicit-labels, trans-acc, complete, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-invariant], stateDesc=[null][true]]

Product exploration explored 100000 steps with 0 reset in 196 ms.

Stack based approach found an accepted trace after 2 steps with 0 reset with depth 3 and stack size 3 in 0 ms.

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-14 FALSE TECHNIQUES STACK_TEST

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-14 finished in 416 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202304061127/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(((p0||X(X(X(G(!p1))))) U X(p2)))'

Support contains 5 out of 9 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 9/9 places, 8/8 transitions.

Applied a total of 0 rules in 1 ms. Remains 9 /9 variables (removed 0) and now considering 8/8 (removed 0) transitions.

// Phase 1: matrix 8 rows 9 cols

[2024-05-29 09:19:20] [INFO ] Computed 4 invariants in 1 ms

[2024-05-29 09:19:20] [INFO ] Implicit Places using invariants in 41 ms returned [6]

Discarding 1 places :

Implicit Place search using SMT only with invariants took 43 ms to find 1 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 8/9 places, 8/8 transitions.

Applied a total of 0 rules in 1 ms. Remains 8 /8 variables (removed 0) and now considering 8/8 (removed 0) transitions.

Finished structural reductions in LTL mode , in 2 iterations and 45 ms. Remains : 8/9 places, 8/8 transitions.

Stuttering acceptance computed with spot in 306 ms :[(NOT p2), (AND (NOT p2) p1), (NOT p2), p1, p1, true]

Running random walk in product with property : SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-15 automaton TGBA Formula[mat=[[{ cond=(NOT p0), acceptance={} source=0 dest: 1}, { cond=true, acceptance={} source=0 dest: 2}], [{ cond=(NOT p2), acceptance={} source=1 dest: 3}], [{ cond=(AND (NOT p0) (NOT p2)), acceptance={0} source=2 dest: 1}, { cond=(NOT p2), acceptance={0} source=2 dest: 2}], [{ cond=true, acceptance={} source=3 dest: 4}], [{ cond=(NOT p1), acceptance={} source=4 dest: 4}, { cond=p1, acceptance={} source=4 dest: 5}], [{ cond=true, acceptance={0} source=5 dest: 5}]], initial=0, aps=[p0:(GEQ s3 1), p2:(GEQ s7 1), p1:(OR (LT s0 1) (LT s1 1) (LT s2 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null, null][false, false, false, false, false, false]]

Product exploration explored 100000 steps with 50000 reset in 73 ms.

Product exploration explored 100000 steps with 50000 reset in 107 ms.

Computed a total of 0 stabilizing places and 0 stable transitions

Computed a total of 0 stabilizing places and 0 stable transitions

Knowledge obtained : [(AND (NOT p0) (NOT p2) (NOT p1)), (X (NOT (AND (NOT p0) (NOT p2)))), (X p2), true]

False Knowledge obtained : [(X (X (AND (NOT p0) (NOT p2)))), (X (X (NOT (AND (NOT p0) (NOT p2))))), (X (X (NOT p2))), (X (X p2))]

Property proved to be true thanks to knowledge (Minato strategy)

Knowledge based reduction with 4 factoid took 20 ms. Reduced automaton from 6 states, 9 edges and 3 AP (stutter sensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-15 TRUE TECHNIQUES KNOWLEDGE

Treatment of property SmallOperatingSystem-PT-MT8192DC4096-LTLFireability-15 finished in 588 ms.

All properties solved by simple procedures.

Total runtime 9480 ms.

BK_STOP 1716974362173

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ LTLFireability = StateSpace ]]

+ /home/mcc/BenchKit/bin//../itstools/bin//..//runeclipse.sh /home/mcc/execution LTLFireability -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202304061127.jar

+ VERSION=202304061127

+ echo 'Running Version 202304061127'

+ /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/its-tools -pnfolder /home/mcc/execution -examination LTLFireability -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="SmallOperatingSystem-PT-MT8192DC4096"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="gold2023"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool gold2023"

echo " Input is SmallOperatingSystem-PT-MT8192DC4096, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r395-smll-171683824200208"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/SmallOperatingSystem-PT-MT8192DC4096.tgz

mv SmallOperatingSystem-PT-MT8192DC4096 execution

cd execution

if [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "UpperBounds" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] || [ "LTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME LTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;