About the Execution of Tapaal for ParamProductionCell-PT-5

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 4216.336 | 290285.00 | 1146305.00 | 55.10 | FFFFTFTTTFFFTFTF | normal |

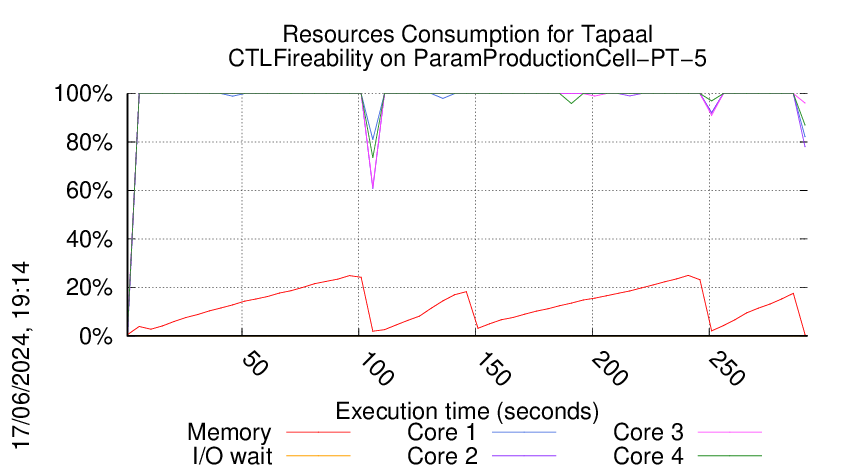

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r272-smll-171654411800050.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool tapaal

Input is ParamProductionCell-PT-5, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r272-smll-171654411800050

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 608K

-rw-r--r-- 1 mcc users 7.0K May 14 13:22 CTLCardinality.txt

-rw-r--r-- 1 mcc users 60K May 14 13:22 CTLCardinality.xml

-rw-r--r-- 1 mcc users 7.4K May 14 13:22 CTLFireability.txt

-rw-r--r-- 1 mcc users 59K May 14 13:22 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:43 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.2K May 18 16:43 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.6K Apr 23 07:41 LTLCardinality.txt

-rw-r--r-- 1 mcc users 28K Apr 23 07:41 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K Apr 23 07:41 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Apr 23 07:41 LTLFireability.xml

-rw-r--r-- 1 mcc users 15K Apr 12 20:33 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 125K Apr 12 20:33 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 7.8K Apr 12 20:31 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 48K Apr 12 20:31 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.9K Apr 23 07:41 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.9K Apr 23 07:41 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 18 16:43 equiv_col

-rw-r--r-- 1 mcc users 2 May 18 16:43 instance

-rw-r--r-- 1 mcc users 6 May 18 16:43 iscolored

-rw-r--r-- 1 mcc users 174K May 18 16:43 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-00

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-01

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-02

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-03

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-04

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-05

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-06

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-07

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-08

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-09

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-10

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2024-11

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2023-12

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2023-13

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2023-14

FORMULA_NAME ParamProductionCell-PT-5-CTLFireability-2023-15

=== Now, execution of the tool begins

BK_START 1716714471239

tapaal

Got BK_BIN_PATH=/home/mcc/BenchKit/bin/

---> tapaal --- TAPAAL - v2.2024

Setting MODEL_PATH=.

Setting VERIFYPN=/home/mcc/BenchKit/bin/verifypn

Got BK_TIME_CONFINEMENT=3600

Setting TEMPDIR=/home/mcc/BenchKit/bin/tmp

Got BK_MEMORY_CONFINEMENT=16384

Limiting to 16265216 kB

Total timeout: 3590

Time left: 3590

*************************************

* TAPAAL verifying CTLFireability *

*************************************

TEMPDIR=/home/mcc/BenchKit/bin/tmp

QF=/home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26

MF=/home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii

Time left: 3590

---------------------------------------------------

Step -1: Stripping Colors

---------------------------------------------------

Verifying stripped models (16 in total)

Time left: 3590

---------------------------------------------------

Step 0: Parallel Simplification

---------------------------------------------------

Doing parallel simplification (16 in total)

Total simplification timout is 718 -- reduction timeout is 299

timeout 3590 /home/mcc/BenchKit/bin/verifypn -n -q 718 -l 29 -d 299 -z 4 -s OverApprox --binary-query-io 2 --write-simplified /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --write-reduced /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Time left: 3590

---------------------------------------------------

Step 1: Parallel processing

---------------------------------------------------

Doing parallel verification of individual queries (16 in total)

Each query is verified by 4 parallel strategies for 299 seconds

------------------- QUERY 1 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.187587 on verification

@@@0.19,59508@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BestFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 1 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-01 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3589

------------------- QUERY 2 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.02949 on verification

@@@0.03,57204@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BestFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 2 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2023-12 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3589

------------------- QUERY 3 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 5.42823 on verification

@@@5.47,209220@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 3 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3583

------------------- QUERY 4 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 96.5427 on verification

@@@96.66,1138284@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s DFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 4 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-04 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3486

------------------- QUERY 5 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.049112 on verification

@@@0.05,57632@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BestFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 5 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-07 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3486

------------------- QUERY 6 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 1.22786 on verification

@@@1.24,65656@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s DFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 6 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-00 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3485

------------------- QUERY 7 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.079205 on verification

@@@0.08,58036@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s RPFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 7 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-05 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3484

------------------- QUERY 8 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.105258 on verification

@@@0.12,58020@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s RPFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 8 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-11 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3484

------------------- QUERY 9 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.063751 on verification

@@@0.07,57692@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s RPFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 9 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2023-14 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3483

------------------- QUERY 10 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 38.8402 on verification

@@@38.91,912804@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s DFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 10 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-03 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3444

------------------- QUERY 11 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 99.0749 on verification

@@@99.16,1382728@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s DFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 11 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2023-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3345

------------------- QUERY 12 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 1.57519 on verification

@@@1.58,72628@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BestFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 12 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-09 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3343

------------------- QUERY 13 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.049532 on verification

@@@0.05,57644@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BestFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 13 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-08 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3343

------------------- QUERY 14 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.901495 on verification

@@@0.92,67872@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s BFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 14 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-02 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3341

------------------- QUERY 15 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 40.6101 on verification

@@@40.68,995796@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s DFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 15 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2023-13 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3300

------------------- QUERY 16 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.142119 on verification

@@@0.15,58880@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n '-s RPFS -q 0 -l 0 -d 119' /home/mcc/BenchKit/bin/tmp/tmp.qGRHMzW6Ii /home/mcc/BenchKit/bin/tmp/tmp.L5Dvvk7a26 --binary-query-io 1 -x 16 -n

FORMULA ParamProductionCell-PT-5-CTLFireability-2024-06 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3300

All queries are solved

Time left: 3300

terminated-with-cleanup

BK_STOP 1716714761524

--------------------

content from stderr:

CPN OverApproximation is only usable on colored models

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ParamProductionCell-PT-5"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="tapaal"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool tapaal"

echo " Input is ParamProductionCell-PT-5, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r272-smll-171654411800050"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ParamProductionCell-PT-5.tgz

mv ParamProductionCell-PT-5 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;