About the Execution of ITS-Tools for FamilyReunion-PT-L00020M0002C001P001G001

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 788.632 | 15730.00 | 45170.00 | 144.70 | FTTTFFFFTTTTTFTF | normal |

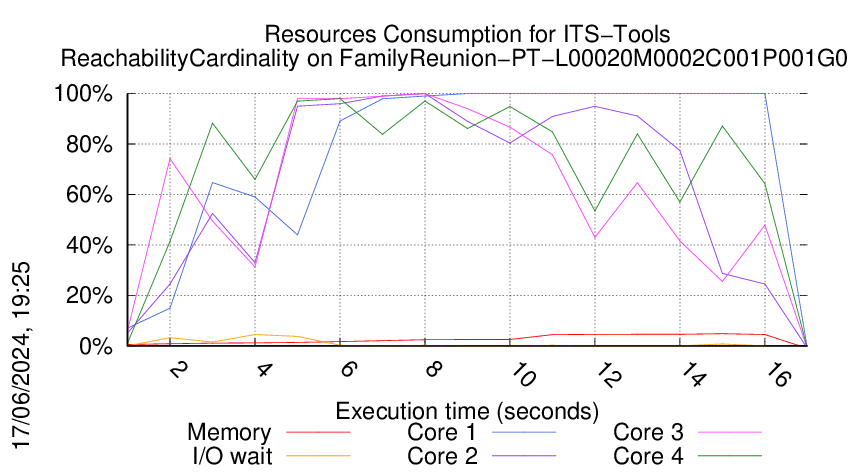

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r158-smll-171636267000494.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

..............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool itstools

Input is FamilyReunion-PT-L00020M0002C001P001G001, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r158-smll-171636267000494

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 3.2M

-rw-r--r-- 1 mcc users 33K Apr 11 20:27 CTLCardinality.txt

-rw-r--r-- 1 mcc users 233K Apr 11 20:27 CTLCardinality.xml

-rw-r--r-- 1 mcc users 50K Apr 11 20:19 CTLFireability.txt

-rw-r--r-- 1 mcc users 195K Apr 11 20:19 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:42 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 7.0K May 18 16:42 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 22K Apr 22 14:44 LTLCardinality.txt

-rw-r--r-- 1 mcc users 104K Apr 22 14:44 LTLCardinality.xml

-rw-r--r-- 1 mcc users 28K Apr 22 14:44 LTLFireability.txt

-rw-r--r-- 1 mcc users 79K Apr 22 14:44 LTLFireability.xml

-rw-r--r-- 1 mcc users 64K Apr 11 20:42 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 436K Apr 11 20:42 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 149K Apr 11 20:36 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 568K Apr 11 20:36 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 3.9K Apr 22 14:44 UpperBounds.txt

-rw-r--r-- 1 mcc users 11K Apr 22 14:44 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 18 16:42 equiv_col

-rw-r--r-- 1 mcc users 24 May 18 16:42 instance

-rw-r--r-- 1 mcc users 6 May 18 16:42 iscolored

-rw-r--r-- 1 mcc users 1.3M May 18 16:42 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-00

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-01

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-02

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-03

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-04

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-05

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-06

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-07

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-08

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-09

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-10

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-11

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-12

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-13

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-14

FORMULA_NAME FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-15

=== Now, execution of the tool begins

BK_START 1716688857919

Invoking MCC driver with

BK_TOOL=itstools

BK_EXAMINATION=ReachabilityCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=FamilyReunion-PT-L00020M0002C001P001G001

BK_MEMORY_CONFINEMENT=16384

Not applying reductions.

Model is PT

ReachabilityCardinality PT

Running Version 202405141337

[2024-05-26 02:01:00] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2024-05-26 02:01:00] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-05-26 02:01:01] [INFO ] Load time of PNML (sax parser for PT used): 640 ms

[2024-05-26 02:01:01] [INFO ] Transformed 3271 places.

[2024-05-26 02:01:01] [INFO ] Transformed 2753 transitions.

[2024-05-26 02:01:01] [INFO ] Parsed PT model containing 3271 places and 2753 transitions and 8446 arcs in 918 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 87 ms.

Working with output stream class java.io.PrintStream

Reduce places removed 11 places and 0 transitions.

RANDOM walk for 40000 steps (32 resets) in 5337 ms. (7 steps per ms) remains 8/16 properties

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-14 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-12 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-10 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-09 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-08 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-06 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-04 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-02 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

BEST_FIRST walk for 40003 steps (8 resets) in 454 ms. (87 steps per ms) remains 8/8 properties

[2024-05-26 02:01:03] [INFO ] Flatten gal took : 841 ms

BEST_FIRST walk for 40003 steps (8 resets) in 621 ms. (64 steps per ms) remains 8/8 properties

[2024-05-26 02:01:04] [INFO ] Flatten gal took : 323 ms

BEST_FIRST walk for 40004 steps (8 resets) in 1895 ms. (21 steps per ms) remains 8/8 properties

[2024-05-26 02:01:04] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality12299860862193120856.gal : 137 ms

[2024-05-26 02:01:04] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality5922437742357535730.prop : 12 ms

Invoking ITS tools like this :cd /home/mcc/execution;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202405141337/bin/its-reach-linux64' '--gc-threshold' '2000000' '--quiet' '-i' '/tmp/ReachabilityCardinality12299860862193120856.gal' '-t' 'CGAL' '-reachable-file' '/tmp/ReachabilityCardinality5922437742357535730.prop' '--nowitness' '--gen-order' 'FOLLOW'

its-reach command run as :

/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202405141337/bin/its-reach-linux64 --gc-threshold 2000000 --quiet ...329

Loading property file /tmp/ReachabilityCardinality5922437742357535730.prop.

BEST_FIRST walk for 40004 steps (8 resets) in 2999 ms. (13 steps per ms) remains 8/8 properties

BEST_FIRST walk for 40003 steps (8 resets) in 2006 ms. (19 steps per ms) remains 8/8 properties

BEST_FIRST walk for 40004 steps (8 resets) in 451 ms. (88 steps per ms) remains 8/8 properties

BEST_FIRST walk for 40003 steps (8 resets) in 171 ms. (232 steps per ms) remains 8/8 properties

BEST_FIRST walk for 40004 steps (8 resets) in 300 ms. (132 steps per ms) remains 8/8 properties

// Phase 1: matrix 2753 rows 3260 cols

[2024-05-26 02:01:06] [INFO ] Computed 748 invariants in 369 ms

All remaining problems are real, not stopping.

At refinement iteration 0 (INCLUDED_ONLY) 0/2496 variables, 212/212 constraints. Problems are: Problem set: 0 solved, 8 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/2496 variables, 0/212 constraints. Problems are: Problem set: 0 solved, 8 unsolved

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-11 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-11 TRUE TECHNIQUES SMT_REFINEMENT

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-15 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-15 FALSE TECHNIQUES SMT_REFINEMENT

At refinement iteration 2 (OVERLAPS) 444/2940 variables, 61/273 constraints. Problems are: Problem set: 2 solved, 6 unsolved

At refinement iteration 3 (INCLUDED_ONLY) 0/2940 variables, 255/528 constraints. Problems are: Problem set: 2 solved, 6 unsolved

At refinement iteration 4 (INCLUDED_ONLY) 0/2940 variables, 0/528 constraints. Problems are: Problem set: 2 solved, 6 unsolved

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-00 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-00 FALSE TECHNIQUES SMT_REFINEMENT

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-01 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-01 TRUE TECHNIQUES SMT_REFINEMENT

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-03 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-03 TRUE TECHNIQUES SMT_REFINEMENT

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-05 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-05 FALSE TECHNIQUES SMT_REFINEMENT

Problem FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-07 is UNSAT

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-07 FALSE TECHNIQUES SMT_REFINEMENT

At refinement iteration 5 (OVERLAPS) 320/3260 variables, 220/748 constraints. Problems are: Problem set: 7 solved, 1 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/3260 variables, 0/748 constraints. Problems are: Problem set: 7 solved, 1 unsolved

SMT process timed out in 6710ms, After SMT, problems are : Problem set: 7 solved, 1 unsolved

Skipping Parikh replay, no witness traces provided.

Support contains 24 out of 3260 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 3260/3260 places, 2753/2753 transitions.

Graph (complete) has 4960 edges and 3260 vertex of which 2934 are kept as prefixes of interest. Removing 326 places using SCC suffix rule.12 ms

Discarding 326 places :

Also discarding 232 output transitions

Drop transitions (Output transitions of discarded places.) removed 232 transitions

Drop transitions (Empty/Sink Transition effects.) removed 41 transitions

Reduce isomorphic transitions removed 41 transitions.

Discarding 376 places :

Implicit places reduction removed 376 places

Drop transitions (Trivial Post-Agglo cleanup.) removed 1220 transitions

Trivial Post-agglo rules discarded 1220 transitions

Performed 1220 trivial Post agglomeration. Transition count delta: 1220

Iterating post reduction 0 with 1637 rules applied. Total rules applied 1638 place count 2558 transition count 1260

Reduce places removed 1220 places and 0 transitions.

Performed 17 Post agglomeration using F-continuation condition.Transition count delta: 17

Iterating post reduction 1 with 1237 rules applied. Total rules applied 2875 place count 1338 transition count 1243

Reduce places removed 17 places and 0 transitions.

Iterating post reduction 2 with 17 rules applied. Total rules applied 2892 place count 1321 transition count 1243

Performed 206 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 206 Pre rules applied. Total rules applied 2892 place count 1321 transition count 1037

Deduced a syphon composed of 206 places in 2 ms

Ensure Unique test removed 104 places

Reduce places removed 310 places and 0 transitions.

Iterating global reduction 3 with 516 rules applied. Total rules applied 3408 place count 1011 transition count 1037

Discarding 3 places :

Implicit places reduction removed 3 places

Drop transitions (Trivial Post-Agglo cleanup.) removed 59 transitions

Trivial Post-agglo rules discarded 59 transitions

Performed 59 trivial Post agglomeration. Transition count delta: 59

Iterating post reduction 3 with 62 rules applied. Total rules applied 3470 place count 1008 transition count 978

Reduce places removed 59 places and 0 transitions.

Performed 2 Post agglomeration using F-continuation condition.Transition count delta: 2

Iterating post reduction 4 with 61 rules applied. Total rules applied 3531 place count 949 transition count 976

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 5 with 2 rules applied. Total rules applied 3533 place count 947 transition count 976

Discarding 208 places :

Symmetric choice reduction at 6 with 208 rule applications. Total rules 3741 place count 739 transition count 750

Iterating global reduction 6 with 208 rules applied. Total rules applied 3949 place count 739 transition count 750

Ensure Unique test removed 21 transitions

Reduce isomorphic transitions removed 21 transitions.

Discarding 42 places :

Implicit places reduction removed 42 places

Drop transitions (Trivial Post-Agglo cleanup.) removed 164 transitions

Trivial Post-agglo rules discarded 164 transitions

Performed 164 trivial Post agglomeration. Transition count delta: 164

Iterating post reduction 6 with 227 rules applied. Total rules applied 4176 place count 697 transition count 565

Reduce places removed 164 places and 0 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Iterating post reduction 7 with 165 rules applied. Total rules applied 4341 place count 533 transition count 564

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 8 with 1 rules applied. Total rules applied 4342 place count 532 transition count 564

Performed 6 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 9 with 6 Pre rules applied. Total rules applied 4342 place count 532 transition count 558

Deduced a syphon composed of 6 places in 1 ms

Reduce places removed 6 places and 0 transitions.

Iterating global reduction 9 with 12 rules applied. Total rules applied 4354 place count 526 transition count 558

Discarding 4 places :

Symmetric choice reduction at 9 with 4 rule applications. Total rules 4358 place count 522 transition count 513

Iterating global reduction 9 with 4 rules applied. Total rules applied 4362 place count 522 transition count 513

Ensure Unique test removed 19 transitions

Reduce isomorphic transitions removed 19 transitions.

Discarding 41 places :

Implicit places reduction removed 41 places

Drop transitions (Trivial Post-Agglo cleanup.) removed 39 transitions

Trivial Post-agglo rules discarded 39 transitions

Performed 39 trivial Post agglomeration. Transition count delta: 39

Iterating post reduction 9 with 99 rules applied. Total rules applied 4461 place count 481 transition count 455

Reduce places removed 39 places and 0 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Iterating post reduction 10 with 40 rules applied. Total rules applied 4501 place count 442 transition count 454

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 11 with 1 rules applied. Total rules applied 4502 place count 441 transition count 454

Performed 23 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 12 with 23 Pre rules applied. Total rules applied 4502 place count 441 transition count 431

Deduced a syphon composed of 23 places in 1 ms

Reduce places removed 23 places and 0 transitions.

Iterating global reduction 12 with 46 rules applied. Total rules applied 4548 place count 418 transition count 431

Discarding 17 places :

Symmetric choice reduction at 12 with 17 rule applications. Total rules 4565 place count 401 transition count 411

Iterating global reduction 12 with 17 rules applied. Total rules applied 4582 place count 401 transition count 411

Ensure Unique test removed 16 transitions

Reduce isomorphic transitions removed 16 transitions.

Iterating post reduction 12 with 16 rules applied. Total rules applied 4598 place count 401 transition count 395

Performed 68 Post agglomeration using F-continuation condition.Transition count delta: 68

Deduced a syphon composed of 68 places in 0 ms

Ensure Unique test removed 21 places

Reduce places removed 89 places and 0 transitions.

Iterating global reduction 13 with 157 rules applied. Total rules applied 4755 place count 312 transition count 327

Performed 20 Post agglomeration using F-continuation condition.Transition count delta: 20

Deduced a syphon composed of 20 places in 0 ms

Reduce places removed 20 places and 0 transitions.

Iterating global reduction 13 with 40 rules applied. Total rules applied 4795 place count 292 transition count 307

Free-agglomeration rule (complex) applied 50 times.

Iterating global reduction 13 with 50 rules applied. Total rules applied 4845 place count 292 transition count 259

Ensure Unique test removed 37 places

Reduce places removed 87 places and 0 transitions.

Iterating post reduction 13 with 87 rules applied. Total rules applied 4932 place count 205 transition count 259

Discarding 14 places :

Symmetric choice reduction at 14 with 14 rule applications. Total rules 4946 place count 191 transition count 231

Iterating global reduction 14 with 14 rules applied. Total rules applied 4960 place count 191 transition count 231

Discarding 11 places :

Symmetric choice reduction at 14 with 11 rule applications. Total rules 4971 place count 180 transition count 209

Iterating global reduction 14 with 11 rules applied. Total rules applied 4982 place count 180 transition count 209

Discarding 9 places :

Symmetric choice reduction at 14 with 9 rule applications. Total rules 4991 place count 171 transition count 191

Iterating global reduction 14 with 9 rules applied. Total rules applied 5000 place count 171 transition count 191

Partial Free-agglomeration rule applied 6 times.

Drop transitions (Partial Free agglomeration) removed 6 transitions

Iterating global reduction 14 with 6 rules applied. Total rules applied 5006 place count 171 transition count 191

Applied a total of 5006 rules in 620 ms. Remains 171 /3260 variables (removed 3089) and now considering 191/2753 (removed 2562) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 636 ms. Remains : 171/3260 places, 191/2753 transitions.

RANDOM walk for 24307 steps (213 resets) in 362 ms. (66 steps per ms) remains 0/1 properties

FORMULA FamilyReunion-PT-L00020M0002C001P001G001-ReachabilityCardinality-2024-13 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

ITS runner timed out or was interrupted.

ITS tools runner thread asked to quit. Dying gracefully.

All properties solved without resorting to model-checking.

Total runtime 13099 ms.

BK_STOP 1716688873649

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit/bin//../itstools/bin//..//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202405141337.jar

+ VERSION=202405141337

+ echo 'Running Version 202405141337'

+ /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FamilyReunion-PT-L00020M0002C001P001G001"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool itstools"

echo " Input is FamilyReunion-PT-L00020M0002C001P001G001, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r158-smll-171636267000494"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/FamilyReunion-PT-L00020M0002C001P001G001.tgz

mv FamilyReunion-PT-L00020M0002C001P001G001 execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;