About the Execution of ITS-Tools for DLCround-PT-12b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 673.079 | 15181.00 | 45693.00 | 240.70 | TFFFFFTTFTFTTTFF | normal |

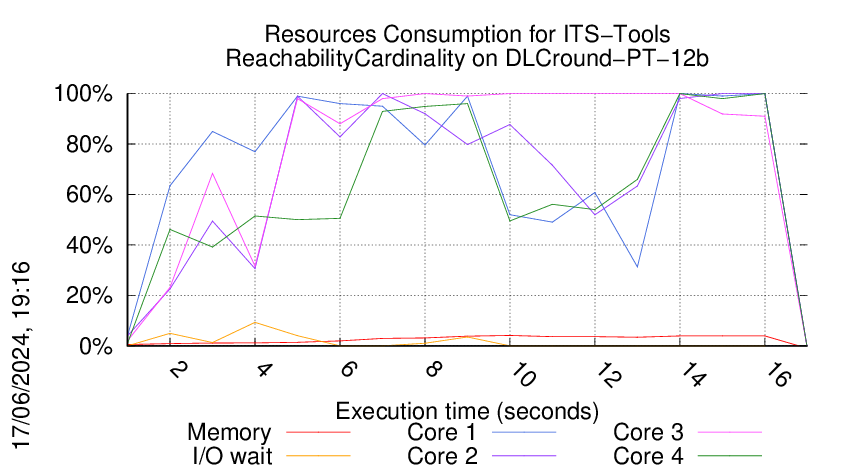

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2024-input.r114-smll-171624275600270.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2024-input.qcow2 backing_fmt=qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

..........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5568

Executing tool itstools

Input is DLCround-PT-12b, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r114-smll-171624275600270

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 2.3M

-rw-r--r-- 1 mcc users 6.6K May 14 13:22 CTLCardinality.txt

-rw-r--r-- 1 mcc users 68K May 14 13:22 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.1K May 14 13:22 CTLFireability.txt

-rw-r--r-- 1 mcc users 56K May 14 13:22 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 18 16:42 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K May 18 16:42 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.3K Apr 22 14:38 LTLCardinality.txt

-rw-r--r-- 1 mcc users 22K Apr 22 14:38 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K May 19 07:16 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K May 19 18:11 LTLFireability.xml

-rw-r--r-- 1 mcc users 7.5K Apr 13 12:12 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 70K Apr 13 12:12 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 9.5K Apr 13 12:12 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 82K Apr 13 12:12 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Apr 22 14:38 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Apr 22 14:38 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 18 16:42 equiv_col

-rw-r--r-- 1 mcc users 4 May 18 16:42 instance

-rw-r--r-- 1 mcc users 6 May 18 16:42 iscolored

-rw-r--r-- 1 mcc users 1.9M May 18 16:42 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-00

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-01

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-02

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-03

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-04

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-05

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-06

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-07

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-08

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-09

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-10

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-11

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-12

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-13

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-14

FORMULA_NAME DLCround-PT-12b-ReachabilityCardinality-2024-15

=== Now, execution of the tool begins

BK_START 1716401002241

Invoking MCC driver with

BK_TOOL=itstools

BK_EXAMINATION=ReachabilityCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=DLCround-PT-12b

BK_MEMORY_CONFINEMENT=16384

Not applying reductions.

Model is PT

ReachabilityCardinality PT

Running Version 202405141337

[2024-05-22 18:03:24] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2024-05-22 18:03:24] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2024-05-22 18:03:26] [INFO ] Load time of PNML (sax parser for PT used): 968 ms

[2024-05-22 18:03:26] [INFO ] Transformed 4848 places.

[2024-05-22 18:03:26] [INFO ] Transformed 7836 transitions.

[2024-05-22 18:03:26] [INFO ] Found NUPN structural information;

[2024-05-22 18:03:26] [INFO ] Parsed PT model containing 4848 places and 7836 transitions and 22188 arcs in 1404 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 28 ms.

Working with output stream class java.io.PrintStream

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-06 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-07 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-11 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

RANDOM walk for 40000 steps (8 resets) in 3694 ms. (10 steps per ms) remains 6/13 properties

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-15 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-13 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-12 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-08 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-05 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-03 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-01 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

BEST_FIRST walk for 40004 steps (8 resets) in 613 ms. (65 steps per ms) remains 6/6 properties

BEST_FIRST walk for 40004 steps (8 resets) in 792 ms. (50 steps per ms) remains 6/6 properties

BEST_FIRST walk for 40004 steps (8 resets) in 151 ms. (263 steps per ms) remains 6/6 properties

BEST_FIRST walk for 40004 steps (8 resets) in 479 ms. (83 steps per ms) remains 6/6 properties

BEST_FIRST walk for 40004 steps (8 resets) in 116 ms. (341 steps per ms) remains 6/6 properties

BEST_FIRST walk for 40004 steps (8 resets) in 421 ms. (94 steps per ms) remains 6/6 properties

// Phase 1: matrix 7836 rows 4848 cols

[2024-05-22 18:03:28] [INFO ] Computed 277 invariants in 90 ms

[2024-05-22 18:03:29] [INFO ] Flatten gal took : 1242 ms

All remaining problems are real, not stopping.

At refinement iteration 0 (INCLUDED_ONLY) 0/82 variables, 82/82 constraints. Problems are: Problem set: 0 solved, 6 unsolved

At refinement iteration 1 (INCLUDED_ONLY) 0/82 variables, 0/82 constraints. Problems are: Problem set: 0 solved, 6 unsolved

[2024-05-22 18:03:29] [INFO ] Flatten gal took : 468 ms

[2024-05-22 18:03:29] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality9998838011275746475.gal : 114 ms

[2024-05-22 18:03:29] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality12477228360750279762.prop : 2 ms

Invoking ITS tools like this :cd /home/mcc/execution;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202405141337/bin/its-reach-linux64' '--gc-threshold' '2000000' '--quiet' '-i' '/tmp/ReachabilityCardinality9998838011275746475.gal' '-t' 'CGAL' '-reachable-file' '/tmp/ReachabilityCardinality12477228360750279762.prop' '--nowitness' '--gen-order' 'FOLLOW'

its-reach command run as :

/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202405141337/bin/its-reach-linux64 --gc-threshold 2000000 --quiet ...329

Problem DLCround-PT-12b-ReachabilityCardinality-2024-02 is UNSAT

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-02 FALSE TECHNIQUES SMT_REFINEMENT

At refinement iteration 2 (OVERLAPS) 4376/4458 variables, 238/320 constraints. Problems are: Problem set: 1 solved, 5 unsolved

Loading property file /tmp/ReachabilityCardinality12477228360750279762.prop.

At refinement iteration 3 (INCLUDED_ONLY) 0/4458 variables, 4376/4696 constraints. Problems are: Problem set: 1 solved, 5 unsolved

At refinement iteration 4 (INCLUDED_ONLY) 0/4458 variables, 0/4696 constraints. Problems are: Problem set: 1 solved, 5 unsolved

At refinement iteration 5 (OVERLAPS) 390/4848 variables, 39/4735 constraints. Problems are: Problem set: 1 solved, 5 unsolved

At refinement iteration 6 (INCLUDED_ONLY) 0/4848 variables, 390/5125 constraints. Problems are: Problem set: 1 solved, 5 unsolved

At refinement iteration 7 (INCLUDED_ONLY) 0/4848 variables, 0/5125 constraints. Problems are: Problem set: 1 solved, 5 unsolved

SMT process timed out in 5412ms, After SMT, problems are : Problem set: 1 solved, 5 unsolved

Skipping Parikh replay, no witness traces provided.

Support contains 58 out of 4848 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4848/4848 places, 7836/7836 transitions.

Graph (trivial) has 4340 edges and 4848 vertex of which 708 / 4848 are part of one of the 53 SCC in 29 ms

Free SCC test removed 655 places

Drop transitions (Empty/Sink Transition effects.) removed 731 transitions

Reduce isomorphic transitions removed 731 transitions.

Drop transitions (Trivial Post-Agglo cleanup.) removed 1711 transitions

Trivial Post-agglo rules discarded 1711 transitions

Performed 1711 trivial Post agglomeration. Transition count delta: 1711

Iterating post reduction 0 with 1711 rules applied. Total rules applied 1712 place count 4193 transition count 5394

Reduce places removed 1711 places and 0 transitions.

Ensure Unique test removed 50 transitions

Reduce isomorphic transitions removed 50 transitions.

Drop transitions (Trivial Post-Agglo cleanup.) removed 37 transitions

Trivial Post-agglo rules discarded 37 transitions

Performed 37 trivial Post agglomeration. Transition count delta: 37

Iterating post reduction 1 with 1798 rules applied. Total rules applied 3510 place count 2482 transition count 5307

Reduce places removed 37 places and 0 transitions.

Ensure Unique test removed 3 transitions

Reduce isomorphic transitions removed 3 transitions.

Drop transitions (Trivial Post-Agglo cleanup.) removed 3 transitions

Trivial Post-agglo rules discarded 3 transitions

Performed 3 trivial Post agglomeration. Transition count delta: 3

Iterating post reduction 2 with 43 rules applied. Total rules applied 3553 place count 2445 transition count 5301

Reduce places removed 3 places and 0 transitions.

Performed 23 Post agglomeration using F-continuation condition.Transition count delta: 23

Iterating post reduction 3 with 26 rules applied. Total rules applied 3579 place count 2442 transition count 5278

Reduce places removed 23 places and 0 transitions.

Iterating post reduction 4 with 23 rules applied. Total rules applied 3602 place count 2419 transition count 5278

Performed 20 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 20 Pre rules applied. Total rules applied 3602 place count 2419 transition count 5258

Deduced a syphon composed of 20 places in 140 ms

Reduce places removed 20 places and 0 transitions.

Iterating global reduction 5 with 40 rules applied. Total rules applied 3642 place count 2399 transition count 5258

Discarding 635 places :

Symmetric choice reduction at 5 with 635 rule applications. Total rules 4277 place count 1764 transition count 4623

Iterating global reduction 5 with 635 rules applied. Total rules applied 4912 place count 1764 transition count 4623

Performed 268 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 268 Pre rules applied. Total rules applied 4912 place count 1764 transition count 4355

Deduced a syphon composed of 268 places in 50 ms

Reduce places removed 268 places and 0 transitions.

Iterating global reduction 5 with 536 rules applied. Total rules applied 5448 place count 1496 transition count 4355

Discarding 83 places :

Symmetric choice reduction at 5 with 83 rule applications. Total rules 5531 place count 1413 transition count 3039

Iterating global reduction 5 with 83 rules applied. Total rules applied 5614 place count 1413 transition count 3039

Ensure Unique test removed 27 transitions

Reduce isomorphic transitions removed 27 transitions.

Iterating post reduction 5 with 27 rules applied. Total rules applied 5641 place count 1413 transition count 3012

Performed 367 Post agglomeration using F-continuation condition with reduction of 12 identical transitions.

Deduced a syphon composed of 367 places in 3 ms

Reduce places removed 367 places and 0 transitions.

Iterating global reduction 6 with 734 rules applied. Total rules applied 6375 place count 1046 transition count 2633

Ensure Unique test removed 12 transitions

Reduce isomorphic transitions removed 12 transitions.

Iterating post reduction 6 with 12 rules applied. Total rules applied 6387 place count 1046 transition count 2621

Discarding 4 places :

Symmetric choice reduction at 7 with 4 rule applications. Total rules 6391 place count 1042 transition count 2557

Iterating global reduction 7 with 4 rules applied. Total rules applied 6395 place count 1042 transition count 2557

Performed 63 Post agglomeration using F-continuation condition.Transition count delta: -540

Deduced a syphon composed of 63 places in 2 ms

Reduce places removed 63 places and 0 transitions.

Iterating global reduction 7 with 126 rules applied. Total rules applied 6521 place count 979 transition count 3097

Drop transitions (Empty/Sink Transition effects.) removed 83 transitions

Ensure Unique test removed 4 transitions

Reduce isomorphic transitions removed 87 transitions.

Iterating post reduction 7 with 87 rules applied. Total rules applied 6608 place count 979 transition count 3010

Discarding 5 places :

Symmetric choice reduction at 8 with 5 rule applications. Total rules 6613 place count 974 transition count 2861

Iterating global reduction 8 with 5 rules applied. Total rules applied 6618 place count 974 transition count 2861

Ensure Unique test removed 3 transitions

Reduce isomorphic transitions removed 3 transitions.

Iterating post reduction 8 with 3 rules applied. Total rules applied 6621 place count 974 transition count 2858

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -12

Deduced a syphon composed of 1 places in 3 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 9 with 2 rules applied. Total rules applied 6623 place count 973 transition count 2870

Drop transitions (Redundant composition of simpler transitions.) removed 92 transitions

Redundant transition composition rules discarded 92 transitions

Iterating global reduction 9 with 92 rules applied. Total rules applied 6715 place count 973 transition count 2778

Discarding 15 places :

Symmetric choice reduction at 9 with 15 rule applications. Total rules 6730 place count 958 transition count 2763

Iterating global reduction 9 with 15 rules applied. Total rules applied 6745 place count 958 transition count 2763

Discarding 15 places :

Symmetric choice reduction at 9 with 15 rule applications. Total rules 6760 place count 943 transition count 2465

Iterating global reduction 9 with 15 rules applied. Total rules applied 6775 place count 943 transition count 2465

Ensure Unique test removed 15 transitions

Reduce isomorphic transitions removed 15 transitions.

Iterating post reduction 9 with 15 rules applied. Total rules applied 6790 place count 943 transition count 2450

Performed 14 Post agglomeration using F-continuation condition.Transition count delta: 14

Deduced a syphon composed of 14 places in 1 ms

Reduce places removed 14 places and 0 transitions.

Iterating global reduction 10 with 28 rules applied. Total rules applied 6818 place count 929 transition count 2436

Discarding 13 places :

Symmetric choice reduction at 10 with 13 rule applications. Total rules 6831 place count 916 transition count 2192

Iterating global reduction 10 with 13 rules applied. Total rules applied 6844 place count 916 transition count 2192

Ensure Unique test removed 11 transitions

Reduce isomorphic transitions removed 11 transitions.

Iterating post reduction 10 with 11 rules applied. Total rules applied 6855 place count 916 transition count 2181

Drop transitions (Redundant composition of simpler transitions.) removed 2 transitions

Redundant transition composition rules discarded 2 transitions

Iterating global reduction 11 with 2 rules applied. Total rules applied 6857 place count 916 transition count 2179

Free-agglomeration rule applied 463 times with reduction of 201 identical transitions.

Iterating global reduction 11 with 463 rules applied. Total rules applied 7320 place count 916 transition count 1515

Reduce places removed 463 places and 0 transitions.

Drop transitions (Empty/Sink Transition effects.) removed 553 transitions

Ensure Unique test removed 9 transitions

Reduce isomorphic transitions removed 562 transitions.

Graph (complete) has 1238 edges and 453 vertex of which 383 are kept as prefixes of interest. Removing 70 places using SCC suffix rule.3 ms

Discarding 70 places :

Also discarding 0 output transitions

Iterating post reduction 11 with 1026 rules applied. Total rules applied 8346 place count 383 transition count 953

Drop transitions (Empty/Sink Transition effects.) removed 30 transitions

Ensure Unique test removed 37 transitions

Reduce isomorphic transitions removed 67 transitions.

Iterating post reduction 12 with 67 rules applied. Total rules applied 8413 place count 383 transition count 886

Discarding 93 places :

Symmetric choice reduction at 13 with 93 rule applications. Total rules 8506 place count 290 transition count 696

Iterating global reduction 13 with 93 rules applied. Total rules applied 8599 place count 290 transition count 696

Performed 5 Post agglomeration using F-continuation condition.Transition count delta: -55

Deduced a syphon composed of 5 places in 1 ms

Reduce places removed 5 places and 0 transitions.

Iterating global reduction 13 with 10 rules applied. Total rules applied 8609 place count 285 transition count 751

Drop transitions (Empty/Sink Transition effects.) removed 46 transitions

Ensure Unique test removed 8 transitions

Reduce isomorphic transitions removed 54 transitions.

Iterating post reduction 13 with 54 rules applied. Total rules applied 8663 place count 285 transition count 697

Discarding 1 places :

Symmetric choice reduction at 14 with 1 rule applications. Total rules 8664 place count 284 transition count 677

Iterating global reduction 14 with 1 rules applied. Total rules applied 8665 place count 284 transition count 677

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 8666 place count 284 transition count 676

Drop transitions (Redundant composition of simpler transitions.) removed 55 transitions

Redundant transition composition rules discarded 55 transitions

Iterating global reduction 15 with 55 rules applied. Total rules applied 8721 place count 284 transition count 621

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 15 with 1 rules applied. Total rules applied 8722 place count 283 transition count 621

Discarding 7 places :

Symmetric choice reduction at 16 with 7 rule applications. Total rules 8729 place count 276 transition count 610

Iterating global reduction 16 with 7 rules applied. Total rules applied 8736 place count 276 transition count 610

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -5

Deduced a syphon composed of 1 places in 1 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 16 with 2 rules applied. Total rules applied 8738 place count 275 transition count 615

Drop transitions (Empty/Sink Transition effects.) removed 6 transitions

Reduce isomorphic transitions removed 6 transitions.

Iterating post reduction 16 with 6 rules applied. Total rules applied 8744 place count 275 transition count 609

Partial Free-agglomeration rule applied 1 times.

Drop transitions (Partial Free agglomeration) removed 1 transitions

Iterating global reduction 17 with 1 rules applied. Total rules applied 8745 place count 275 transition count 609

Drop transitions (Redundant composition of simpler transitions.) removed 1 transitions

Redundant transition composition rules discarded 1 transitions

Iterating global reduction 17 with 1 rules applied. Total rules applied 8746 place count 275 transition count 608

Applied a total of 8746 rules in 2743 ms. Remains 275 /4848 variables (removed 4573) and now considering 608/7836 (removed 7228) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 2761 ms. Remains : 275/4848 places, 608/7836 transitions.

RANDOM walk for 40000 steps (8 resets) in 1467 ms. (27 steps per ms) remains 1/5 properties

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-14 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-10 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-09 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-04 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

BEST_FIRST walk for 33419 steps (7 resets) in 203 ms. (163 steps per ms) remains 0/1 properties

FORMULA DLCround-PT-12b-ReachabilityCardinality-2024-00 TRUE TECHNIQUES TOPOLOGICAL BESTFIRST_WALK

ITS runner timed out or was interrupted.

ITS tools runner thread asked to quit. Dying gracefully.

All properties solved without resorting to model-checking.

Total runtime 12548 ms.

BK_STOP 1716401017422

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit/bin//../itstools/bin//..//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202405141337.jar

+ VERSION=202405141337

+ echo 'Running Version 202405141337'

+ /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-12b"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5568"

echo " Executing tool itstools"

echo " Input is DLCround-PT-12b, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r114-smll-171624275600270"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-12b.tgz

mv DLCround-PT-12b execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;