About the Execution of LoLa+red for PGCD-COL-D04N050

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 3305.604 | 74860.00 | 76046.00 | 603.40 | TTTTTTFTT?FF?TTT | normal |

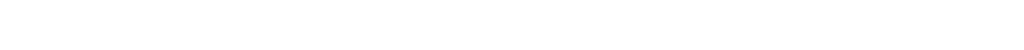

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r519-tall-167987245300417.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lolaxred

Input is PGCD-COL-D04N050, examination is CTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r519-tall-167987245300417

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 448K

-rw-r--r-- 1 mcc users 6.3K Mar 23 15:24 CTLCardinality.txt

-rw-r--r-- 1 mcc users 69K Mar 23 15:24 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.5K Mar 23 15:20 CTLFireability.txt

-rw-r--r-- 1 mcc users 53K Mar 23 15:20 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 23 07:07 LTLCardinality.txt

-rw-r--r-- 1 mcc users 30K Mar 23 07:07 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K Mar 23 07:07 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K Mar 23 07:07 LTLFireability.xml

-rw-r--r-- 1 mcc users 1 Mar 26 22:42 NewModel

-rw-r--r-- 1 mcc users 9.6K Mar 23 15:26 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 103K Mar 23 15:26 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 8.2K Mar 23 15:26 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 79K Mar 23 15:26 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Mar 23 07:07 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Mar 23 07:07 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 26 22:42 equiv_pt

-rw-r--r-- 1 mcc users 8 Mar 26 22:42 instance

-rw-r--r-- 1 mcc users 5 Mar 26 22:42 iscolored

-rw-r--r-- 1 mcc users 11K Mar 31 16:48 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-00

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-01

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-02

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-03

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-04

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-05

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-06

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-07

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-08

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-09

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-10

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-11

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-12

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-13

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-14

FORMULA_NAME PGCD-COL-D04N050-CTLCardinality-15

=== Now, execution of the tool begins

BK_START 1680814644943

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lolaxred

BK_EXAMINATION=CTLCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=PGCD-COL-D04N050

Applying reductions before tool lola

Invoking reducer

Running Version 202304061127

[2023-04-06 20:57:26] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLCardinality, -timeout, 360, -rebuildPNML]

[2023-04-06 20:57:26] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-04-06 20:57:26] [INFO ] Detected file is not PT type :http://www.pnml.org/version-2009/grammar/symmetricnet

log4j:WARN No appenders could be found for logger (org.apache.axiom.locator.DefaultOMMetaFactoryLocator).

log4j:WARN Please initialize the log4j system properly.

log4j:WARN See http://logging.apache.org/log4j/1.2/faq.html#noconfig for more info.

[2023-04-06 20:57:26] [WARNING] Using fallBack plugin, rng conformance not checked

[2023-04-06 20:57:27] [INFO ] Load time of PNML (colored model parsed with PNMLFW) : 541 ms

[2023-04-06 20:57:27] [INFO ] Imported 3 HL places and 3 HL transitions for a total of 15 PT places and 15.0 transition bindings in 18 ms.

Parsed 16 properties from file /home/mcc/execution/CTLCardinality.xml in 17 ms.

[2023-04-06 20:57:27] [INFO ] Built PT skeleton of HLPN with 3 places and 3 transitions 14 arcs in 4 ms.

[2023-04-06 20:57:27] [INFO ] Skeletonized 16 HLPN properties in 2 ms.

Initial state reduction rules removed 1 formulas.

FORMULA PGCD-COL-D04N050-CTLCardinality-04 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Computed a total of 0 stabilizing places and 0 stable transitions

Remains 15 properties that can be checked using skeleton over-approximation.

Computed a total of 0 stabilizing places and 0 stable transitions

Incomplete random walk after 10169 steps, including 2 resets, run finished after 40 ms. (steps per millisecond=254 ) properties (out of 59) seen :50

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 145 ms. (steps per millisecond=68 ) properties (out of 9) seen :1

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 73 ms. (steps per millisecond=137 ) properties (out of 8) seen :1

Incomplete Best-First random walk after 10000 steps, including 2 resets, run finished after 65 ms. (steps per millisecond=153 ) properties (out of 7) seen :0

Incomplete Best-First random walk after 10000 steps, including 2 resets, run finished after 77 ms. (steps per millisecond=129 ) properties (out of 7) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 60 ms. (steps per millisecond=166 ) properties (out of 7) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 38 ms. (steps per millisecond=263 ) properties (out of 7) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 73 ms. (steps per millisecond=137 ) properties (out of 7) seen :0

Running SMT prover for 7 properties.

// Phase 1: matrix 3 rows 3 cols

[2023-04-06 20:57:27] [INFO ] Computed 2 invariants in 3 ms

[2023-04-06 20:57:27] [INFO ] [Real]Absence check using 2 positive place invariants in 3 ms returned sat

[2023-04-06 20:57:27] [INFO ] After 137ms SMT Verify possible using all constraints in real domain returned unsat :1 sat :0 real:6

[2023-04-06 20:57:27] [INFO ] [Nat]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-04-06 20:57:27] [INFO ] After 46ms SMT Verify possible using all constraints in natural domain returned unsat :7 sat :0

Fused 7 Parikh solutions to 0 different solutions.

Parikh walk visited 0 properties in 1 ms.

Successfully simplified 7 atomic propositions for a total of 15 simplifications.

[2023-04-06 20:57:28] [INFO ] Initial state reduction rules for CTL removed 1 formulas.

[2023-04-06 20:57:28] [INFO ] Flatten gal took : 13 ms

FORMULA PGCD-COL-D04N050-CTLCardinality-14 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-04-06 20:57:28] [INFO ] Flatten gal took : 2 ms

Arc [2:1*[(MOD (ADD $x 1) 5)]] contains successor/predecessor on variables of sort CD

[2023-04-06 20:57:28] [INFO ] Unfolded HLPN to a Petri net with 15 places and 15 transitions 70 arcs in 5 ms.

[2023-04-06 20:57:28] [INFO ] Unfolded 14 HLPN properties in 0 ms.

Support contains 15 out of 15 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 5 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

// Phase 1: matrix 15 rows 15 cols

[2023-04-06 20:57:28] [INFO ] Computed 6 invariants in 1 ms

[2023-04-06 20:57:28] [INFO ] Dead Transitions using invariants and state equation in 60 ms found 0 transitions.

[2023-04-06 20:57:28] [INFO ] Invariant cache hit.

[2023-04-06 20:57:28] [INFO ] Implicit Places using invariants in 29 ms returned []

[2023-04-06 20:57:28] [INFO ] Invariant cache hit.

[2023-04-06 20:57:28] [INFO ] State equation strengthened by 5 read => feed constraints.

[2023-04-06 20:57:28] [INFO ] Implicit Places using invariants and state equation in 36 ms returned []

Implicit Place search using SMT with State Equation took 67 ms to find 0 implicit places.

[2023-04-06 20:57:28] [INFO ] Invariant cache hit.

[2023-04-06 20:57:28] [INFO ] Dead Transitions using invariants and state equation in 30 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 166 ms. Remains : 15/15 places, 15/15 transitions.

Support contains 15 out of 15 places after structural reductions.

[2023-04-06 20:57:28] [INFO ] Flatten gal took : 4 ms

[2023-04-06 20:57:28] [INFO ] Flatten gal took : 4 ms

[2023-04-06 20:57:28] [INFO ] Input system was already deterministic with 15 transitions.

Incomplete random walk after 10050 steps, including 2 resets, run finished after 35 ms. (steps per millisecond=287 ) properties (out of 47) seen :25

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=142 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 8 ms. (steps per millisecond=125 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 22) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 22) seen :0

Running SMT prover for 22 properties.

[2023-04-06 20:57:28] [INFO ] Invariant cache hit.

[2023-04-06 20:57:28] [INFO ] [Real]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-04-06 20:57:28] [INFO ] [Real]Absence check using 2 positive and 4 generalized place invariants in 1 ms returned sat

[2023-04-06 20:57:28] [INFO ] After 126ms SMT Verify possible using all constraints in real domain returned unsat :2 sat :0 real:20

[2023-04-06 20:57:28] [INFO ] [Nat]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-04-06 20:57:28] [INFO ] [Nat]Absence check using 2 positive and 4 generalized place invariants in 2 ms returned sat

[2023-04-06 20:57:28] [INFO ] After 53ms SMT Verify possible using state equation in natural domain returned unsat :5 sat :17

[2023-04-06 20:57:28] [INFO ] State equation strengthened by 5 read => feed constraints.

[2023-04-06 20:57:28] [INFO ] After 48ms SMT Verify possible using 5 Read/Feed constraints in natural domain returned unsat :5 sat :17

[2023-04-06 20:57:28] [INFO ] After 102ms SMT Verify possible using trap constraints in natural domain returned unsat :5 sat :17

Attempting to minimize the solution found.

Minimization took 48 ms.

[2023-04-06 20:57:28] [INFO ] After 263ms SMT Verify possible using all constraints in natural domain returned unsat :5 sat :17

Fused 22 Parikh solutions to 17 different solutions.

Parikh walk visited 11 properties in 159 ms.

Support contains 10 out of 15 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 4 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] Dead Transitions using invariants and state equation in 37 ms found 0 transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 41 ms. Remains : 15/15 places, 15/15 transitions.

Incomplete random walk after 10012 steps, including 2 resets, run finished after 13 ms. (steps per millisecond=770 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 14 ms. (steps per millisecond=714 ) properties (out of 6) seen :1

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=833 ) properties (out of 5) seen :1

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 11 ms. (steps per millisecond=909 ) properties (out of 4) seen :1

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 10 ms. (steps per millisecond=1000 ) properties (out of 3) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 8 ms. (steps per millisecond=1250 ) properties (out of 3) seen :0

Running SMT prover for 3 properties.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] [Real]Absence check using 2 positive place invariants in 0 ms returned sat

[2023-04-06 20:57:29] [INFO ] [Real]Absence check using 2 positive and 4 generalized place invariants in 7 ms returned sat

[2023-04-06 20:57:29] [INFO ] After 59ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:3

[2023-04-06 20:57:29] [INFO ] [Nat]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-04-06 20:57:29] [INFO ] [Nat]Absence check using 2 positive and 4 generalized place invariants in 1 ms returned sat

[2023-04-06 20:57:29] [INFO ] After 12ms SMT Verify possible using state equation in natural domain returned unsat :0 sat :3

[2023-04-06 20:57:29] [INFO ] State equation strengthened by 5 read => feed constraints.

[2023-04-06 20:57:29] [INFO ] After 15ms SMT Verify possible using 5 Read/Feed constraints in natural domain returned unsat :0 sat :3

[2023-04-06 20:57:29] [INFO ] After 25ms SMT Verify possible using trap constraints in natural domain returned unsat :0 sat :3

Attempting to minimize the solution found.

Minimization took 12 ms.

[2023-04-06 20:57:29] [INFO ] After 74ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :3

Finished Parikh walk after 347 steps, including 0 resets, run visited all 3 properties in 6 ms. (steps per millisecond=57 )

Parikh walk visited 3 properties in 5 ms.

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 3 ms

[2023-04-06 20:57:29] [INFO ] Input system was already deterministic with 15 transitions.

Computed a total of 0 stabilizing places and 0 stable transitions

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] Dead Transitions using invariants and state equation in 30 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 31 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 3 ms

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:29] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 2 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] Dead Transitions using invariants and state equation in 25 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 28 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:29] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] Dead Transitions using invariants and state equation in 30 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 31 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 5 ms

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:29] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:29] [INFO ] Invariant cache hit.

[2023-04-06 20:57:29] [INFO ] Dead Transitions using invariants and state equation in 20 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 22 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:29] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:29] [INFO ] Input system was already deterministic with 15 transitions.

Incomplete random walk after 10009 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=2502 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=1666 ) properties (out of 1) seen :0

Interrupted probabilistic random walk after 2418933 steps, run timeout after 3001 ms. (steps per millisecond=806 ) properties seen :{}

Probabilistic random walk after 2418933 steps, saw 1364152 distinct states, run finished after 3002 ms. (steps per millisecond=805 ) properties seen :0

Running SMT prover for 1 properties.

[2023-04-06 20:57:32] [INFO ] Invariant cache hit.

[2023-04-06 20:57:32] [INFO ] [Real]Absence check using 2 positive place invariants in 0 ms returned sat

[2023-04-06 20:57:32] [INFO ] [Real]Absence check using 2 positive and 4 generalized place invariants in 1 ms returned sat

[2023-04-06 20:57:32] [INFO ] After 31ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-04-06 20:57:32] [INFO ] [Nat]Absence check using 2 positive place invariants in 0 ms returned sat

[2023-04-06 20:57:32] [INFO ] [Nat]Absence check using 2 positive and 4 generalized place invariants in 1 ms returned sat

[2023-04-06 20:57:32] [INFO ] After 10ms SMT Verify possible using state equation in natural domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] State equation strengthened by 5 read => feed constraints.

[2023-04-06 20:57:32] [INFO ] After 3ms SMT Verify possible using 5 Read/Feed constraints in natural domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] After 7ms SMT Verify possible using trap constraints in natural domain returned unsat :0 sat :1

Attempting to minimize the solution found.

Minimization took 3 ms.

[2023-04-06 20:57:32] [INFO ] After 50ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :1

Parikh walk visited 0 properties in 59 ms.

Support contains 5 out of 15 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:32] [INFO ] Invariant cache hit.

[2023-04-06 20:57:32] [INFO ] Dead Transitions using invariants and state equation in 33 ms found 0 transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 34 ms. Remains : 15/15 places, 15/15 transitions.

Incomplete random walk after 100000 steps, including 2 resets, run finished after 40 ms. (steps per millisecond=2500 ) properties (out of 1) seen :0

Running SMT prover for 1 properties.

[2023-04-06 20:57:32] [INFO ] Invariant cache hit.

[2023-04-06 20:57:32] [INFO ] [Real]Absence check using 2 positive place invariants in 0 ms returned sat

[2023-04-06 20:57:32] [INFO ] [Real]Absence check using 2 positive and 4 generalized place invariants in 2 ms returned sat

[2023-04-06 20:57:32] [INFO ] After 7ms SMT Verify possible using state equation in real domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] State equation strengthened by 5 read => feed constraints.

[2023-04-06 20:57:32] [INFO ] After 2ms SMT Verify possible using 5 Read/Feed constraints in real domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] After 6ms SMT Verify possible using trap constraints in real domain returned unsat :0 sat :0 real:1

[2023-04-06 20:57:32] [INFO ] After 40ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-04-06 20:57:32] [INFO ] [Nat]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-04-06 20:57:32] [INFO ] [Nat]Absence check using 2 positive and 4 generalized place invariants in 1 ms returned sat

[2023-04-06 20:57:32] [INFO ] After 8ms SMT Verify possible using state equation in natural domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] After 2ms SMT Verify possible using 5 Read/Feed constraints in natural domain returned unsat :0 sat :1

[2023-04-06 20:57:32] [INFO ] After 6ms SMT Verify possible using trap constraints in natural domain returned unsat :0 sat :1

Attempting to minimize the solution found.

Minimization took 3 ms.

[2023-04-06 20:57:32] [INFO ] After 39ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :1

Incomplete random walk after 1000038 steps, including 2 resets, run finished after 223 ms. (steps per millisecond=4484 ) properties (out of 1) seen :0

Finished Best-First random walk after 3721 steps, including 0 resets, run visited all 1 properties in 2 ms. (steps per millisecond=1860 )

FORMULA PGCD-COL-D04N050-CTLCardinality-03 TRUE TECHNIQUES TOPOLOGICAL BESTFIRST_WALK

Parikh walk visited 0 properties in 0 ms.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 34 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 36 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 27 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 28 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 22 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 23 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 31 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 32 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 3 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 23 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 23 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 36 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 39 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 24 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 24 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 24 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 26 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 3 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 1 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 25 ms found 0 transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 27 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

Starting structural reductions in LTL mode, iteration 0 : 15/15 places, 15/15 transitions.

Applied a total of 0 rules in 0 ms. Remains 15 /15 variables (removed 0) and now considering 15/15 (removed 0) transitions.

[2023-04-06 20:57:33] [INFO ] Invariant cache hit.

[2023-04-06 20:57:33] [INFO ] Dead Transitions using invariants and state equation in 22 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 23 ms. Remains : 15/15 places, 15/15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Input system was already deterministic with 15 transitions.

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 2 ms

[2023-04-06 20:57:33] [INFO ] Flatten gal took : 1 ms

[2023-04-06 20:57:33] [INFO ] Export to MCC of 13 properties in file /home/mcc/execution/CTLCardinality.sr.xml took 2 ms.

[2023-04-06 20:57:33] [INFO ] Export to PNML in file /home/mcc/execution/model.sr.pnml of net with 15 places, 15 transitions and 70 arcs took 0 ms.

Total runtime 6932 ms.

There are residual formulas that ITS could not solve within timeout

starting LoLA

BK_INPUT PGCD-COL-D04N050

BK_EXAMINATION: CTLCardinality

bin directory: /home/mcc/BenchKit/bin//../reducer/bin//../../lola/bin/

current directory: /home/mcc/execution/369

FORMULA PGCD-COL-D04N050-CTLCardinality-02 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-08 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-06 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-15 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-05 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-11 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-00 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-01 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-13 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA PGCD-COL-D04N050-CTLCardinality-07 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

BK_STOP 1680814719803

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202304061127.jar

+ VERSION=202304061127

+ echo 'Running Version 202304061127'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination CTLCardinality -timeout 360 -rebuildPNML

lola: MEM LIMIT 32

lola: MEM LIMIT 5

lola: NET

lola: input: PNML file (--pnmlnet)

lola: reading net from /home/mcc/execution/369/model.pnml

lola: reading pnml

lola: PNML file contains place/transition net

lola: finished parsing

lola: closed net file /home/mcc/execution/369/model.pnml

lola: Reading formula.

lola: Using XML format (--xmlformula)

lola: reading XML formula

lola: reading formula from /home/mcc/execution/369/CTLCardinality.xml

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:96

lola: rewrite Frontend/Parser/formula_rewrite.k:120

lola: rewrite Frontend/Parser/formula_rewrite.k:394

lola: rewrite Frontend/Parser/formula_rewrite.k:96

lola: rewrite Frontend/Parser/formula_rewrite.k:96

lola: rewrite Frontend/Parser/formula_rewrite.k:162

lola: rewrite Frontend/Parser/formula_rewrite.k:150

lola: rewrite Frontend/Parser/formula_rewrite.k:162

lola: rewrite Frontend/Parser/formula_rewrite.k:147

lola: rewrite Frontend/Parser/formula_rewrite.k:120

lola: rewrite Frontend/Parser/formula_rewrite.k:117

lola: rewrite Frontend/Parser/formula_rewrite.k:156

lola: rewrite Frontend/Parser/formula_rewrite.k:150

lola: rewrite Frontend/Parser/formula_rewrite.k:121

lola: rewrite Frontend/Parser/formula_rewrite.k:469

lola: rewrite Frontend/Parser/formula_rewrite.k:475

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:98

lola: rewrite Frontend/Parser/formula_rewrite.k:129

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:96

lola: rewrite Frontend/Parser/formula_rewrite.k:183

lola: rewrite Frontend/Parser/formula_rewrite.k:96

lola: rewrite Frontend/Parser/formula_rewrite.k:132

lola: rewrite Frontend/Parser/formula_rewrite.k:138

lola: rewrite Frontend/Parser/formula_rewrite.k:469

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: RELEASE

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:98

lola: rewrite Frontend/Parser/formula_rewrite.k:165

lola: rewrite Frontend/Parser/formula_rewrite.k:147

lola: rewrite Frontend/Parser/formula_rewrite.k:165

lola: rewrite Frontend/Parser/formula_rewrite.k:150

lola: rewrite Frontend/Parser/formula_rewrite.k:278

lola: rewrite Frontend/Parser/formula_rewrite.k:116

lola: rewrite Frontend/Parser/formula_rewrite.k:120

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: NOTDEADLOCKFREE

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: LAUNCH task # 49 (type SKEL/FNDP) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 50 (type SKEL/EQUN) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 51 (type SKEL/SRCH) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: LAUNCH task # 52 (type SKEL/SRCH) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: FINISHED task # 52 (type SKEL/SRCH) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : unknown

lola: markings : 2

lola: fired transitions : 2

lola: time used : 0.000000

lola: memory pages used : 1

lola: Created skeleton in 0.000000 secs.

lola: FINISHED task # 51 (type SKEL/SRCH) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : true

lola: markings : 47

lola: fired transitions : 46

lola: time used : 0.000000

lola: memory pages used : 1

lola: NOTDEADLOCKFREE

lola: CANCELED task # 49 (type FNDP) for PGCD-COL-D04N050-CTLCardinality-06 (obsolete)

lola: CANCELED task # 50 (type EQUN) for PGCD-COL-D04N050-CTLCardinality-06 (obsolete)

lola: FINISHED task # 49 (type SKEL/FNDP) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : true

lola: fired transitions : 45

lola: tried executions : 1

lola: time used : 0.000000

lola: memory pages used : 0

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:714

lola: LAUNCH task # 53 (type SKEL/SRCH) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: FINISHED task # 53 (type SKEL/SRCH) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

lola: markings : 70

lola: fired transitions : 69

lola: time used : 0.000000

lola: memory pages used : 1

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Rule S: 0 transitions removed,0 places removed

lola: NOTDEADLOCKFREE

lola: Created skeleton in 0.000000 secs.

sara: try reading problem file /home/mcc/execution/369/CTLCardinality-50.sara.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: FINISHED task # 50 (type SKEL/EQUN) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : true

lola: Created skeleton in 0.000000 secs.

lola: RELEASE

lola: Created skeleton in 0.000000 secs.

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:715

lola: rewrite Frontend/Parser/formula_rewrite.k:714

lola: LAUNCH task # 12 (type EXCL) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 189 sec

lola: memory limit: 32 pages

lola: FINISHED task # 12 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

lola: markings : 68

lola: fired transitions : 67

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 7 (type EXCL) for 6 PGCD-COL-D04N050-CTLCardinality-02

lola: time limit : 200 sec

lola: memory limit: 32 pages

lola: FINISHED task # 7 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-02

lola: result : true

lola: markings : 2

lola: fired transitions : 2

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 23 (type EXCL) for 22 PGCD-COL-D04N050-CTLCardinality-08

lola: time limit : 225 sec

lola: memory limit: 32 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: LAUNCH task # 55 (type FNDP) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 56 (type EQUN) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 58 (type SRCH) for 16 PGCD-COL-D04N050-CTLCardinality-06

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:813

sara: try reading problem file /home/mcc/execution/369/CTLCardinality-56.sara.

sara: place or transition ordering is non-deterministic

lola: Created skeleton in 0.000000 secs.

lola: FINISHED task # 23 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-08

lola: result : true

lola: markings : 3

lola: fired transitions : 3

lola: time used : 0.000000

lola: memory pages used : 1

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: Created skeleton in 0.000000 secs.

lola: LAUNCH task # 26 (type EXCL) for 25 PGCD-COL-D04N050-CTLCardinality-09

lola: time limit : 225 sec

lola: memory limit: 32 pages

lola: FINISHED task # 56 (type EQUN) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : true

lola: CANCELED task # 55 (type FNDP) for PGCD-COL-D04N050-CTLCardinality-06 (obsolete)

lola: CANCELED task # 58 (type SRCH) for PGCD-COL-D04N050-CTLCardinality-06 (obsolete)

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: FINISHED task # 55 (type FNDP) for PGCD-COL-D04N050-CTLCardinality-06

lola: result : true

lola: fired transitions : 45

lola: tried executions : 1

lola: time used : 0.000000

lola: memory pages used : 0

lola: FINISHED task # 58 (type SRCH) for PGCD-COL-D04N050-CTLCardinality-06

lola: NOTDEADLOCKFREE

lola: result : unknown

lola: markings : 7727

lola: fired transitions : 29040

lola: time used : 0.000000

lola: memory pages used : 1

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: LAUNCH task # 64 (type SKEL/SRCH) for 44 PGCD-COL-D04N050-CTLCardinality-15

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: LAUNCH task # 60 (type SKEL/FNDP) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 61 (type SKEL/EQUN) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: FINISHED task # 60 (type SKEL/FNDP) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

lola: fired transitions : 28

lola: tried executions : 1

lola: time used : 0.000000

lola: memory pages used : 0

lola: CANCELED task # 61 (type EQUN) for PGCD-COL-D04N050-CTLCardinality-05 (obsolete)

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: LAUNCH task # 65 (type FNDP) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 66 (type EQUN) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:711

lola: FINISHED task # 64 (type SKEL/SRCH) for PGCD-COL-D04N050-CTLCardinality-15

lola: result : true

lola: time used : 0.000000

lola: memory pages used : 1

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: LAUNCH task # 68 (type SRCH) for 9 PGCD-COL-D04N050-CTLCardinality-05

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

sara: try reading problem file /home/mcc/execution/369/CTLCardinality-61.sara.

lola: FINISHED task # 61 (type SKEL/EQUN) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

lola: FINISHED task # 65 (type FNDP) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

lola: fired transitions : 28

lola: tried executions : 1

lola: time used : 0.000000

lola: memory pages used : 0

sara: try reading problem file /home/mcc/execution/369/CTLCardinality-66.sara.

sara: place or transition ordering is non-deterministic

lola: CANCELED task # 66 (type EQUN) for PGCD-COL-D04N050-CTLCardinality-05 (obsolete)

lola: CANCELED task # 68 (type SRCH) for PGCD-COL-D04N050-CTLCardinality-05 (obsolete)

lola: FINISHED task # 66 (type EQUN) for PGCD-COL-D04N050-CTLCardinality-05

lola: result : true

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-00: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-01: EG 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 1 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-10: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-11: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 2 0 0 2 0 0 0

PGCD-COL-D04N050-CTLCardinality-13: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

26 CTL EXCL 5/400 12/32 PGCD-COL-D04N050-CTLCardinality-09 2677374 m, 535474 m/sec, 8265353 t fired, .

Time elapsed: 5 secs. Pages in use: 12

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-00: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-01: EG 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 1 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-10: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-11: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 2 0 0 2 0 0 0

PGCD-COL-D04N050-CTLCardinality-13: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

26 CTL EXCL 10/400 24/32 PGCD-COL-D04N050-CTLCardinality-09 5320772 m, 528679 m/sec, 16131360 t fired, .

Time elapsed: 10 secs. Pages in use: 24

# running tasks: 1 of 4 Visible: 13

lola: CANCELED task # 26 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-09 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-00: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-01: EG 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-10: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-11: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 2 0 0 2 0 0 0

PGCD-COL-D04N050-CTLCardinality-13: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 15 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

lola: LAUNCH task # 32 (type EXCL) for 31 PGCD-COL-D04N050-CTLCardinality-11

lola: time limit : 448 sec

lola: memory limit: 32 pages

lola: FINISHED task # 32 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-11

lola: result : false

lola: markings : 1

lola: fired transitions : 1

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 29 (type EXCL) for 28 PGCD-COL-D04N050-CTLCardinality-10

lola: time limit : 512 sec

lola: memory limit: 32 pages

lola: FINISHED task # 29 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-10

lola: result : false

lola: markings : 3

lola: fired transitions : 3

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 1 (type EXCL) for 0 PGCD-COL-D04N050-CTLCardinality-00

lola: time limit : 597 sec

lola: memory limit: 32 pages

lola: FINISHED task # 1 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-00

lola: result : true

lola: markings : 1

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 4 (type EXCL) for 3 PGCD-COL-D04N050-CTLCardinality-01

lola: time limit : 717 sec

lola: memory limit: 32 pages

lola: FINISHED task # 4 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-01

lola: result : true

lola: markings : 3

lola: fired transitions : 3

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 42 (type EXCL) for 41 PGCD-COL-D04N050-CTLCardinality-13

lola: time limit : 896 sec

lola: memory limit: 32 pages

lola: FINISHED task # 42 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-13

lola: result : true

lola: markings : 3

lola: fired transitions : 6

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 39 (type EXCL) for 34 PGCD-COL-D04N050-CTLCardinality-12

lola: time limit : 1195 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 1 1 0 2 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 5/1195 9/32 PGCD-COL-D04N050-CTLCardinality-12 1978072 m, 395614 m/sec, 11378078 t fired, .

Time elapsed: 20 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 1 1 0 2 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 10/1195 17/32 PGCD-COL-D04N050-CTLCardinality-12 3735734 m, 351532 m/sec, 21647945 t fired, .

Time elapsed: 25 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 1 1 0 2 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 15/1195 24/32 PGCD-COL-D04N050-CTLCardinality-12 5436663 m, 340185 m/sec, 31678228 t fired, .

Time elapsed: 30 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 1 1 0 2 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 20/1195 31/32 PGCD-COL-D04N050-CTLCardinality-12 7049676 m, 322602 m/sec, 41495674 t fired, .

Time elapsed: 35 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

lola: CANCELED task # 39 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-12 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 1 0 0 2 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 40 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

lola: LAUNCH task # 37 (type EXCL) for 34 PGCD-COL-D04N050-CTLCardinality-12

lola: time limit : 1780 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 0 1 0 2 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

37 CTL EXCL 5/1780 9/32 PGCD-COL-D04N050-CTLCardinality-12 1907826 m, 381565 m/sec, 11464964 t fired, .

Time elapsed: 45 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 0 1 0 2 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

37 CTL EXCL 10/1780 16/32 PGCD-COL-D04N050-CTLCardinality-12 3629614 m, 344357 m/sec, 21799573 t fired, .

Time elapsed: 50 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 0 1 0 2 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

37 CTL EXCL 15/1780 24/32 PGCD-COL-D04N050-CTLCardinality-12 5311646 m, 336406 m/sec, 31824315 t fired, .

Time elapsed: 55 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 0 1 0 2 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

37 CTL EXCL 20/1780 31/32 PGCD-COL-D04N050-CTLCardinality-12 6945685 m, 326807 m/sec, 41667085 t fired, .

Time elapsed: 60 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

lola: CANCELED task # 37 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-12 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

PGCD-COL-D04N050-CTLCardinality-07: CTL 0 1 0 0 1 0 0 0

PGCD-COL-D04N050-CTLCardinality-09: CTL 0 0 0 0 1 0 1 0

PGCD-COL-D04N050-CTLCardinality-12: DISJ 0 0 0 0 2 0 2 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 65 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 13

lola: LAUNCH task # 20 (type EXCL) for 19 PGCD-COL-D04N050-CTLCardinality-07

lola: time limit : 3535 sec

lola: memory limit: 32 pages

lola: FINISHED task # 20 (type EXCL) for PGCD-COL-D04N050-CTLCardinality-07

lola: result : true

lola: markings : 3

lola: fired transitions : 6

lola: time used : 0.000000

lola: memory pages used : 1

lola: Portfolio finished: no open tasks 13

FINAL RESULTS

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

PGCD-COL-D04N050-CTLCardinality-00: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-01: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-02: EXEG true state space /EXEG

PGCD-COL-D04N050-CTLCardinality-05: CONJ true CONJ

PGCD-COL-D04N050-CTLCardinality-06: AG false state equation

PGCD-COL-D04N050-CTLCardinality-07: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-08: EG true state space / EG

PGCD-COL-D04N050-CTLCardinality-09: CTL unknown AGGR

PGCD-COL-D04N050-CTLCardinality-10: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-11: CTL false CTL model checker

PGCD-COL-D04N050-CTLCardinality-12: DISJ unknown DISJ

PGCD-COL-D04N050-CTLCardinality-13: CTL true CTL model checker

PGCD-COL-D04N050-CTLCardinality-15: LTL/CTL true skeleton: CTL model checker

Time elapsed: 65 secs. Pages in use: 32

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="PGCD-COL-D04N050"

export BK_EXAMINATION="CTLCardinality"

export BK_TOOL="lolaxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool lolaxred"

echo " Input is PGCD-COL-D04N050, examination is CTLCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r519-tall-167987245300417"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/PGCD-COL-D04N050.tgz

mv PGCD-COL-D04N050 execution

cd execution

if [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "UpperBounds" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] || [ "CTLCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;