About the Execution of LoLa+red for Sudoku-COL-AN16

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16221.184 | 1424910.00 | 1481942.00 | 16443.70 | TTTTFTTF???FFFFF | normal |

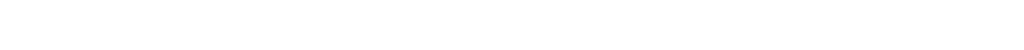

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r487-tall-167912702600123.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lolaxred

Input is Sudoku-COL-AN16, examination is LTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r487-tall-167912702600123

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 484K

-rw-r--r-- 1 mcc users 7.4K Feb 26 10:03 CTLCardinality.txt

-rw-r--r-- 1 mcc users 81K Feb 26 10:03 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.7K Feb 26 09:04 CTLFireability.txt

-rw-r--r-- 1 mcc users 61K Feb 26 09:04 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:41 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.6K Jan 29 11:41 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.7K Feb 25 17:17 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Feb 25 17:17 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.2K Feb 25 17:17 LTLFireability.txt

-rw-r--r-- 1 mcc users 16K Feb 25 17:17 LTLFireability.xml

-rw-r--r-- 1 mcc users 13K Feb 26 11:47 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 125K Feb 26 11:47 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 8.3K Feb 26 10:14 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 68K Feb 26 10:14 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 25 17:17 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Feb 25 17:17 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:23 equiv_pt

-rw-r--r-- 1 mcc users 5 Mar 5 18:23 instance

-rw-r--r-- 1 mcc users 5 Mar 5 18:23 iscolored

-rw-r--r-- 1 mcc users 6.5K Mar 5 18:23 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-00

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-01

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-02

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-03

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-04

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-05

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-06

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-07

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-08

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-09

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-10

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-11

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-12

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-13

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-14

FORMULA_NAME Sudoku-COL-AN16-LTLCardinality-15

=== Now, execution of the tool begins

BK_START 1679167917953

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lolaxred

BK_EXAMINATION=LTLCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=Sudoku-COL-AN16

Applying reductions before tool lola

Invoking reducer

Running Version 202303021504

[2023-03-18 19:31:59] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLCardinality, -timeout, 360, -rebuildPNML]

[2023-03-18 19:31:59] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-18 19:31:59] [INFO ] Detected file is not PT type :http://www.pnml.org/version-2009/grammar/symmetricnet

log4j:WARN No appenders could be found for logger (org.apache.axiom.locator.DefaultOMMetaFactoryLocator).

log4j:WARN Please initialize the log4j system properly.

log4j:WARN See http://logging.apache.org/log4j/1.2/faq.html#noconfig for more info.

[2023-03-18 19:31:59] [WARNING] Using fallBack plugin, rng conformance not checked

[2023-03-18 19:31:59] [INFO ] Load time of PNML (colored model parsed with PNMLFW) : 354 ms

[2023-03-18 19:31:59] [INFO ] Imported 4 HL places and 1 HL transitions for a total of 4864 PT places and 4096.0 transition bindings in 11 ms.

Parsed 16 properties from file /home/mcc/execution/LTLCardinality.xml in 13 ms.

Working with output stream class java.io.PrintStream

[2023-03-18 19:32:00] [INFO ] Built PT skeleton of HLPN with 4 places and 1 transitions 4 arcs in 4 ms.

[2023-03-18 19:32:00] [INFO ] Skeletonized 16 HLPN properties in 1 ms.

Initial state reduction rules removed 4 formulas.

FORMULA Sudoku-COL-AN16-LTLCardinality-03 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Sudoku-COL-AN16-LTLCardinality-05 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Sudoku-COL-AN16-LTLCardinality-14 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Sudoku-COL-AN16-LTLCardinality-15 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Computed a total of 4 stabilizing places and 1 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4 transition count 1

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Remains 12 properties that can be checked using skeleton over-approximation.

Computed a total of 4 stabilizing places and 1 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4 transition count 1

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Incomplete random walk after 10061 steps, including 38 resets, run finished after 25 ms. (steps per millisecond=402 ) properties (out of 17) seen :13

Incomplete Best-First random walk after 10061 steps, including 38 resets, run finished after 12 ms. (steps per millisecond=838 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10061 steps, including 38 resets, run finished after 9 ms. (steps per millisecond=1117 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10061 steps, including 38 resets, run finished after 9 ms. (steps per millisecond=1117 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10061 steps, including 38 resets, run finished after 7 ms. (steps per millisecond=1437 ) properties (out of 4) seen :0

Running SMT prover for 4 properties.

// Phase 1: matrix 1 rows 4 cols

[2023-03-18 19:32:00] [INFO ] Computed 3 place invariants in 2 ms

[2023-03-18 19:32:00] [INFO ] After 108ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:4

[2023-03-18 19:32:00] [INFO ] [Nat]Absence check using 3 positive place invariants in 1 ms returned sat

[2023-03-18 19:32:00] [INFO ] After 48ms SMT Verify possible using all constraints in natural domain returned unsat :4 sat :0

Fused 4 Parikh solutions to 0 different solutions.

Parikh walk visited 0 properties in 1 ms.

Successfully simplified 4 atomic propositions for a total of 12 simplifications.

FORMULA Sudoku-COL-AN16-LTLCardinality-00 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Sudoku-COL-AN16-LTLCardinality-11 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Sudoku-COL-AN16-LTLCardinality-12 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-03-18 19:32:00] [INFO ] Initial state reduction rules for LTL removed 1 formulas.

[2023-03-18 19:32:00] [INFO ] Flatten gal took : 11 ms

FORMULA Sudoku-COL-AN16-LTLCardinality-07 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-03-18 19:32:00] [INFO ] Flatten gal took : 1 ms

Domain [N(16), N(16)] of place Rows breaks symmetries in sort N

[2023-03-18 19:32:00] [INFO ] Unfolded HLPN to a Petri net with 4864 places and 4096 transitions 16384 arcs in 59 ms.

[2023-03-18 19:32:00] [INFO ] Unfolded 8 HLPN properties in 4 ms.

Support contains 4864 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 45 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

// Phase 1: matrix 4096 rows 4864 cols

[2023-03-18 19:32:00] [INFO ] Computed 768 place invariants in 60 ms

[2023-03-18 19:32:01] [INFO ] Implicit Places using invariants in 637 ms returned []

[2023-03-18 19:32:01] [INFO ] Invariant cache hit.

[2023-03-18 19:32:01] [INFO ] Implicit Places using invariants and state equation in 465 ms returned []

Implicit Place search using SMT with State Equation took 1106 ms to find 0 implicit places.

[2023-03-18 19:32:01] [INFO ] Invariant cache hit.

[2023-03-18 19:32:04] [INFO ] Dead Transitions using invariants and state equation in 2601 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 3755 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Support contains 4864 out of 4864 places after structural reductions.

[2023-03-18 19:32:04] [INFO ] Flatten gal took : 349 ms

[2023-03-18 19:32:05] [INFO ] Flatten gal took : 224 ms

[2023-03-18 19:32:06] [INFO ] Input system was already deterministic with 4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3605 ms. (steps per millisecond=2 ) properties (out of 12) seen :7

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 192 ms. (steps per millisecond=52 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 161 ms. (steps per millisecond=62 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 334 ms. (steps per millisecond=29 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 174 ms. (steps per millisecond=57 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 347 ms. (steps per millisecond=28 ) properties (out of 5) seen :0

Running SMT prover for 5 properties.

[2023-03-18 19:32:10] [INFO ] Invariant cache hit.

[2023-03-18 19:32:12] [INFO ] [Real]Absence check using 768 positive place invariants in 249 ms returned sat

java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Error writing to Z3 solver: java.io.IOException: Stream closed...

at fr.lip6.move.gal.structural.smt.SMTUtils.execAndCheckResult(SMTUtils.java:251)

at fr.lip6.move.gal.structural.smt.DeadlockTester.verifyPossible(DeadlockTester.java:629)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMTIncremental(DeadlockTester.java:339)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMT(DeadlockTester.java:223)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.applyReductions(ReachabilitySolver.java:95)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.checkAtomicPropositionsLogic(AtomicReducerSR.java:105)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.strongReductions(AtomicReducerSR.java:44)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.preSolveForLogic(LTLPropertySolver.java:176)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.runStructuralLTLCheck(LTLPropertySolver.java:71)

at fr.lip6.move.gal.application.Application.startNoEx(Application.java:762)

at fr.lip6.move.gal.application.Application.start(Application.java:178)

at fr.lip6.move.gal.itscl.application.Application.start(Application.java:45)

at org.eclipse.equinox.internal.app.EclipseAppHandle.run(EclipseAppHandle.java:203)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.runApplication(EclipseAppLauncher.java:136)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.start(EclipseAppLauncher.java:104)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:402)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:255)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native Method)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(NativeMethodAccessorImpl.java:77)

at java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

at java.base/java.lang.reflect.Method.invoke(Method.java:568)

at org.eclipse.equinox.launcher.Main.invokeFramework(Main.java:659)

at org.eclipse.equinox.launcher.Main.basicRun(Main.java:596)

at org.eclipse.equinox.launcher.Main.run(Main.java:1467)

at org.eclipse.equinox.launcher.Main.main(Main.java:1440)

[2023-03-18 19:32:36] [WARNING] SMT solver failed with error :SMT solver raised an error when submitting script.... while checking expressions.

[2023-03-18 19:32:36] [INFO ] After 25046ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Fused 5 Parikh solutions to 1 different solutions.

Parikh walk visited 0 properties in 0 ms.

Support contains 768 out of 4864 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Graph (complete) has 12288 edges and 4864 vertex of which 768 are kept as prefixes of interest. Removing 4096 places using SCC suffix rule.9 ms

Discarding 4096 places :

Also discarding 0 output transitions

Applied a total of 1 rules in 90 ms. Remains 768 /4864 variables (removed 4096) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 90 ms. Remains : 768/4864 places, 4096/4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3371 ms. (steps per millisecond=2 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 161 ms. (steps per millisecond=62 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 161 ms. (steps per millisecond=62 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 327 ms. (steps per millisecond=30 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 156 ms. (steps per millisecond=64 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 327 ms. (steps per millisecond=30 ) properties (out of 5) seen :0

Probabilistic random walk after 163905 steps, saw 163856 distinct states, run finished after 12009 ms. (steps per millisecond=13 ) properties seen :0

Running SMT prover for 5 properties.

// Phase 1: matrix 4096 rows 768 cols

[2023-03-18 19:32:53] [INFO ] Computed 47 place invariants in 511 ms

[2023-03-18 19:32:53] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 51 ms returned sat

[2023-03-18 19:32:53] [INFO ] After 246ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:5

[2023-03-18 19:32:54] [INFO ] [Nat]Absence check using 0 positive and 47 generalized place invariants in 43 ms returned sat

[2023-03-18 19:33:00] [INFO ] After 6123ms SMT Verify possible using state equation in natural domain returned unsat :2 sat :3

[2023-03-18 19:33:00] [INFO ] After 6531ms SMT Verify possible using trap constraints in natural domain returned unsat :2 sat :3

Attempting to minimize the solution found.

Minimization took 233 ms.

[2023-03-18 19:33:00] [INFO ] After 7023ms SMT Verify possible using all constraints in natural domain returned unsat :2 sat :3

Fused 5 Parikh solutions to 1 different solutions.

Finished Parikh walk after 256 steps, including 0 resets, run visited all 3 properties in 29 ms. (steps per millisecond=8 )

Parikh walk visited 3 properties in 31 ms.

Successfully simplified 2 atomic propositions for a total of 8 simplifications.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((p0||X(G(p1)))))'

Support contains 4096 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 163 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

// Phase 1: matrix 4096 rows 4864 cols

[2023-03-18 19:33:01] [INFO ] Computed 768 place invariants in 29 ms

[2023-03-18 19:33:02] [INFO ] Implicit Places using invariants in 1374 ms returned []

[2023-03-18 19:33:02] [INFO ] Invariant cache hit.

[2023-03-18 19:33:04] [INFO ] Implicit Places using invariants and state equation in 1306 ms returned []

Implicit Place search using SMT with State Equation took 2682 ms to find 0 implicit places.

[2023-03-18 19:33:04] [INFO ] Invariant cache hit.

[2023-03-18 19:33:06] [INFO ] Dead Transitions using invariants and state equation in 2657 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5505 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 224 ms :[true, (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (NOT p1)]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-01 automaton TGBA Formula[mat=[[{ cond=true, acceptance={0} source=0 dest: 0}], [{ cond=true, acceptance={} source=1 dest: 2}], [{ cond=(NOT p0), acceptance={} source=2 dest: 3}], [{ cond=(NOT p1), acceptance={} source=3 dest: 0}, { cond=p1, acceptance={} source=3 dest: 3}]], initial=1, aps=[p0:(LEQ 1 (ADD s256 s257 s258 s259 s260 s261 s262 s263 s264 s265 s266 s267 s268 s269 s270 s271 s272 s273 s274 s275 s276 s277 s278 s279 s280 s281 s282 s283...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, terminal, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null][false, false, false, false]]

Product exploration timeout after 21130 steps with 10565 reset in 10005 ms.

Product exploration timeout after 21120 steps with 10560 reset in 10004 ms.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p0) p1), (X p0), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge :(X p0)

Knowledge based reduction with 4 factoid took 73 ms. Reduced automaton from 4 states, 5 edges and 2 AP (stutter sensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA Sudoku-COL-AN16-LTLCardinality-01 TRUE TECHNIQUES KNOWLEDGE

Treatment of property Sudoku-COL-AN16-LTLCardinality-01 finished in 27469 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!((G(p0)||X((p1||F((p2&&X(F(p1))))))))'

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 45 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:33:28] [INFO ] Invariant cache hit.

[2023-03-18 19:33:29] [INFO ] Implicit Places using invariants in 750 ms returned []

[2023-03-18 19:33:29] [INFO ] Invariant cache hit.

[2023-03-18 19:33:30] [INFO ] Implicit Places using invariants and state equation in 748 ms returned []

Implicit Place search using SMT with State Equation took 1501 ms to find 0 implicit places.

[2023-03-18 19:33:30] [INFO ] Invariant cache hit.

[2023-03-18 19:33:32] [INFO ] Dead Transitions using invariants and state equation in 2621 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4169 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 289 ms :[(OR (NOT p2) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (OR (AND (NOT p0) (NOT p2)) (AND (NOT p0) (NOT p1))), (AND (NOT p1) (NOT p0)), (NOT p1), (NOT p1)]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-02 automaton TGBA Formula[mat=[[{ cond=(NOT p2), acceptance={0} source=0 dest: 0}, { cond=p2, acceptance={0} source=0 dest: 5}], [{ cond=p0, acceptance={} source=1 dest: 2}, { cond=(NOT p0), acceptance={} source=1 dest: 6}], [{ cond=(AND (NOT p0) (NOT p1) (NOT p2)), acceptance={} source=2 dest: 0}, { cond=(AND p0 (NOT p1) (NOT p2)), acceptance={} source=2 dest: 3}, { cond=(AND p0 (NOT p1) p2), acceptance={} source=2 dest: 4}, { cond=(AND (NOT p0) (NOT p1) p2), acceptance={} source=2 dest: 5}], [{ cond=(AND (NOT p0) (NOT p2)), acceptance={} source=3 dest: 0}, { cond=(AND p0 (NOT p2)), acceptance={} source=3 dest: 3}, { cond=(AND p0 p2), acceptance={} source=3 dest: 4}, { cond=(AND (NOT p0) p2), acceptance={} source=3 dest: 5}], [{ cond=(AND p0 (NOT p1)), acceptance={} source=4 dest: 4}, { cond=(AND (NOT p0) (NOT p1)), acceptance={} source=4 dest: 5}], [{ cond=(NOT p1), acceptance={0} source=5 dest: 5}], [{ cond=(AND (NOT p1) (NOT p2)), acceptance={} source=6 dest: 0}, { cond=(AND (NOT p1) p2), acceptance={} source=6 dest: 5}]], initial=1, aps=[p2:(LEQ (ADD s0 s1 s2 s3 s4 s5 s6 s7 s8 s9 s10 s11 s12 s13 s14 s15 s16 s17 s18 s19 s20 s21 s22 s23 s24 s25 s26 s27 s28 s29 s30 s31 s32 s33 s34 s35 s36 s37...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null, null, null][false, false, false, false, false, false, false]]

Product exploration timeout after 17040 steps with 8520 reset in 10005 ms.

Product exploration timeout after 16880 steps with 8440 reset in 10006 ms.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p2) (NOT p0) p1), (X (NOT (AND (NOT p0) (NOT p1) p2))), (X (NOT (AND (NOT p1) p2))), (X (NOT (AND p0 (NOT p1) p2))), (X (NOT (AND (NOT p1) (NOT p2)))), (X (NOT (AND p0 (NOT p1) (NOT p2)))), (X (NOT (AND (NOT p0) (NOT p1) (NOT p2)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge :(X (NOT (AND (NOT p1) (NOT p2))))

Knowledge based reduction with 10 factoid took 193 ms. Reduced automaton from 7 states, 17 edges and 3 AP (stutter sensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA Sudoku-COL-AN16-LTLCardinality-02 TRUE TECHNIQUES KNOWLEDGE

Treatment of property Sudoku-COL-AN16-LTLCardinality-02 finished in 28699 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((p0 U p1)))'

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 28 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:33:57] [INFO ] Invariant cache hit.

[2023-03-18 19:33:58] [INFO ] Implicit Places using invariants in 752 ms returned []

[2023-03-18 19:33:58] [INFO ] Invariant cache hit.

[2023-03-18 19:33:59] [INFO ] Implicit Places using invariants and state equation in 735 ms returned []

Implicit Place search using SMT with State Equation took 1489 ms to find 0 implicit places.

[2023-03-18 19:33:59] [INFO ] Invariant cache hit.

[2023-03-18 19:34:01] [INFO ] Dead Transitions using invariants and state equation in 2556 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4075 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 82 ms :[(NOT p1), (NOT p1), true]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-04 automaton TGBA Formula[mat=[[{ cond=(AND (NOT p1) p0), acceptance={0} source=0 dest: 0}, { cond=(AND (NOT p1) (NOT p0)), acceptance={0} source=0 dest: 2}], [{ cond=true, acceptance={} source=1 dest: 0}], [{ cond=true, acceptance={0} source=2 dest: 2}]], initial=1, aps=[p1:(LEQ (ADD s4352 s4353 s4354 s4355 s4356 s4357 s4358 s4359 s4360 s4361 s4362 s4363 s4364 s4365 s4366 s4367 s4368 s4369 s4370 s4371 s4372 s4373 s4374 s43...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null, null][false, false, false]]

Entered a terminal (fully accepting) state of product in 1 steps with 0 reset in 3 ms.

FORMULA Sudoku-COL-AN16-LTLCardinality-04 FALSE TECHNIQUES STUTTER_TEST

Treatment of property Sudoku-COL-AN16-LTLCardinality-04 finished in 4208 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((p0||F(G((!p0||(p1 U p2)))))))'

Support contains 4352 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 107 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:34:01] [INFO ] Invariant cache hit.

[2023-03-18 19:34:02] [INFO ] Implicit Places using invariants in 1015 ms returned []

[2023-03-18 19:34:02] [INFO ] Invariant cache hit.

[2023-03-18 19:34:03] [INFO ] Implicit Places using invariants and state equation in 1010 ms returned []

Implicit Place search using SMT with State Equation took 2027 ms to find 0 implicit places.

[2023-03-18 19:34:03] [INFO ] Invariant cache hit.

[2023-03-18 19:34:06] [INFO ] Dead Transitions using invariants and state equation in 2620 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4757 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 146 ms :[false, (AND p0 (NOT p2)), (AND p0 (NOT p2)), false]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-06 automaton TGBA Formula[mat=[[{ cond=(NOT p0), acceptance={} source=0 dest: 1}], [{ cond=(OR (NOT p0) p2 p1), acceptance={} source=1 dest: 1}, { cond=(AND p0 (NOT p2) (NOT p1)), acceptance={0} source=1 dest: 1}, { cond=(AND p0 (NOT p2) p1), acceptance={0} source=1 dest: 2}], [{ cond=(AND (NOT p0) (NOT p2) (NOT p1)), acceptance={} source=2 dest: 1}, { cond=(AND p0 (NOT p2) (NOT p1)), acceptance={0} source=2 dest: 1}, { cond=(AND (NOT p0) (NOT p2) p1), acceptance={} source=2 dest: 2}, { cond=(AND p0 (NOT p2) p1), acceptance={0} source=2 dest: 2}], [{ cond=true, acceptance={} source=3 dest: 0}]], initial=3, aps=[p0:(GT 1 (ADD s4352 s4353 s4354 s4355 s4356 s4357 s4358 s4359 s4360 s4361 s4362 s4363 s4364 s4365 s4366 s4367 s4368 s4369 s4370 s4371 s4372 s4373 s4374 s4...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-sensitive], stateDesc=[null, null, null, null][false, false, false, false]]

Product exploration timeout after 34800 steps with 154 reset in 10004 ms.

Product exploration timeout after 34500 steps with 152 reset in 10002 ms.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p0) (NOT p2) p1), (X (NOT p0)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge sufficient to adopt a stutter insensitive property.

Knowledge based reduction with 5 factoid took 250 ms. Reduced automaton from 4 states, 9 edges and 3 AP (stutter sensitive) to 2 states, 7 edges and 3 AP (stutter insensitive).

Stuttering acceptance computed with spot in 81 ms :[(AND p0 (NOT p2)), (AND p0 (NOT p2))]

Incomplete random walk after 10000 steps, including 44 resets, run finished after 4872 ms. (steps per millisecond=2 ) properties (out of 5) seen :1

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1335 ms. (steps per millisecond=7 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1321 ms. (steps per millisecond=7 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1216 ms. (steps per millisecond=8 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1213 ms. (steps per millisecond=8 ) properties (out of 4) seen :0

Running SMT prover for 4 properties.

[2023-03-18 19:34:38] [INFO ] Invariant cache hit.

[2023-03-18 19:34:40] [INFO ] After 639ms SMT Verify possible using all constraints in real domain returned unsat :1 sat :0 real:3

[2023-03-18 19:34:41] [INFO ] [Nat]Absence check using 768 positive place invariants in 260 ms returned sat

[2023-03-18 19:34:41] [INFO ] After 935ms SMT Verify possible using all constraints in natural domain returned unsat :4 sat :0

Fused 4 Parikh solutions to 0 different solutions.

Parikh walk visited 0 properties in 0 ms.

Found 4 invariant AP formulas.

Knowledge obtained : [(AND (NOT p0) (NOT p2) p1), (X (NOT p0)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p2) (G (NOT p2)))), (F (OR (G p1) (G (NOT p1)))), (G (NOT (AND (NOT p2) (NOT p1) (NOT p0)))), (G (OR p2 p1 (NOT p0))), (G (NOT (AND (NOT p2) p1 p0))), (G (NOT (AND (NOT p2) (NOT p1) p0)))]

False Knowledge obtained : [(F (NOT (AND (NOT p2) p1 (NOT p0))))]

Property proved to be true thanks to knowledge :(G (NOT (AND (NOT p2) p1 p0)))

Knowledge based reduction with 9 factoid took 241 ms. Reduced automaton from 2 states, 7 edges and 3 AP (stutter insensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA Sudoku-COL-AN16-LTLCardinality-06 TRUE TECHNIQUES KNOWLEDGE

Treatment of property Sudoku-COL-AN16-LTLCardinality-06 finished in 39975 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(F(p0)))'

Support contains 256 out of 4864 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Graph (complete) has 12288 edges and 4864 vertex of which 768 are kept as prefixes of interest. Removing 4096 places using SCC suffix rule.19 ms

Discarding 4096 places :

Also discarding 0 output transitions

Applied a total of 1 rules in 307 ms. Remains 768 /4864 variables (removed 4096) and now considering 4096/4096 (removed 0) transitions.

// Phase 1: matrix 4096 rows 768 cols

[2023-03-18 19:34:42] [INFO ] Computed 47 place invariants in 283 ms

[2023-03-18 19:34:42] [INFO ] Implicit Places using invariants in 862 ms returned []

[2023-03-18 19:34:42] [INFO ] Invariant cache hit.

[2023-03-18 19:34:46] [INFO ] Implicit Places using invariants and state equation in 3454 ms returned []

Implicit Place search using SMT with State Equation took 4321 ms to find 0 implicit places.

[2023-03-18 19:34:46] [INFO ] Redundant transitions in 271 ms returned []

[2023-03-18 19:34:46] [INFO ] Invariant cache hit.

[2023-03-18 19:34:47] [INFO ] Dead Transitions using invariants and state equation in 1153 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 768/4864 places, 4096/4096 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 6065 ms. Remains : 768/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 67 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-08 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={} source=0 dest: 1}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p0:(LEQ 2 (ADD s0 s1 s2 s3 s4 s5 s6 s7 s8 s9 s10 s11 s12 s13 s14 s15 s16 s17 s18 s19 s20 s21 s22 s23 s24 s25 s26 s27 s28 s29 s30 s31 s32 s33 s34 s35 s36 s...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-invariant, very-weak, weak, inherently-weak], stateDesc=[null, null][true, true]]

Product exploration timeout after 37870 steps with 167 reset in 10002 ms.

Product exploration timeout after 37570 steps with 166 reset in 10003 ms.

Computed a total of 768 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 768 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [p0, (X p0), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 120 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 77 ms :[(NOT p0), (NOT p0)]

Incomplete random walk after 10000 steps, including 44 resets, run finished after 2633 ms. (steps per millisecond=3 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 170 ms. (steps per millisecond=58 ) properties (out of 1) seen :0

Interrupted probabilistic random walk after 295642 steps, run timeout after 6004 ms. (steps per millisecond=49 ) properties seen :{}

Probabilistic random walk after 295642 steps, saw 295539 distinct states, run finished after 6005 ms. (steps per millisecond=49 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:35:17] [INFO ] Invariant cache hit.

[2023-03-18 19:35:17] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 41 ms returned sat

[2023-03-18 19:35:29] [INFO ] After 11603ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 65 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 65 ms. Remains : 768/768 places, 4096/4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 2695 ms. (steps per millisecond=3 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 168 ms. (steps per millisecond=59 ) properties (out of 1) seen :0

Probabilistic random walk after 291556 steps, saw 291457 distinct states, run finished after 6009 ms. (steps per millisecond=48 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:35:38] [INFO ] Invariant cache hit.

[2023-03-18 19:35:38] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 42 ms returned sat

[2023-03-18 19:35:49] [INFO ] After 11628ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 66 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 66 ms. Remains : 768/768 places, 4096/4096 transitions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 55 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:35:49] [INFO ] Invariant cache hit.

[2023-03-18 19:35:50] [INFO ] Implicit Places using invariants in 576 ms returned []

[2023-03-18 19:35:50] [INFO ] Invariant cache hit.

[2023-03-18 19:35:55] [INFO ] Implicit Places using invariants and state equation in 5135 ms returned []

Implicit Place search using SMT with State Equation took 5713 ms to find 0 implicit places.

[2023-03-18 19:35:55] [INFO ] Redundant transitions in 236 ms returned []

[2023-03-18 19:35:55] [INFO ] Invariant cache hit.

[2023-03-18 19:35:57] [INFO ] Dead Transitions using invariants and state equation in 1178 ms found 0 transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 7188 ms. Remains : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 52 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Running SMT prover for 1 properties.

[2023-03-18 19:35:57] [INFO ] Invariant cache hit.

[2023-03-18 19:35:57] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 43 ms returned sat

[2023-03-18 19:36:08] [INFO ] After 11303ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:36:08] [INFO ] [Nat]Absence check using 0 positive and 47 generalized place invariants in 42 ms returned sat

[2023-03-18 19:36:16] [INFO ] After 7403ms SMT Verify possible using state equation in natural domain returned unsat :0 sat :1

[2023-03-18 19:36:16] [INFO ] After 7540ms SMT Verify possible using trap constraints in natural domain returned unsat :0 sat :1

Attempting to minimize the solution found.

Minimization took 76 ms.

[2023-03-18 19:36:16] [INFO ] After 7763ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :1

Knowledge obtained : [p0, (X p0), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 96 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 78 ms :[(NOT p0), (NOT p0)]

Stuttering acceptance computed with spot in 70 ms :[(NOT p0), (NOT p0)]

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 78 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:36:16] [INFO ] Invariant cache hit.

[2023-03-18 19:36:17] [INFO ] Implicit Places using invariants in 540 ms returned []

[2023-03-18 19:36:17] [INFO ] Invariant cache hit.

[2023-03-18 19:36:21] [INFO ] Implicit Places using invariants and state equation in 4330 ms returned []

Implicit Place search using SMT with State Equation took 4870 ms to find 0 implicit places.

[2023-03-18 19:36:21] [INFO ] Redundant transitions in 155 ms returned []

[2023-03-18 19:36:21] [INFO ] Invariant cache hit.

[2023-03-18 19:36:22] [INFO ] Dead Transitions using invariants and state equation in 1149 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 6264 ms. Remains : 768/768 places, 4096/4096 transitions.

Computed a total of 768 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 768 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [p0, (X p0), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 133 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 74 ms :[(NOT p0), (NOT p0)]

Incomplete random walk after 10000 steps, including 44 resets, run finished after 2655 ms. (steps per millisecond=3 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 170 ms. (steps per millisecond=58 ) properties (out of 1) seen :0

Probabilistic random walk after 297641 steps, saw 297539 distinct states, run finished after 6006 ms. (steps per millisecond=49 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:36:32] [INFO ] Invariant cache hit.

[2023-03-18 19:36:32] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 42 ms returned sat

[2023-03-18 19:36:45] [INFO ] After 12408ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 67 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 68 ms. Remains : 768/768 places, 4096/4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 2658 ms. (steps per millisecond=3 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 176 ms. (steps per millisecond=56 ) properties (out of 1) seen :0

Probabilistic random walk after 291556 steps, saw 291457 distinct states, run finished after 6013 ms. (steps per millisecond=48 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:36:53] [INFO ] Invariant cache hit.

[2023-03-18 19:36:54] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 42 ms returned sat

[2023-03-18 19:37:06] [INFO ] After 12067ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 47 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 48 ms. Remains : 768/768 places, 4096/4096 transitions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 44 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:37:06] [INFO ] Invariant cache hit.

[2023-03-18 19:37:06] [INFO ] Implicit Places using invariants in 592 ms returned []

[2023-03-18 19:37:06] [INFO ] Invariant cache hit.

[2023-03-18 19:37:11] [INFO ] Implicit Places using invariants and state equation in 4797 ms returned []

Implicit Place search using SMT with State Equation took 5391 ms to find 0 implicit places.

[2023-03-18 19:37:11] [INFO ] Redundant transitions in 155 ms returned []

[2023-03-18 19:37:11] [INFO ] Invariant cache hit.

[2023-03-18 19:37:12] [INFO ] Dead Transitions using invariants and state equation in 1155 ms found 0 transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 6752 ms. Remains : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 42 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Running SMT prover for 1 properties.

[2023-03-18 19:37:12] [INFO ] Invariant cache hit.

[2023-03-18 19:37:13] [INFO ] [Real]Absence check using 0 positive and 47 generalized place invariants in 42 ms returned sat

[2023-03-18 19:37:24] [INFO ] After 11551ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Knowledge obtained : [p0, (X p0), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 123 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 72 ms :[(NOT p0), (NOT p0)]

Stuttering acceptance computed with spot in 67 ms :[(NOT p0), (NOT p0)]

Stuttering acceptance computed with spot in 68 ms :[(NOT p0), (NOT p0)]

Product exploration timeout after 38210 steps with 169 reset in 10004 ms.

Product exploration timeout after 38040 steps with 168 reset in 10004 ms.

Support contains 256 out of 768 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 768/768 places, 4096/4096 transitions.

Applied a total of 0 rules in 55 ms. Remains 768 /768 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:37:44] [INFO ] Invariant cache hit.

[2023-03-18 19:37:45] [INFO ] Implicit Places using invariants in 575 ms returned []

[2023-03-18 19:37:45] [INFO ] Invariant cache hit.

[2023-03-18 19:37:49] [INFO ] Implicit Places using invariants and state equation in 4417 ms returned []

Implicit Place search using SMT with State Equation took 4994 ms to find 0 implicit places.

[2023-03-18 19:37:50] [INFO ] Redundant transitions in 157 ms returned []

[2023-03-18 19:37:50] [INFO ] Invariant cache hit.

[2023-03-18 19:37:51] [INFO ] Dead Transitions using invariants and state equation in 1142 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 6360 ms. Remains : 768/768 places, 4096/4096 transitions.

Treatment of property Sudoku-COL-AN16-LTLCardinality-08 finished in 190245 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(F((p0&&(F(G(p1)) U p1))))))'

Support contains 4352 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 40 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

// Phase 1: matrix 4096 rows 4864 cols

[2023-03-18 19:37:51] [INFO ] Computed 768 place invariants in 16 ms

[2023-03-18 19:37:52] [INFO ] Implicit Places using invariants in 1015 ms returned []

[2023-03-18 19:37:52] [INFO ] Invariant cache hit.

[2023-03-18 19:37:54] [INFO ] Implicit Places using invariants and state equation in 1010 ms returned []

Implicit Place search using SMT with State Equation took 2027 ms to find 0 implicit places.

[2023-03-18 19:37:54] [INFO ] Invariant cache hit.

[2023-03-18 19:37:56] [INFO ] Dead Transitions using invariants and state equation in 2590 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4665 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 143 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-09 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 1}], [{ cond=true, acceptance={} source=1 dest: 2}], [{ cond=(NOT p0), acceptance={0} source=2 dest: 2}, { cond=(AND p0 (NOT p1)), acceptance={} source=2 dest: 3}], [{ cond=(AND (NOT p0) p1), acceptance={} source=3 dest: 3}, { cond=(NOT p1), acceptance={0} source=3 dest: 3}]], initial=0, aps=[p0:(LEQ (ADD s256 s257 s258 s259 s260 s261 s262 s263 s264 s265 s266 s267 s268 s269 s270 s271 s272 s273 s274 s275 s276 s277 s278 s279 s280 s281 s282 s283 s...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive], stateDesc=[null, null, null, null][false, false, false, false]]

Product exploration timeout after 14340 steps with 3585 reset in 10004 ms.

Product exploration timeout after 14320 steps with 3580 reset in 10005 ms.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 132 ms. Reduced automaton from 4 states, 6 edges and 2 AP (stutter sensitive) to 4 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 165 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Finished random walk after 129 steps, including 0 resets, run visited all 4 properties in 91 ms. (steps per millisecond=1 )

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : [(F p1), (F (NOT p0)), (F (AND (NOT p0) p1)), (F (NOT (AND p0 (NOT p1))))]

Knowledge based reduction with 3 factoid took 197 ms. Reduced automaton from 4 states, 6 edges and 2 AP (stutter sensitive) to 4 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 132 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Stuttering acceptance computed with spot in 134 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

[2023-03-18 19:38:20] [INFO ] Invariant cache hit.

Could not prove EG (NOT p1)

Support contains 4352 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 36 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:38:35] [INFO ] Invariant cache hit.

[2023-03-18 19:38:36] [INFO ] Implicit Places using invariants in 981 ms returned []

[2023-03-18 19:38:36] [INFO ] Invariant cache hit.

[2023-03-18 19:38:37] [INFO ] Implicit Places using invariants and state equation in 995 ms returned []

Implicit Place search using SMT with State Equation took 1977 ms to find 0 implicit places.

[2023-03-18 19:38:37] [INFO ] Invariant cache hit.

[2023-03-18 19:38:40] [INFO ] Dead Transitions using invariants and state equation in 2552 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4566 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 130 ms. Reduced automaton from 4 states, 6 edges and 2 AP (stutter sensitive) to 4 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 152 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Finished random walk after 129 steps, including 0 resets, run visited all 4 properties in 88 ms. (steps per millisecond=1 )

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : [(F p1), (F (NOT p0)), (F (AND (NOT p0) p1)), (F (NOT (AND p0 (NOT p1))))]

Knowledge based reduction with 3 factoid took 177 ms. Reduced automaton from 4 states, 6 edges and 2 AP (stutter sensitive) to 4 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 116 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Stuttering acceptance computed with spot in 163 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

[2023-03-18 19:38:44] [INFO ] Invariant cache hit.

Could not prove EG (NOT p1)

Stuttering acceptance computed with spot in 139 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Product exploration timeout after 14230 steps with 3557 reset in 10002 ms.

Product exploration timeout after 14250 steps with 3562 reset in 10004 ms.

Applying partial POR strategy [false, false, true, true]

Stuttering acceptance computed with spot in 143 ms :[(OR (NOT p1) (NOT p0)), (OR (NOT p0) (NOT p1)), (OR (NOT p0) (NOT p1)), (NOT p1)]

Support contains 4352 out of 4864 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 167 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:39:19] [INFO ] Redundant transitions in 156 ms returned []

[2023-03-18 19:39:19] [INFO ] Invariant cache hit.

[2023-03-18 19:39:22] [INFO ] Dead Transitions using invariants and state equation in 2583 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 2914 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Support contains 4352 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 40 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:39:22] [INFO ] Invariant cache hit.

[2023-03-18 19:39:23] [INFO ] Implicit Places using invariants in 1003 ms returned []

[2023-03-18 19:39:23] [INFO ] Invariant cache hit.

[2023-03-18 19:39:24] [INFO ] Implicit Places using invariants and state equation in 994 ms returned []

Implicit Place search using SMT with State Equation took 1999 ms to find 0 implicit places.

[2023-03-18 19:39:24] [INFO ] Invariant cache hit.

[2023-03-18 19:39:27] [INFO ] Dead Transitions using invariants and state equation in 2579 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4618 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Treatment of property Sudoku-COL-AN16-LTLCardinality-09 finished in 95496 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(X((F(p0)||G(p1))))))'

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 21 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:39:27] [INFO ] Invariant cache hit.

[2023-03-18 19:39:28] [INFO ] Implicit Places using invariants in 729 ms returned []

[2023-03-18 19:39:28] [INFO ] Invariant cache hit.

[2023-03-18 19:39:28] [INFO ] Implicit Places using invariants and state equation in 724 ms returned []

Implicit Place search using SMT with State Equation took 1457 ms to find 0 implicit places.

[2023-03-18 19:39:28] [INFO ] Invariant cache hit.

[2023-03-18 19:39:31] [INFO ] Dead Transitions using invariants and state equation in 2551 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4030 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Stuttering acceptance computed with spot in 175 ms :[(NOT p0), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

Running random walk in product with property : Sudoku-COL-AN16-LTLCardinality-10 automaton TGBA Formula[mat=[[{ cond=(NOT p0), acceptance={0} source=0 dest: 0}], [{ cond=(AND (NOT p0) (NOT p1)), acceptance={} source=1 dest: 0}, { cond=(AND (NOT p0) p1), acceptance={} source=1 dest: 1}], [{ cond=true, acceptance={} source=2 dest: 1}], [{ cond=true, acceptance={} source=3 dest: 4}], [{ cond=true, acceptance={} source=4 dest: 2}]], initial=3, aps=[p0:(LEQ (ADD s256 s257 s258 s259 s260 s261 s262 s263 s264 s265 s266 s267 s268 s269 s270 s271 s272 s273 s274 s275 s276 s277 s278 s279 s280 s281 s282 s283 s...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null][false, false, false, false, false]]

Product exploration timeout after 15450 steps with 3862 reset in 10007 ms.

Product exploration timeout after 15340 steps with 3835 reset in 10001 ms.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 138 ms. Reduced automaton from 5 states, 6 edges and 2 AP (stutter sensitive) to 5 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 185 ms :[(NOT p0), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3672 ms. (steps per millisecond=2 ) properties (out of 3) seen :2

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1238 ms. (steps per millisecond=8 ) properties (out of 1) seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:39:58] [INFO ] Invariant cache hit.

[2023-03-18 19:39:59] [INFO ] After 447ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:39:59] [INFO ] [Nat]Absence check using 768 positive place invariants in 249 ms returned sat

[2023-03-18 19:40:24] [INFO ] After 25027ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 38 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 38 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3628 ms. (steps per millisecond=2 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1238 ms. (steps per millisecond=8 ) properties (out of 1) seen :0

Probabilistic random walk after 111393 steps, saw 111364 distinct states, run finished after 12107 ms. (steps per millisecond=9 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:40:41] [INFO ] Invariant cache hit.

[2023-03-18 19:40:42] [INFO ] After 457ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:40:42] [INFO ] [Nat]Absence check using 768 positive place invariants in 241 ms returned sat

[2023-03-18 19:41:07] [INFO ] After 25026ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 42 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 42 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 31 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:41:07] [INFO ] Invariant cache hit.

[2023-03-18 19:41:07] [INFO ] Implicit Places using invariants in 737 ms returned []

[2023-03-18 19:41:07] [INFO ] Invariant cache hit.

[2023-03-18 19:41:08] [INFO ] Implicit Places using invariants and state equation in 738 ms returned []

Implicit Place search using SMT with State Equation took 1478 ms to find 0 implicit places.

[2023-03-18 19:41:08] [INFO ] Redundant transitions in 160 ms returned []

[2023-03-18 19:41:08] [INFO ] Invariant cache hit.

[2023-03-18 19:41:11] [INFO ] Dead Transitions using invariants and state equation in 2461 ms found 0 transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 4145 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 32 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Running SMT prover for 1 properties.

[2023-03-18 19:41:11] [INFO ] Invariant cache hit.

[2023-03-18 19:41:12] [INFO ] After 458ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:41:12] [INFO ] [Nat]Absence check using 768 positive place invariants in 235 ms returned sat

[2023-03-18 19:44:57] [INFO ] After 225024ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : [(F (NOT p0)), (F (AND (NOT p0) (NOT p1)))]

Knowledge based reduction with 3 factoid took 152 ms. Reduced automaton from 5 states, 6 edges and 2 AP (stutter sensitive) to 5 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 158 ms :[(NOT p0), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

Stuttering acceptance computed with spot in 173 ms :[(NOT p0), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 19 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

[2023-03-18 19:44:57] [INFO ] Invariant cache hit.

[2023-03-18 19:44:58] [INFO ] Implicit Places using invariants in 743 ms returned []

[2023-03-18 19:44:58] [INFO ] Invariant cache hit.

[2023-03-18 19:44:59] [INFO ] Implicit Places using invariants and state equation in 750 ms returned []

Implicit Place search using SMT with State Equation took 1495 ms to find 0 implicit places.

[2023-03-18 19:44:59] [INFO ] Invariant cache hit.

[2023-03-18 19:45:01] [INFO ] Dead Transitions using invariants and state equation in 2559 ms found 0 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4073 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Computed a total of 4864 stabilizing places and 4096 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 4864 transition count 4096

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p0 (NOT p1)), (F (OR (G p0) (G (NOT p0)))), (F (OR (G p1) (G (NOT p1))))]

False Knowledge obtained : []

Knowledge based reduction with 3 factoid took 127 ms. Reduced automaton from 5 states, 6 edges and 2 AP (stutter sensitive) to 5 states, 6 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 172 ms :[(NOT p0), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1)), (AND (NOT p0) (NOT p1))]

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3618 ms. (steps per millisecond=2 ) properties (out of 3) seen :2

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1247 ms. (steps per millisecond=8 ) properties (out of 1) seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:45:08] [INFO ] Invariant cache hit.

[2023-03-18 19:45:08] [INFO ] After 462ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:45:09] [INFO ] [Nat]Absence check using 768 positive place invariants in 249 ms returned sat

[2023-03-18 19:45:33] [INFO ] After 25021ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0

Parikh walk visited 0 properties in 0 ms.

Support contains 4608 out of 4864 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 4864/4864 places, 4096/4096 transitions.

Applied a total of 0 rules in 39 ms. Remains 4864 /4864 variables (removed 0) and now considering 4096/4096 (removed 0) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 39 ms. Remains : 4864/4864 places, 4096/4096 transitions.

Incomplete random walk after 10000 steps, including 44 resets, run finished after 3592 ms. (steps per millisecond=2 ) properties (out of 1) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 1224 ms. (steps per millisecond=8 ) properties (out of 1) seen :0

Probabilistic random walk after 111393 steps, saw 111364 distinct states, run finished after 12026 ms. (steps per millisecond=9 ) properties seen :0

Running SMT prover for 1 properties.

[2023-03-18 19:45:50] [INFO ] Invariant cache hit.

[2023-03-18 19:45:51] [INFO ] After 466ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:1

[2023-03-18 19:45:52] [INFO ] [Nat]Absence check using 768 positive place invariants in 254 ms returned sat

[2023-03-18 19:46:16] [INFO ] After 25024ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0