About the Execution of LTSMin+red for StigmergyCommit-PT-11b

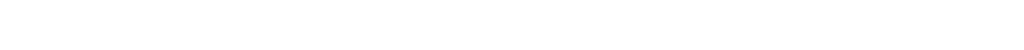

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15014.224 | 1800000.00 | 1901973.00 | 9632.80 | [undef] | Time out reached |

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r471-smll-167912659900341.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool ltsminxred

Input is StigmergyCommit-PT-11b, examination is ReachabilityDeadlock

Time confinement is 1800 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r471-smll-167912659900341

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.4G

-rw-r--r-- 1 mcc users 6.2K Feb 26 12:47 CTLCardinality.txt

-rw-r--r-- 1 mcc users 59K Feb 26 12:47 CTLCardinality.xml

-rw-r--r-- 1 mcc users 4.9K Feb 26 12:19 CTLFireability.txt

-rw-r--r-- 1 mcc users 40K Feb 26 12:19 CTLFireability.xml

-rw-r--r-- 1 mcc users 3.9K Feb 25 17:13 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Feb 25 17:13 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.4K Feb 25 17:13 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 17:13 LTLFireability.xml

-rw-r--r-- 1 mcc users 12K Feb 26 13:36 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 118K Feb 26 13:36 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 7.7K Feb 26 13:12 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 58K Feb 26 13:12 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K Feb 25 17:13 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K Feb 25 17:13 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 5 18:23 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 iscolored

-rw-r--r-- 1 mcc users 1.4G Mar 5 18:23 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

FORMULA_NAME ReachabilityDeadlock

=== Now, execution of the tool begins

BK_START 1679390520026

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=ReachabilityDeadlock

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=1800

BK_INPUT=StigmergyCommit-PT-11b

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202303021504

[2023-03-21 09:22:10] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityDeadlock, -timeout, 180, -rebuildPNML]

[2023-03-21 09:22:10] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-21 09:23:03] [INFO ] Load time of PNML (sax parser for PT used): 52361 ms

[2023-03-21 09:23:04] [INFO ] Transformed 3655 places.

[2023-03-21 09:23:08] [INFO ] Transformed 1070836 transitions.

[2023-03-21 09:23:09] [INFO ] Found NUPN structural information;

[2023-03-21 09:23:09] [INFO ] Parsed PT model containing 3655 places and 1070836 transitions and 25615632 arcs in 58165 ms.

Parsed 1 properties from file /home/mcc/execution/ReachabilityDeadlock.xml in 3 ms.

Working with output stream class java.io.PrintStream

Built sparse matrix representations for Structural reductions in 349 ms.6380859KB memory used

Starting structural reductions in DEADLOCK mode, iteration 0 : 3655/3655 places, 1070836/1070836 transitions.

Graph (trivial) has 3630 edges and 3655 vertex of which 252 / 3655 are part of one of the 36 SCC in 69 ms

Free SCC test removed 216 places

Ensure Unique test removed 240 transitions

Reduce isomorphic transitions removed 240 transitions.

Computed a total of 638 stabilizing places and 662 stable transitions

Computed a total of 638 stabilizing places and 662 stable transitions

Drop transitions removed 2748 transitions

Trivial Post-agglo rules discarded 2748 transitions

Performed 2748 trivial Post agglomeration. Transition count delta: 2748

Iterating post reduction 0 with 2748 rules applied. Total rules applied 2749 place count 3439 transition count 1067848

Reduce places removed 2748 places and 0 transitions.

Ensure Unique test removed 36 transitions

Reduce isomorphic transitions removed 36 transitions.

Computed a total of 193 stabilizing places and 217 stable transitions

Drop transitions removed 12 transitions

Trivial Post-agglo rules discarded 12 transitions

Performed 12 trivial Post agglomeration. Transition count delta: 12

Iterating post reduction 1 with 2796 rules applied. Total rules applied 5545 place count 691 transition count 1067800

Reduce places removed 12 places and 0 transitions.

Computed a total of 193 stabilizing places and 217 stable transitions

Iterating post reduction 2 with 12 rules applied. Total rules applied 5557 place count 679 transition count 1067800

Computed a total of 193 stabilizing places and 217 stable transitions

Performed 132 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 132 Pre rules applied. Total rules applied 5557 place count 679 transition count 1067668

Deduced a syphon composed of 132 places in 1703 ms

Reduce places removed 132 places and 0 transitions.

Iterating global reduction 3 with 264 rules applied. Total rules applied 5821 place count 547 transition count 1067668

Computed a total of 133 stabilizing places and 157 stable transitions

Discarding 146 places :

Symmetric choice reduction at 3 with 146 rule applications. Total rules 5967 place count 401 transition count 1067510

Iterating global reduction 3 with 146 rules applied. Total rules applied 6113 place count 401 transition count 1067510

Computed a total of 108 stabilizing places and 132 stable transitions

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 1 Pre rules applied. Total rules applied 6113 place count 401 transition count 1067509

Deduced a syphon composed of 1 places in 1626 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 3 with 2 rules applied. Total rules applied 6115 place count 400 transition count 1067509

Computed a total of 108 stabilizing places and 132 stable transitions

TIME LIMIT: Killed by timeout after 1800 seconds

MemTotal: 16393216 kB

MemFree: 5174380 kB

After kill :

MemTotal: 16393216 kB

MemFree: 15070684 kB

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityDeadlock -timeout 180 -rebuildPNML

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="StigmergyCommit-PT-11b"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="ltsminxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="1800"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool ltsminxred"

echo " Input is StigmergyCommit-PT-11b, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r471-smll-167912659900341"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/StigmergyCommit-PT-11b.tgz

mv StigmergyCommit-PT-11b execution

cd execution

if [ "ReachabilityDeadlock" = "ReachabilityDeadlock" ] || [ "ReachabilityDeadlock" = "UpperBounds" ] || [ "ReachabilityDeadlock" = "QuasiLiveness" ] || [ "ReachabilityDeadlock" = "StableMarking" ] || [ "ReachabilityDeadlock" = "Liveness" ] || [ "ReachabilityDeadlock" = "OneSafe" ] || [ "ReachabilityDeadlock" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityDeadlock" = "ReachabilityDeadlock" ] || [ "ReachabilityDeadlock" = "QuasiLiveness" ] || [ "ReachabilityDeadlock" = "StableMarking" ] || [ "ReachabilityDeadlock" = "Liveness" ] || [ "ReachabilityDeadlock" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityDeadlock"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;