About the Execution of ITS-Tools for LamportFastMutEx-COL-6

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 688.995 | 13139.00 | 30245.00 | 209.20 | FFFTFTTFTTTTTTTT | normal |

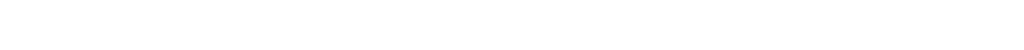

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r229-tall-167856413200374.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

..................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool itstools

Input is LamportFastMutEx-COL-6, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r229-tall-167856413200374

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 484K

-rw-r--r-- 1 mcc users 7.1K Feb 25 13:41 CTLCardinality.txt

-rw-r--r-- 1 mcc users 70K Feb 25 13:41 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.1K Feb 25 13:40 CTLFireability.txt

-rw-r--r-- 1 mcc users 50K Feb 25 13:40 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.6K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.1K Feb 25 16:20 LTLCardinality.txt

-rw-r--r-- 1 mcc users 28K Feb 25 16:20 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K Feb 25 16:20 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 16:20 LTLFireability.xml

-rw-r--r-- 1 mcc users 8.2K Feb 25 13:44 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 73K Feb 25 13:44 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 13K Feb 25 13:43 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 97K Feb 25 13:43 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K Feb 25 16:20 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K Feb 25 16:20 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 equiv_pt

-rw-r--r-- 1 mcc users 2 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 42K Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-00

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-01

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-02

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-03

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-04

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-05

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-06

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-07

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-08

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-09

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-10

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-11

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-12

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-13

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-14

FORMULA_NAME LamportFastMutEx-COL-6-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1679475495495

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=itstools

BK_EXAMINATION=ReachabilityCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=LamportFastMutEx-COL-6

Not applying reductions.

Model is COL

ReachabilityCardinality COL

Running Version 202303021504

[2023-03-22 08:58:17] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2023-03-22 08:58:17] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-22 08:58:17] [INFO ] Detected file is not PT type :http://www.pnml.org/version-2009/grammar/symmetricnet

log4j:WARN No appenders could be found for logger (org.apache.axiom.locator.DefaultOMMetaFactoryLocator).

log4j:WARN Please initialize the log4j system properly.

log4j:WARN See http://logging.apache.org/log4j/1.2/faq.html#noconfig for more info.

[2023-03-22 08:58:17] [WARNING] Using fallBack plugin, rng conformance not checked

[2023-03-22 08:58:17] [INFO ] Load time of PNML (colored model parsed with PNMLFW) : 453 ms

[2023-03-22 08:58:17] [INFO ] Imported 18 HL places and 17 HL transitions for a total of 217 PT places and 525.0 transition bindings in 14 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 17 ms.

Working with output stream class java.io.PrintStream

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-15 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-03-22 08:58:17] [INFO ] Built PT skeleton of HLPN with 18 places and 17 transitions 68 arcs in 4 ms.

[2023-03-22 08:58:17] [INFO ] Skeletonized 15 HLPN properties in 1 ms.

Remains 15 properties that can be checked using skeleton over-approximation.

Reduce places removed 3 places and 0 transitions.

Computed a total of 0 stabilizing places and 0 stable transitions

[2023-03-22 08:58:17] [INFO ] Flatten gal took : 14 ms

[2023-03-22 08:58:17] [INFO ] Flatten gal took : 3 ms

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-09 TRUE TECHNIQUES CPN_APPROX

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-10 TRUE TECHNIQUES CPN_APPROX

Domain [pid(7), pid(7)] of place P_wait breaks symmetries in sort pid

Symmetric sort wr.t. initial and guards and successors and join/free detected :P_bool

Arc [3:1*[$i, 1]] contains constants of sort P_bool

Transition T_setbi_2 : constants on arcs in [[3:1*[$i, 1]]] introduces in P_bool(2) partition with 1 elements that refines current partition to 2 subsets.

[2023-03-22 08:58:17] [INFO ] Unfolded HLPN to a Petri net with 217 places and 420 transitions 1834 arcs in 22 ms.

[2023-03-22 08:58:17] [INFO ] Unfolded 15 HLPN properties in 1 ms.

Deduced a syphon composed of 41 places in 2 ms

Reduce places removed 41 places and 66 transitions.

[2023-03-22 08:58:17] [INFO ] Flatten gal took : 82 ms

[2023-03-22 08:58:17] [INFO ] Flatten gal took : 40 ms

[2023-03-22 08:58:18] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality4670342801291009692.gal : 34 ms

[2023-03-22 08:58:18] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality6354544034804435867.prop : 15 ms

Invoking ITS tools like this :cd /home/mcc/execution;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202303021504/bin/its-reach-linux64' '--gc-threshold' '2000000' '--quiet' '-i' '/tmp/ReachabilityCardinality4670342801291009692.gal' '-t' 'CGAL' '-reachable-file' '/tmp/ReachabilityCardinality6354544034804435867.prop' '--nowitness' '--gen-order' 'FOLLOW'

Incomplete random walk after 10000 steps, including 2 resets, run finished after 677 ms. (steps per millisecond=14 ) properties (out of 13) seen :3

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-14 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-07 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-02 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 131 ms. (steps per millisecond=76 ) properties (out of 10) seen :0

its-reach command run as :

/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202303021504/bin/its-reach-linux64 --gc-threshold 2000000 --quiet ...328

Loading property file /tmp/ReachabilityCardinality6354544034804435867.prop.

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 152 ms. (steps per millisecond=65 ) properties (out of 10) seen :0

SDD proceeding with computation,13 properties remain. new max is 4

SDD size :1 after 5

SDD proceeding with computation,13 properties remain. new max is 8

SDD size :5 after 7

SDD proceeding with computation,13 properties remain. new max is 16

SDD size :7 after 9

SDD proceeding with computation,13 properties remain. new max is 32

SDD size :9 after 64

SDD proceeding with computation,13 properties remain. new max is 64

SDD size :64 after 101

SDD proceeding with computation,13 properties remain. new max is 128

SDD size :101 after 146

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 129 ms. (steps per millisecond=77 ) properties (out of 10) seen :0

SDD proceeding with computation,13 properties remain. new max is 256

SDD size :146 after 632

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 79 ms. (steps per millisecond=126 ) properties (out of 10) seen :0

SDD proceeding with computation,13 properties remain. new max is 512

SDD size :632 after 1727

SDD proceeding with computation,13 properties remain. new max is 1024

SDD size :1727 after 2504

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 131 ms. (steps per millisecond=76 ) properties (out of 10) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 61 ms. (steps per millisecond=163 ) properties (out of 10) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 49 ms. (steps per millisecond=204 ) properties (out of 10) seen :0

Reachability property LamportFastMutEx-COL-6-ReachabilityCardinality-14 is true.

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 59 ms. (steps per millisecond=169 ) properties (out of 10) seen :0

Invariant property LamportFastMutEx-COL-6-ReachabilityCardinality-07 does not hold.

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 85 ms. (steps per millisecond=117 ) properties (out of 10) seen :0

SDD proceeding with computation,11 properties remain. new max is 1024

SDD size :2504 after 6265

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 73 ms. (steps per millisecond=137 ) properties (out of 10) seen :0

Running SMT prover for 10 properties.

[2023-03-22 08:58:19] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2023-03-22 08:58:19] [INFO ] Computed 50 place invariants in 13 ms

SDD proceeding with computation,11 properties remain. new max is 2048

SDD size :6265 after 30817

[2023-03-22 08:58:20] [INFO ] After 582ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:10

[2023-03-22 08:58:20] [INFO ] [Nat]Absence check using 50 positive place invariants in 11 ms returned sat

[2023-03-22 08:58:20] [INFO ] After 107ms SMT Verify possible using state equation in natural domain returned unsat :8 sat :2

[2023-03-22 08:58:20] [INFO ] State equation strengthened by 72 read => feed constraints.

SDD proceeding with computation,11 properties remain. new max is 4096

SDD size :30817 after 41274

[2023-03-22 08:58:20] [INFO ] After 66ms SMT Verify possible using 72 Read/Feed constraints in natural domain returned unsat :8 sat :2

[2023-03-22 08:58:20] [INFO ] Deduced a trap composed of 9 places in 65 ms of which 5 ms to minimize.

[2023-03-22 08:58:20] [INFO ] Deduced a trap composed of 9 places in 40 ms of which 1 ms to minimize.

[2023-03-22 08:58:20] [INFO ] Trap strengthening (SAT) tested/added 3/2 trap constraints in 137 ms

[2023-03-22 08:58:20] [INFO ] After 260ms SMT Verify possible using trap constraints in natural domain returned unsat :8 sat :2

Attempting to minimize the solution found.

Minimization took 50 ms.

[2023-03-22 08:58:20] [INFO ] After 586ms SMT Verify possible using all constraints in natural domain returned unsat :8 sat :2

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-13 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-12 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-08 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-06 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-05 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-04 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-03 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-00 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 10 Parikh solutions to 2 different solutions.

Parikh walk visited 0 properties in 15 ms.

Support contains 36 out of 176 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 176/176 places, 354/354 transitions.

Performed 6 Post agglomeration using F-continuation condition.Transition count delta: 6

Deduced a syphon composed of 6 places in 1 ms

Reduce places removed 6 places and 0 transitions.

Iterating global reduction 0 with 12 rules applied. Total rules applied 12 place count 170 transition count 348

Free-agglomeration rule (complex) applied 6 times.

Iterating global reduction 0 with 6 rules applied. Total rules applied 18 place count 170 transition count 342

Reduce places removed 6 places and 0 transitions.

Iterating post reduction 0 with 6 rules applied. Total rules applied 24 place count 164 transition count 342

Applied a total of 24 rules in 49 ms. Remains 164 /176 variables (removed 12) and now considering 342/354 (removed 12) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 49 ms. Remains : 164/176 places, 342/354 transitions.

Incomplete random walk after 10000 steps, including 2 resets, run finished after 116 ms. (steps per millisecond=86 ) properties (out of 2) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 44 ms. (steps per millisecond=227 ) properties (out of 2) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 28 ms. (steps per millisecond=357 ) properties (out of 2) seen :0

SDD proceeding with computation,11 properties remain. new max is 8192

SDD size :41274 after 77734

Reachability property LamportFastMutEx-COL-6-ReachabilityCardinality-11 is true.

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-11 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL COLLATERAL_PROCESSING

Interrupted probabilistic random walk after 504833 steps, run timeout after 3001 ms. (steps per millisecond=168 ) properties seen :{}

Probabilistic random walk after 504833 steps, saw 190811 distinct states, run finished after 3002 ms. (steps per millisecond=168 ) properties seen :0

Running SMT prover for 2 properties.

[2023-03-22 08:58:24] [INFO ] Flow matrix only has 252 transitions (discarded 90 similar events)

// Phase 1: matrix 252 rows 164 cols

[2023-03-22 08:58:24] [INFO ] Computed 50 place invariants in 10 ms

[2023-03-22 08:58:24] [INFO ] [Real]Absence check using 50 positive place invariants in 8 ms returned sat

[2023-03-22 08:58:24] [INFO ] After 198ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:2

[2023-03-22 08:58:24] [INFO ] [Nat]Absence check using 50 positive place invariants in 7 ms returned sat

[2023-03-22 08:58:24] [INFO ] After 132ms SMT Verify possible using state equation in natural domain returned unsat :0 sat :2

[2023-03-22 08:58:24] [INFO ] State equation strengthened by 72 read => feed constraints.

[2023-03-22 08:58:24] [INFO ] After 62ms SMT Verify possible using 72 Read/Feed constraints in natural domain returned unsat :0 sat :2

[2023-03-22 08:58:24] [INFO ] Deduced a trap composed of 6 places in 86 ms of which 1 ms to minimize.

Invariant property LamportFastMutEx-COL-6-ReachabilityCardinality-01 does not hold.

FORMULA LamportFastMutEx-COL-6-ReachabilityCardinality-01 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL COLLATERAL_PROCESSING

[2023-03-22 08:58:24] [INFO ] Deduced a trap composed of 15 places in 107 ms of which 1 ms to minimize.

[2023-03-22 08:58:25] [INFO ] Deduced a trap composed of 7 places in 152 ms of which 1 ms to minimize.

[2023-03-22 08:58:25] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 390 ms

[2023-03-22 08:58:25] [INFO ] Deduced a trap composed of 8 places in 120 ms of which 1 ms to minimize.

[2023-03-22 08:58:25] [INFO ] Deduced a trap composed of 16 places in 65 ms of which 1 ms to minimize.

[2023-03-22 08:58:25] [INFO ] Trap strengthening (SAT) tested/added 3/2 trap constraints in 211 ms

[2023-03-22 08:58:25] [INFO ] After 718ms SMT Verify possible using trap constraints in natural domain returned unsat :0 sat :2

Attempting to minimize the solution found.

Minimization took 52 ms.

[2023-03-22 08:58:25] [INFO ] After 995ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :2

Parikh walk visited 0 properties in 21 ms.

ITS runner failed with exception null

java.lang.InterruptedException

at java.base/java.lang.Object.wait(Native Method)

at java.base/java.lang.Thread.join(Thread.java:1304)

at java.base/java.lang.Thread.join(Thread.java:1372)

at fr.lip6.move.gal.application.runner.AbstractRunner.join(AbstractRunner.java:27)

at fr.lip6.move.gal.application.runner.its.ITSRunner.join(ITSRunner.java:177)

at fr.lip6.move.gal.application.solver.global.GlobalPropertySolver.verifyWithSDD(GlobalPropertySolver.java:675)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.lambda$2(ReachabilitySolver.java:63)

at java.base/java.lang.Thread.run(Thread.java:833)

All properties solved without resorting to model-checking.

Total runtime 8356 ms.

BK_STOP 1679475508634

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit/bin//../itstools/bin//..//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="LamportFastMutEx-COL-6"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool itstools"

echo " Input is LamportFastMutEx-COL-6, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r229-tall-167856413200374"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/LamportFastMutEx-COL-6.tgz

mv LamportFastMutEx-COL-6 execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;