About the Execution of LoLa+red for HirschbergSinclair-PT-35

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 962.176 | 515739.00 | 553050.00 | 2370.10 | TF?FFT?TTFTFFTTT | normal |

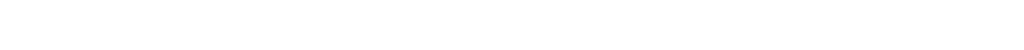

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r199-smll-167840346000476.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lolaxred

Input is HirschbergSinclair-PT-35, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r199-smll-167840346000476

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.1M

-rw-r--r-- 1 mcc users 12K Feb 26 02:09 CTLCardinality.txt

-rw-r--r-- 1 mcc users 87K Feb 26 02:09 CTLCardinality.xml

-rw-r--r-- 1 mcc users 9.0K Feb 26 02:09 CTLFireability.txt

-rw-r--r-- 1 mcc users 62K Feb 26 02:09 CTLFireability.xml

-rw-r--r-- 1 mcc users 6.4K Feb 25 16:15 LTLCardinality.txt

-rw-r--r-- 1 mcc users 32K Feb 25 16:15 LTLCardinality.xml

-rw-r--r-- 1 mcc users 3.3K Feb 25 16:15 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K Feb 25 16:15 LTLFireability.xml

-rw-r--r-- 1 mcc users 20K Feb 26 02:10 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 141K Feb 26 02:10 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 9.8K Feb 26 02:10 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 53K Feb 26 02:10 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.0K Feb 25 16:15 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Feb 25 16:15 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 3 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 544K Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-00

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-01

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-02

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-03

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-04

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-05

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-06

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-07

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-08

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-09

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-10

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-11

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-12

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-13

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-14

FORMULA_NAME HirschbergSinclair-PT-35-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1678549480987

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lolaxred

BK_EXAMINATION=LTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=HirschbergSinclair-PT-35

Applying reductions before tool lola

Invoking reducer

Running Version 202303021504

[2023-03-11 15:44:43] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -timeout, 360, -rebuildPNML]

[2023-03-11 15:44:44] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-11 15:44:44] [INFO ] Load time of PNML (sax parser for PT used): 224 ms

[2023-03-11 15:44:44] [INFO ] Transformed 998 places.

[2023-03-11 15:44:44] [INFO ] Transformed 922 transitions.

[2023-03-11 15:44:44] [INFO ] Parsed PT model containing 998 places and 922 transitions and 2806 arcs in 408 ms.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 16 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 4 formulas.

FORMULA HirschbergSinclair-PT-35-LTLFireability-03 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA HirschbergSinclair-PT-35-LTLFireability-07 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA HirschbergSinclair-PT-35-LTLFireability-10 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA HirschbergSinclair-PT-35-LTLFireability-13 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 42 out of 998 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 998/998 places, 922/922 transitions.

Reduce places removed 35 places and 0 transitions.

Iterating post reduction 0 with 35 rules applied. Total rules applied 35 place count 963 transition count 922

Discarding 31 places :

Symmetric choice reduction at 1 with 31 rule applications. Total rules 66 place count 932 transition count 891

Iterating global reduction 1 with 31 rules applied. Total rules applied 97 place count 932 transition count 891

Discarding 31 places :

Symmetric choice reduction at 1 with 31 rule applications. Total rules 128 place count 901 transition count 860

Iterating global reduction 1 with 31 rules applied. Total rules applied 159 place count 901 transition count 860

Applied a total of 159 rules in 583 ms. Remains 901 /998 variables (removed 97) and now considering 860/922 (removed 62) transitions.

// Phase 1: matrix 860 rows 901 cols

[2023-03-11 15:44:45] [INFO ] Computed 41 place invariants in 40 ms

[2023-03-11 15:44:46] [INFO ] SMT solver returned unknown. Retrying;

[2023-03-11 15:44:46] [INFO ] Implicit Places using invariants in 968 ms returned []

[2023-03-11 15:44:46] [INFO ] Invariant cache hit.

[2023-03-11 15:44:49] [INFO ] Implicit Places using invariants and state equation in 2900 ms returned []

Implicit Place search using SMT with State Equation took 3940 ms to find 0 implicit places.

[2023-03-11 15:44:49] [INFO ] Invariant cache hit.

[2023-03-11 15:44:50] [INFO ] Dead Transitions using invariants and state equation in 1260 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 901/998 places, 860/922 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5786 ms. Remains : 901/998 places, 860/922 transitions.

Support contains 42 out of 901 places after structural reductions.

[2023-03-11 15:44:51] [INFO ] Flatten gal took : 175 ms

[2023-03-11 15:44:51] [INFO ] Flatten gal took : 129 ms

[2023-03-11 15:44:51] [INFO ] Input system was already deterministic with 860 transitions.

Support contains 41 out of 901 places (down from 42) after GAL structural reductions.

Finished random walk after 898 steps, including 0 resets, run visited all 27 properties in 182 ms. (steps per millisecond=4 )

Computed a total of 901 stabilizing places and 860 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 901 transition count 860

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X((G(p1)||p0))))'

Support contains 5 out of 901 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 4 place count 897 transition count 856

Iterating global reduction 0 with 4 rules applied. Total rules applied 8 place count 897 transition count 856

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 12 place count 893 transition count 852

Iterating global reduction 0 with 4 rules applied. Total rules applied 16 place count 893 transition count 852

Applied a total of 16 rules in 166 ms. Remains 893 /901 variables (removed 8) and now considering 852/860 (removed 8) transitions.

// Phase 1: matrix 852 rows 893 cols

[2023-03-11 15:44:52] [INFO ] Computed 41 place invariants in 11 ms

[2023-03-11 15:44:53] [INFO ] Implicit Places using invariants in 708 ms returned []

[2023-03-11 15:44:53] [INFO ] Invariant cache hit.

[2023-03-11 15:44:56] [INFO ] Implicit Places using invariants and state equation in 3013 ms returned []

Implicit Place search using SMT with State Equation took 3732 ms to find 0 implicit places.

[2023-03-11 15:44:56] [INFO ] Invariant cache hit.

[2023-03-11 15:44:57] [INFO ] Dead Transitions using invariants and state equation in 1106 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 893/901 places, 852/860 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5009 ms. Remains : 893/901 places, 852/860 transitions.

Stuttering acceptance computed with spot in 337 ms :[true, (NOT p1), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-00 automaton TGBA Formula[mat=[[{ cond=true, acceptance={0} source=0 dest: 0}], [{ cond=(NOT p1), acceptance={} source=1 dest: 0}, { cond=p1, acceptance={} source=1 dest: 1}], [{ cond=(AND (NOT p0) (NOT p1)), acceptance={} source=2 dest: 0}, { cond=(AND (NOT p0) p1), acceptance={} source=2 dest: 1}], [{ cond=true, acceptance={} source=3 dest: 2}], [{ cond=true, acceptance={} source=4 dest: 3}]], initial=4, aps=[p1:(OR (GEQ s727 1) (AND (GEQ s3 1) (GEQ s259 1))), p0:(OR (LT s37 1) (LT s873 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, terminal, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null][false, false, false, false, false]]

Product exploration explored 100000 steps with 33333 reset in 932 ms.

Product exploration explored 100000 steps with 33333 reset in 799 ms.

Computed a total of 893 stabilizing places and 852 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 893 transition count 852

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND (NOT p1) p0), (X (X (NOT (AND (NOT p0) (NOT p1))))), (X (X (NOT (AND (NOT p0) p1)))), (F (G (NOT p1))), (F (G p0))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge :(X (X (NOT (AND (NOT p0) p1))))

Knowledge based reduction with 5 factoid took 147 ms. Reduced automaton from 5 states, 7 edges and 2 AP (stutter sensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA HirschbergSinclair-PT-35-LTLFireability-00 TRUE TECHNIQUES KNOWLEDGE

Treatment of property HirschbergSinclair-PT-35-LTLFireability-00 finished in 7697 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(G((p0&&X((p1&&G(p2))))))))'

Support contains 4 out of 901 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Discarding 3 places :

Symmetric choice reduction at 0 with 3 rule applications. Total rules 3 place count 898 transition count 857

Iterating global reduction 0 with 3 rules applied. Total rules applied 6 place count 898 transition count 857

Discarding 3 places :

Symmetric choice reduction at 0 with 3 rule applications. Total rules 9 place count 895 transition count 854

Iterating global reduction 0 with 3 rules applied. Total rules applied 12 place count 895 transition count 854

Applied a total of 12 rules in 128 ms. Remains 895 /901 variables (removed 6) and now considering 854/860 (removed 6) transitions.

// Phase 1: matrix 854 rows 895 cols

[2023-03-11 15:45:00] [INFO ] Computed 41 place invariants in 12 ms

[2023-03-11 15:45:00] [INFO ] Implicit Places using invariants in 634 ms returned []

[2023-03-11 15:45:00] [INFO ] Invariant cache hit.

[2023-03-11 15:45:04] [INFO ] Implicit Places using invariants and state equation in 4238 ms returned []

Implicit Place search using SMT with State Equation took 4880 ms to find 0 implicit places.

[2023-03-11 15:45:04] [INFO ] Invariant cache hit.

[2023-03-11 15:45:06] [INFO ] Dead Transitions using invariants and state equation in 1133 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 895/901 places, 854/860 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 6144 ms. Remains : 895/901 places, 854/860 transitions.

Stuttering acceptance computed with spot in 266 ms :[true, (OR (NOT p0) (NOT p1) (NOT p2)), (OR (NOT p0) (NOT p1) (NOT p2)), (OR (NOT p0) (NOT p1) (NOT p2)), (OR (NOT p0) (NOT p1) (NOT p2))]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-01 automaton TGBA Formula[mat=[[{ cond=true, acceptance={0} source=0 dest: 0}], [{ cond=(NOT p0), acceptance={} source=1 dest: 0}, { cond=p0, acceptance={} source=1 dest: 4}], [{ cond=true, acceptance={} source=2 dest: 3}], [{ cond=true, acceptance={} source=3 dest: 1}], [{ cond=(OR (NOT p0) (NOT p1) (NOT p2)), acceptance={} source=4 dest: 0}, { cond=(AND p0 p1 p2), acceptance={} source=4 dest: 4}]], initial=2, aps=[p0:(GEQ s97 1), p1:(OR (LT s61 1) (LT s340 1)), p2:(GEQ s252 1)], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, complete, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, terminal, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null][false, false, false, false, false]]

Entered a terminal (fully accepting) state of product in 2 steps with 0 reset in 1 ms.

FORMULA HirschbergSinclair-PT-35-LTLFireability-01 FALSE TECHNIQUES STUTTER_TEST

Treatment of property HirschbergSinclair-PT-35-LTLFireability-01 finished in 6454 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(F(p0)))'

Support contains 2 out of 901 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Reduce places removed 34 places and 34 transitions.

Drop transitions removed 378 transitions

Trivial Post-agglo rules discarded 378 transitions

Performed 378 trivial Post agglomeration. Transition count delta: 378

Iterating post reduction 0 with 378 rules applied. Total rules applied 378 place count 867 transition count 448

Reduce places removed 378 places and 0 transitions.

Iterating post reduction 1 with 378 rules applied. Total rules applied 756 place count 489 transition count 448

Discarding 4 places :

Symmetric choice reduction at 2 with 4 rule applications. Total rules 760 place count 485 transition count 444

Iterating global reduction 2 with 4 rules applied. Total rules applied 764 place count 485 transition count 444

Applied a total of 764 rules in 133 ms. Remains 485 /901 variables (removed 416) and now considering 444/860 (removed 416) transitions.

// Phase 1: matrix 444 rows 485 cols

[2023-03-11 15:45:06] [INFO ] Computed 41 place invariants in 4 ms

[2023-03-11 15:45:07] [INFO ] Implicit Places using invariants in 582 ms returned []

[2023-03-11 15:45:07] [INFO ] Invariant cache hit.

[2023-03-11 15:45:09] [INFO ] Implicit Places using invariants and state equation in 2137 ms returned []

Implicit Place search using SMT with State Equation took 2723 ms to find 0 implicit places.

[2023-03-11 15:45:09] [INFO ] Redundant transitions in 42 ms returned []

[2023-03-11 15:45:09] [INFO ] Invariant cache hit.

[2023-03-11 15:45:10] [INFO ] Dead Transitions using invariants and state equation in 891 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 485/901 places, 444/860 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 3801 ms. Remains : 485/901 places, 444/860 transitions.

Stuttering acceptance computed with spot in 104 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-02 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={} source=0 dest: 1}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p0:(AND (GEQ s32 1) (GEQ s124 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-invariant, very-weak, weak, inherently-weak], stateDesc=[null, null][true, true]]

Product exploration explored 100000 steps with 794 reset in 928 ms.

Product exploration explored 100000 steps with 794 reset in 606 ms.

Computed a total of 485 stabilizing places and 444 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 485 transition count 444

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 167 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 74 ms :[(NOT p0), (NOT p0)]

Finished random walk after 142 steps, including 0 resets, run visited all 1 properties in 6 ms. (steps per millisecond=23 )

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p0)]

Knowledge based reduction with 4 factoid took 173 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 80 ms :[(NOT p0), (NOT p0)]

Stuttering acceptance computed with spot in 80 ms :[(NOT p0), (NOT p0)]

[2023-03-11 15:45:12] [INFO ] Invariant cache hit.

[2023-03-11 15:45:13] [INFO ] [Real]Absence check using 0 positive and 41 generalized place invariants in 304 ms returned sat

[2023-03-11 15:45:13] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2023-03-11 15:45:16] [INFO ] [Real]Absence check using state equation in 3483 ms returned sat

[2023-03-11 15:45:17] [INFO ] Computed and/alt/rep : 364/372/364 causal constraints (skipped 14 transitions) in 54 ms.

[2023-03-11 15:45:18] [INFO ] Added : 25 causal constraints over 5 iterations in 1109 ms. Result :sat

Could not prove EG (NOT p0)

Support contains 2 out of 485 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 485/485 places, 444/444 transitions.

Applied a total of 0 rules in 48 ms. Remains 485 /485 variables (removed 0) and now considering 444/444 (removed 0) transitions.

[2023-03-11 15:45:18] [INFO ] Invariant cache hit.

[2023-03-11 15:45:19] [INFO ] Implicit Places using invariants in 923 ms returned []

[2023-03-11 15:45:19] [INFO ] Invariant cache hit.

[2023-03-11 15:45:21] [INFO ] Implicit Places using invariants and state equation in 2556 ms returned []

Implicit Place search using SMT with State Equation took 3488 ms to find 0 implicit places.

[2023-03-11 15:45:21] [INFO ] Redundant transitions in 15 ms returned []

[2023-03-11 15:45:21] [INFO ] Invariant cache hit.

[2023-03-11 15:45:22] [INFO ] Dead Transitions using invariants and state equation in 655 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 4217 ms. Remains : 485/485 places, 444/444 transitions.

Computed a total of 485 stabilizing places and 444 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 485 transition count 444

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 186 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 103 ms :[(NOT p0), (NOT p0)]

Finished random walk after 145 steps, including 0 resets, run visited all 1 properties in 7 ms. (steps per millisecond=20 )

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p0)]

Knowledge based reduction with 4 factoid took 256 ms. Reduced automaton from 2 states, 3 edges and 1 AP (stutter insensitive) to 2 states, 3 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 93 ms :[(NOT p0), (NOT p0)]

Stuttering acceptance computed with spot in 105 ms :[(NOT p0), (NOT p0)]

[2023-03-11 15:45:23] [INFO ] Invariant cache hit.

[2023-03-11 15:45:24] [INFO ] [Real]Absence check using 0 positive and 41 generalized place invariants in 303 ms returned sat

[2023-03-11 15:45:24] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2023-03-11 15:45:27] [INFO ] [Real]Absence check using state equation in 3498 ms returned sat

[2023-03-11 15:45:28] [INFO ] Computed and/alt/rep : 364/372/364 causal constraints (skipped 14 transitions) in 45 ms.

[2023-03-11 15:45:28] [INFO ] Added : 25 causal constraints over 5 iterations in 834 ms. Result :sat

Could not prove EG (NOT p0)

Stuttering acceptance computed with spot in 130 ms :[(NOT p0), (NOT p0)]

Product exploration explored 100000 steps with 794 reset in 704 ms.

Product exploration explored 100000 steps with 795 reset in 544 ms.

Support contains 2 out of 485 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 485/485 places, 444/444 transitions.

Applied a total of 0 rules in 30 ms. Remains 485 /485 variables (removed 0) and now considering 444/444 (removed 0) transitions.

[2023-03-11 15:45:30] [INFO ] Invariant cache hit.

[2023-03-11 15:45:31] [INFO ] Implicit Places using invariants in 722 ms returned []

[2023-03-11 15:45:31] [INFO ] Invariant cache hit.

[2023-03-11 15:45:33] [INFO ] Implicit Places using invariants and state equation in 2188 ms returned []

Implicit Place search using SMT with State Equation took 2914 ms to find 0 implicit places.

[2023-03-11 15:45:33] [INFO ] Redundant transitions in 6 ms returned []

[2023-03-11 15:45:33] [INFO ] Invariant cache hit.

[2023-03-11 15:45:33] [INFO ] Dead Transitions using invariants and state equation in 658 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 3620 ms. Remains : 485/485 places, 444/444 transitions.

Treatment of property HirschbergSinclair-PT-35-LTLFireability-02 finished in 27815 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(G(F(p0)))'

Support contains 1 out of 901 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Reduce places removed 35 places and 35 transitions.

Drop transitions removed 391 transitions

Trivial Post-agglo rules discarded 391 transitions

Performed 391 trivial Post agglomeration. Transition count delta: 391

Iterating post reduction 0 with 391 rules applied. Total rules applied 391 place count 866 transition count 434

Reduce places removed 391 places and 0 transitions.

Iterating post reduction 1 with 391 rules applied. Total rules applied 782 place count 475 transition count 434

Discarding 4 places :

Symmetric choice reduction at 2 with 4 rule applications. Total rules 786 place count 471 transition count 430

Iterating global reduction 2 with 4 rules applied. Total rules applied 790 place count 471 transition count 430

Applied a total of 790 rules in 97 ms. Remains 471 /901 variables (removed 430) and now considering 430/860 (removed 430) transitions.

// Phase 1: matrix 430 rows 471 cols

[2023-03-11 15:45:34] [INFO ] Computed 41 place invariants in 3 ms

[2023-03-11 15:45:34] [INFO ] Implicit Places using invariants in 528 ms returned []

[2023-03-11 15:45:34] [INFO ] Invariant cache hit.

[2023-03-11 15:45:36] [INFO ] Implicit Places using invariants and state equation in 2227 ms returned []

Implicit Place search using SMT with State Equation took 2761 ms to find 0 implicit places.

[2023-03-11 15:45:36] [INFO ] Redundant transitions in 2 ms returned []

[2023-03-11 15:45:36] [INFO ] Invariant cache hit.

[2023-03-11 15:45:37] [INFO ] Dead Transitions using invariants and state equation in 794 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 471/901 places, 430/860 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 3662 ms. Remains : 471/901 places, 430/860 transitions.

Stuttering acceptance computed with spot in 90 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-04 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 0}, { cond=(NOT p0), acceptance={} source=0 dest: 1}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p0:(GEQ s54 1)], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, no-univ-branch, stutter-invariant, very-weak, weak, inherently-weak], stateDesc=[null, null][true, true]]

Stuttering criterion allowed to conclude after 11200 steps with 252 reset in 106 ms.

FORMULA HirschbergSinclair-PT-35-LTLFireability-04 FALSE TECHNIQUES STUTTER_TEST

Treatment of property HirschbergSinclair-PT-35-LTLFireability-04 finished in 3883 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X((X((F(p0)&&p1))||(X((F(p3)&&p2)) U p4))))'

Support contains 6 out of 901 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 4 place count 897 transition count 856

Iterating global reduction 0 with 4 rules applied. Total rules applied 8 place count 897 transition count 856

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 12 place count 893 transition count 852

Iterating global reduction 0 with 4 rules applied. Total rules applied 16 place count 893 transition count 852

Applied a total of 16 rules in 225 ms. Remains 893 /901 variables (removed 8) and now considering 852/860 (removed 8) transitions.

// Phase 1: matrix 852 rows 893 cols

[2023-03-11 15:45:38] [INFO ] Computed 41 place invariants in 10 ms

[2023-03-11 15:45:39] [INFO ] Implicit Places using invariants in 1119 ms returned []

[2023-03-11 15:45:39] [INFO ] Invariant cache hit.

[2023-03-11 15:45:43] [INFO ] Implicit Places using invariants and state equation in 3789 ms returned []

Implicit Place search using SMT with State Equation took 4910 ms to find 0 implicit places.

[2023-03-11 15:45:43] [INFO ] Invariant cache hit.

[2023-03-11 15:45:44] [INFO ] Dead Transitions using invariants and state equation in 1241 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 893/901 places, 852/860 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 6377 ms. Remains : 893/901 places, 852/860 transitions.

Stuttering acceptance computed with spot in 505 ms :[(OR (AND (NOT p1) (NOT p4)) (AND (NOT p0) (NOT p4))), (NOT p3), (OR (AND (NOT p0) (NOT p2)) (AND (NOT p0) (NOT p3)) (AND (NOT p1) (NOT p2)) (AND (NOT p1) (NOT p3)) (AND (NOT p0) (NOT p4)) (AND (NOT p1) (NOT p4))), (AND (NOT p3) (NOT p0)), true, (OR (AND (NOT p1) (NOT p4)) (AND (NOT p0) (NOT p4))), (NOT p0), (OR (NOT p3) (NOT p2) (NOT p4)), (OR (AND (NOT p0) (NOT p3)) (AND (NOT p0) (NOT p2)) (AND (NOT p0) (NOT p4)))]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-05 automaton TGBA Formula[mat=[[{ cond=(NOT p4), acceptance={} source=0 dest: 2}], [{ cond=(NOT p3), acceptance={0} source=1 dest: 1}], [{ cond=(AND p4 (NOT p1) p2 (NOT p3)), acceptance={} source=2 dest: 1}, { cond=(AND p4 p1 (NOT p0) p2 (NOT p3)), acceptance={} source=2 dest: 3}, { cond=(AND (NOT p1) (NOT p2)), acceptance={} source=2 dest: 4}, { cond=(AND p1 (NOT p0) (NOT p2)), acceptance={} source=2 dest: 6}, { cond=(AND (NOT p4) (NOT p1) p2), acceptance={} source=2 dest: 7}, { cond=(AND (NOT p4) p1 (NOT p0) p2), acceptance={} source=2 dest: 8}], [{ cond=(AND (NOT p0) (NOT p3)), acceptance={0} source=3 dest: 3}], [{ cond=true, acceptance={0} source=4 dest: 4}], [{ cond=true, acceptance={} source=5 dest: 0}], [{ cond=(NOT p0), acceptance={0} source=6 dest: 6}], [{ cond=(AND p4 p2 (NOT p3)), acceptance={0} source=7 dest: 1}, { cond=(NOT p2), acceptance={0} source=7 dest: 4}, { cond=(AND (NOT p4) p2), acceptance={0} source=7 dest: 7}], [{ cond=(AND p4 (NOT p0) p2 (NOT p3)), acceptance={0} source=8 dest: 3}, { cond=(AND (NOT p0) (NOT p2)), acceptance={0} source=8 dest: 6}, { cond=(AND (NOT p4) (NOT p0) p2), acceptance={0} source=8 dest: 8}]], initial=5, aps=[p4:(LT s353 1), p3:(GEQ s175 1), p1:(GEQ s387 1), p2:(AND (GEQ s13 1) (GEQ s532 1)), p0:(AND (GEQ s13 1) (GEQ s98 1))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null, null, null, null, null, null, null, null][false, false, false, false, false, false, false, false, false]]

Product exploration explored 100000 steps with 50000 reset in 982 ms.

Product exploration explored 100000 steps with 50000 reset in 793 ms.

Computed a total of 893 stabilizing places and 852 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 893 transition count 852

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(AND p4 (NOT p3) (NOT p1) (NOT p2) (NOT p0)), (X p4), (X (X (AND (NOT p1) (NOT p2)))), (X (X (NOT (AND (NOT p4) p1 (NOT p0) p2)))), (X (X (NOT (AND p4 p1 (NOT p0) p2 (NOT p3))))), (X (X (NOT (AND p1 (NOT p0) (NOT p2))))), (X (X (NOT (AND (NOT p4) (NOT p1) p2)))), (X (X (NOT (AND p4 (NOT p1) p2 (NOT p3))))), (F (G p4)), (F (G (NOT p3))), (F (G (NOT p1))), (F (G (NOT p2))), (F (G (NOT p0)))]

False Knowledge obtained : []

Property proved to be true thanks to knowledge :(X p4)

Knowledge based reduction with 13 factoid took 277 ms. Reduced automaton from 9 states, 18 edges and 5 AP (stutter sensitive) to 1 states, 0 edges and 0 AP (stutter insensitive).

FORMULA HirschbergSinclair-PT-35-LTLFireability-05 TRUE TECHNIQUES KNOWLEDGE

Treatment of property HirschbergSinclair-PT-35-LTLFireability-05 finished in 9387 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(F(p0)))'

Support contains 3 out of 901 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 4 place count 897 transition count 856

Iterating global reduction 0 with 4 rules applied. Total rules applied 8 place count 897 transition count 856

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 12 place count 893 transition count 852

Iterating global reduction 0 with 4 rules applied. Total rules applied 16 place count 893 transition count 852

Applied a total of 16 rules in 207 ms. Remains 893 /901 variables (removed 8) and now considering 852/860 (removed 8) transitions.

[2023-03-11 15:45:47] [INFO ] Invariant cache hit.

[2023-03-11 15:45:48] [INFO ] Implicit Places using invariants in 780 ms returned []

[2023-03-11 15:45:48] [INFO ] Invariant cache hit.

[2023-03-11 15:45:51] [INFO ] Implicit Places using invariants and state equation in 3219 ms returned []

Implicit Place search using SMT with State Equation took 4006 ms to find 0 implicit places.

[2023-03-11 15:45:51] [INFO ] Invariant cache hit.

[2023-03-11 15:45:53] [INFO ] Dead Transitions using invariants and state equation in 1414 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 893/901 places, 852/860 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5628 ms. Remains : 893/901 places, 852/860 transitions.

Stuttering acceptance computed with spot in 71 ms :[(NOT p0), (NOT p0)]

Running random walk in product with property : HirschbergSinclair-PT-35-LTLFireability-06 automaton TGBA Formula[mat=[[{ cond=true, acceptance={} source=0 dest: 1}], [{ cond=(NOT p0), acceptance={0} source=1 dest: 1}]], initial=0, aps=[p0:(OR (GEQ s684 1) (AND (GEQ s59 1) (GEQ s286 1)))], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive, very-weak, weak, inherently-weak], stateDesc=[null, null][false, false]]

Product exploration explored 100000 steps with 296 reset in 453 ms.

Product exploration explored 100000 steps with 296 reset in 556 ms.

Computed a total of 893 stabilizing places and 852 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 893 transition count 852

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 180 ms. Reduced automaton from 2 states, 2 edges and 1 AP (stutter sensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 49 ms :[(NOT p0)]

Finished random walk after 334 steps, including 0 resets, run visited all 1 properties in 7 ms. (steps per millisecond=47 )

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p0)]

Knowledge based reduction with 4 factoid took 241 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 52 ms :[(NOT p0)]

Stuttering acceptance computed with spot in 35 ms :[(NOT p0)]

[2023-03-11 15:45:55] [INFO ] Invariant cache hit.

[2023-03-11 15:45:56] [INFO ] [Real]Absence check using 0 positive and 41 generalized place invariants in 171 ms returned sat

[2023-03-11 15:45:56] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2023-03-11 15:46:10] [INFO ] [Real]Absence check using state equation in 13780 ms returned unknown

Could not prove EG (NOT p0)

Support contains 3 out of 893 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 893/893 places, 852/852 transitions.

Reduce places removed 34 places and 34 transitions.

Drop transitions removed 374 transitions

Trivial Post-agglo rules discarded 374 transitions

Performed 374 trivial Post agglomeration. Transition count delta: 374

Iterating post reduction 0 with 374 rules applied. Total rules applied 374 place count 859 transition count 444

Reduce places removed 374 places and 0 transitions.

Iterating post reduction 1 with 374 rules applied. Total rules applied 748 place count 485 transition count 444

Applied a total of 748 rules in 65 ms. Remains 485 /893 variables (removed 408) and now considering 444/852 (removed 408) transitions.

// Phase 1: matrix 444 rows 485 cols

[2023-03-11 15:46:10] [INFO ] Computed 41 place invariants in 5 ms

[2023-03-11 15:46:10] [INFO ] Implicit Places using invariants in 831 ms returned []

[2023-03-11 15:46:10] [INFO ] Invariant cache hit.

[2023-03-11 15:46:13] [INFO ] Implicit Places using invariants and state equation in 2118 ms returned []

Implicit Place search using SMT with State Equation took 2959 ms to find 0 implicit places.

[2023-03-11 15:46:13] [INFO ] Redundant transitions in 2 ms returned []

[2023-03-11 15:46:13] [INFO ] Invariant cache hit.

[2023-03-11 15:46:13] [INFO ] Dead Transitions using invariants and state equation in 639 ms found 0 transitions.

Starting structural reductions in SI_LTL mode, iteration 1 : 485/893 places, 444/852 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 3672 ms. Remains : 485/893 places, 444/852 transitions.

Computed a total of 485 stabilizing places and 444 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 485 transition count 444

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 205 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 51 ms :[(NOT p0)]

Finished random walk after 173 steps, including 0 resets, run visited all 1 properties in 2 ms. (steps per millisecond=86 )

Knowledge obtained : [(NOT p0), (X (NOT p0)), (X (X (NOT p0))), (F (G (NOT p0)))]

False Knowledge obtained : [(F p0)]

Knowledge based reduction with 4 factoid took 230 ms. Reduced automaton from 1 states, 1 edges and 1 AP (stutter insensitive) to 1 states, 1 edges and 1 AP (stutter insensitive).

Stuttering acceptance computed with spot in 49 ms :[(NOT p0)]

Stuttering acceptance computed with spot in 49 ms :[(NOT p0)]

[2023-03-11 15:46:14] [INFO ] Invariant cache hit.

[2023-03-11 15:46:15] [INFO ] [Real]Absence check using 0 positive and 41 generalized place invariants in 209 ms returned sat

[2023-03-11 15:46:15] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2023-03-11 15:46:25] [INFO ] [Real]Absence check using state equation in 9917 ms returned sat

[2023-03-11 15:46:25] [INFO ] Solution in real domain found non-integer solution.

[2023-03-11 15:46:26] [INFO ] [Nat]Absence check using 0 positive and 41 generalized place invariants in 244 ms returned sat

[2023-03-11 15:46:26] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2023-03-11 15:46:29] [INFO ] [Nat]Absence check using state equation in 3160 ms returned sat

[2023-03-11 15:46:29] [INFO ] Computed and/alt/rep : 365/373/365 causal constraints (skipped 13 transitions) in 33 ms.

[2023-03-11 15:46:33] [INFO ] Added : 242 causal constraints over 49 iterations in 4487 ms. Result :sat

Could not prove EG (NOT p0)

Stuttering acceptance computed with spot in 135 ms :[(NOT p0)]

Product exploration explored 100000 steps with 624 reset in 683 ms.

Product exploration explored 100000 steps with 623 reset in 713 ms.

Support contains 3 out of 485 places. Attempting structural reductions.

Starting structural reductions in SI_LTL mode, iteration 0 : 485/485 places, 444/444 transitions.

Applied a total of 0 rules in 26 ms. Remains 485 /485 variables (removed 0) and now considering 444/444 (removed 0) transitions.

[2023-03-11 15:46:35] [INFO ] Invariant cache hit.

[2023-03-11 15:46:36] [INFO ] Implicit Places using invariants in 727 ms returned []

[2023-03-11 15:46:36] [INFO ] Invariant cache hit.

[2023-03-11 15:46:39] [INFO ] Implicit Places using invariants and state equation in 2803 ms returned []

Implicit Place search using SMT with State Equation took 3533 ms to find 0 implicit places.

[2023-03-11 15:46:39] [INFO ] Redundant transitions in 2 ms returned []

[2023-03-11 15:46:39] [INFO ] Invariant cache hit.

[2023-03-11 15:46:39] [INFO ] Dead Transitions using invariants and state equation in 619 ms found 0 transitions.

Finished structural reductions in SI_LTL mode , in 1 iterations and 4187 ms. Remains : 485/485 places, 444/444 transitions.

Treatment of property HirschbergSinclair-PT-35-LTLFireability-06 finished in 52351 ms.

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(F(((!p0&&X(F((F(p1)&&G(!p2)))))||G((F(p1)&&F(G(!p2)))))))'

Support contains 5 out of 901 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 901/901 places, 860/860 transitions.

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 4 place count 897 transition count 856

Iterating global reduction 0 with 4 rules applied. Total rules applied 8 place count 897 transition count 856

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 12 place count 893 transition count 852

Iterating global reduction 0 with 4 rules applied. Total rules applied 16 place count 893 transition count 852

Applied a total of 16 rules in 155 ms. Remains 893 /901 variables (removed 8) and now considering 852/860 (removed 8) transitions.

// Phase 1: matrix 852 rows 893 cols

[2023-03-11 15:46:39] [INFO ] Computed 41 place invariants in 13 ms

[2023-03-11 15:46:41] [INFO ] Implicit Places using invariants in 1085 ms returned []

[2023-03-11 15:46:41] [INFO ] Invariant cache hit.

[2023-03-11 15:46:44] [INFO ] Implicit Places using invariants and state equation in 3305 ms returned []

Implicit Place search using SMT with State Equation took 4392 ms to find 0 implicit places.

[2023-03-11 15:46:44] [INFO ] Invariant cache hit.

[2023-03-11 15:46:45] [INFO ] Dead Transitions using invariants and state equation in 1072 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 893/901 places, 852/860 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5621 ms. Remains : 893/901 places, 852/860 transitions.

Stuttering acceptance computed with spot in 257 ms :[(OR (NOT p1) p2), (NOT p1), p2, (OR (NOT p1) p2), p2]