About the Execution of 2022-gold for FamilyReunion-COL-L00020M0002C001P001G001

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 2647.228 | 3592744.00 | 8929974.00 | 5522.00 | FF??TTFTT??F?TFF | normal |

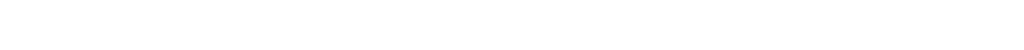

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r190-tall-167838875400232.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool gold2022

Input is FamilyReunion-COL-L00020M0002C001P001G001, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r190-tall-167838875400232

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 560K

-rw-r--r-- 1 mcc users 7.4K Feb 26 11:40 CTLCardinality.txt

-rw-r--r-- 1 mcc users 78K Feb 26 11:40 CTLCardinality.xml

-rw-r--r-- 1 mcc users 7.5K Feb 26 11:36 CTLFireability.txt

-rw-r--r-- 1 mcc users 55K Feb 26 11:36 CTLFireability.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 equiv_pt

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 7.0K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 24 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 3.6K Feb 25 16:05 LTLCardinality.txt

-rw-r--r-- 1 mcc users 24K Feb 25 16:05 LTLCardinality.xml

-rw-r--r-- 1 mcc users 3.3K Feb 25 16:05 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K Feb 25 16:05 LTLFireability.xml

-rw-r--r-- 1 mcc users 135K Mar 5 18:22 model.pnml

-rw-r--r-- 1 mcc users 8.9K Feb 26 11:48 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 90K Feb 26 11:48 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 11K Feb 26 11:45 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 65K Feb 26 11:45 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.0K Feb 25 16:05 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.0K Feb 25 16:05 UpperBounds.xml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-00

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-01

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-02

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-03

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-04

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-05

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-06

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-07

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-08

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-09

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-10

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-11

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-12

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-13

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-14

FORMULA_NAME FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1678619058422

gold2022

Got BK_BIN_PATH=/home/mcc/BenchKit/bin/

---> gold2022 --- TAPAAL v5

Setting MODEL_PATH=.

Setting VERIFYPN=/home/mcc/BenchKit/bin/verifypn

Got BK_TIME_CONFINEMENT=3600

Setting TEMPDIR=/home/mcc/BenchKit/bin/tmp

Got BK_MEMORY_CONFINEMENT=16384

Limiting to 16265216 kB

Total timeout: 3590

Time left: 3590

*************************************

* TAPAAL verifying LTLFireability *

*************************************

TEMPDIR=/home/mcc/BenchKit/bin/tmp

QF=/home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2

MF=/home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m

Time left: 3590

---------------------------------------------------

Step -1: Stripping Colors

---------------------------------------------------

Verifying stripped models (16 in total)

/home/mcc/BenchKit/bin/verifypn -n -c -q 718 -ltl -l 29 -d 299 -z 4 -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./LTLFireability.xml

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-15

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-14

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-13

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-12

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-11

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-10

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-09

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-08

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-07

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-06

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-05

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-04

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-03

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-02

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-01

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-00

WARNING: Could not run CPN over-approximation on any queries, terminating.

Time left: 3590

---------------------------------------------------

Step 0: Parallel Simplification

---------------------------------------------------

Doing parallel simplification (16 in total)

Total simplification timout is 718 -- reduction timeout is 299

timeout 1017 /home/mcc/BenchKit/bin/verifypn -n -ltl -q 718 -l 29 -d 299 -z 4 -s OverApprox --binary-query-io 2 --write-simplified /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --write-reduced /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./LTLFireability.xml

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-04 TRUE TECHNIQUES COLLATERAL_PROCESSING STRUCTURAL_REDUCTION QUERY_REDUCTION SAT_SMT LP_APPROX UNFOLDING_TO_PT

Query index 4 was solved

Query is satisfied.

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-05 TRUE TECHNIQUES COLLATERAL_PROCESSING STRUCTURAL_REDUCTION QUERY_REDUCTION SAT_SMT LP_APPROX UNFOLDING_TO_PT

Query index 5 was solved

Query is satisfied.

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-13 TRUE TECHNIQUES COLLATERAL_PROCESSING STRUCTURAL_REDUCTION QUERY_REDUCTION SAT_SMT LP_APPROX UNFOLDING_TO_PT

Query index 13 was solved

Query is satisfied.

Solution found by parallel simplification (step 0)

Solution found by parallel simplification (step 0)

Solution found by parallel simplification (step 0)

Time left: 3586

---------------------------------------------------

Step 1: Parallel processing

---------------------------------------------------

Doing parallel verification of individual queries (13 in total)

Each query is verified by 4 parallel strategies for 299 seconds

------------------- QUERY 1 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.123441 on verification

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-00 FALSE TECHNIQUES EXPLICIT TARJAN WEAK_SKIP STUBBORN AUT_STUB HEURISTIC LOGFIRECOUNT_HEUR(5000) OPTIM-1

Query index 0 was solved

Query is NOT satisfied.

Spent 0.117999 on verification

@@@0.22,154896@@@

@@@0.22,154868@@@

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-00 FALSE TECHNIQUES EXPLICIT TARJAN WEAK_SKIP OPTIM-1

Query index 0 was solved

Query is NOT satisfied.

Spent 0.075861 on verification

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ tarjan\ --ltl-heur\ dist\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 1 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-00 FALSE TECHNIQUES EXPLICIT TARJAN WEAK_SKIP STUBBORN AUT_STUB HEURISTIC DIST_HEUR OPTIM-1

Time left: 3585

------------------- QUERY 2 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.107191 on verification

@@@0.20,154844@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ tarjan\ --ltl-heur\ dist\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 2 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-14 FALSE TECHNIQUES EXPLICIT TARJAN WEAK_SKIP STUBBORN AUT_STUB HEURISTIC DIST_HEUR OPTIM-1

Time left: 3585

------------------- QUERY 3 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.03054 on verification

@@@0.14,27324@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ ndfs\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 3 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-06 FALSE TECHNIQUES EXPLICIT NDFS WEAK_SKIP HEURISTIC AUTOMATON_HEUR OPTIM-1

Time left: 3584

------------------- QUERY 4 ----------------------

No solution found

Time left: 3283

------------------- QUERY 5 ----------------------

No solution found

Time left: 2980

------------------- QUERY 6 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.011187 on verification

@@@0.08,27604@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ ndfs\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 6 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-01 FALSE TECHNIQUES EXPLICIT NDFS WEAK_SKIP HEURISTIC AUTOMATON_HEUR OPTIM-1

Time left: 2980

------------------- QUERY 7 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 160.638 on verification

@@@160.70,318912@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ tarjan\ --ltl-heur\ dist\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 7 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-07 TRUE TECHNIQUES EXPLICIT TARJAN WEAK_SKIP STUBBORN AUT_STUB HEURISTIC DIST_HEUR OPTIM-1

Time left: 2819

------------------- QUERY 8 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.029781 on verification

@@@0.09,27520@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ ndfs\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 8 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-11 FALSE TECHNIQUES EXPLICIT NDFS WEAK_SKIP HEURISTIC AUTOMATON_HEUR OPTIM-1

Time left: 2819

------------------- QUERY 9 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.008701 on verification

@@@0.07,27500@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ ndfs\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 9 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-08 TRUE TECHNIQUES EXPLICIT NDFS WEAK_SKIP HEURISTIC AUTOMATON_HEUR OPTIM-1

Time left: 2818

------------------- QUERY 10 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.009723 on verification

@@@0.08,27456@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -ltl\ ndfs\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.r8o2aBxE9m /home/mcc/BenchKit/bin/tmp/tmp.fl6OqOkaG2 --binary-query-io 1 -x 10 -n

FORMULA FamilyReunion-COL-L00020M0002C001P001G001-LTLFireability-15 FALSE TECHNIQUES EXPLICIT NDFS WEAK_SKIP HEURISTIC AUTOMATON_HEUR OPTIM-1

Time left: 2818

------------------- QUERY 11 ----------------------

No solution found

Time left: 2517

------------------- QUERY 12 ----------------------

No solution found

Time left: 2215

------------------- QUERY 13 ----------------------

No solution found

Time left: 1914

---------------------------------------------------

Step 2: Sequential processing

---------------------------------------------------

Remaining 5 queries are verified sequentially.

Each query is verified for a dynamic timeout (at least 598 seconds)

Time left: 1914

------------------- QUERY 4 ----------------------

Running query 4 for 598 seconds. Remaining: 5 queries and 1914 seconds

No solution found

Time left: 1313

------------------- QUERY 5 ----------------------

Running query 5 for 598 seconds. Remaining: 4 queries and 1313 seconds

No solution found

Time left: 713

------------------- QUERY 11 ----------------------

Running query 11 for 598 seconds. Remaining: 3 queries and 713 seconds

No solution found

Time left: 112

------------------- QUERY 12 ----------------------

Time left: 112

---------------------------------------------------

Step 4: Random Parallel processing

---------------------------------------------------

Doing random parallel verification of individual queries (5 in total)

Each query is verified by 4 parallel strategies for 22 seconds

------------------- QUERY 4 ----------------------

No solution found

Time left: 88

------------------- QUERY 5 ----------------------

No solution found

Time left: 64

------------------- QUERY 11 ----------------------

No solution found

Time left: 39

------------------- QUERY 12 ----------------------

No solution found

Time left: 15

------------------- QUERY 13 ----------------------

No solution found

Time left: -3

Out of time, terminating!

terminated-with-cleanup

BK_STOP 1678622651166

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FamilyReunion-COL-L00020M0002C001P001G001"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="gold2022"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool gold2022"

echo " Input is FamilyReunion-COL-L00020M0002C001P001G001, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r190-tall-167838875400232"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/FamilyReunion-COL-L00020M0002C001P001G001.tgz

mv FamilyReunion-COL-L00020M0002C001P001G001 execution

cd execution

if [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "UpperBounds" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] || [ "LTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME LTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;