About the Execution of LTSMin+red for FamilyReunion-PT-L00200M0020C010P010G005

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16219.604 | 3600000.00 | 4735492.00 | 1588770.30 | ???????F??FFF??? | normal |

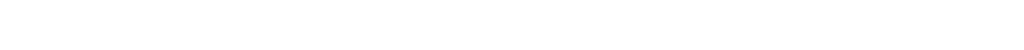

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r169-tall-167838855900428.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool ltsminxred

Input is FamilyReunion-PT-L00200M0020C010P010G005, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r169-tall-167838855900428

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 152M

-rw-r--r-- 1 mcc users 1.4M Feb 26 17:36 CTLCardinality.txt

-rw-r--r-- 1 mcc users 7.4M Feb 26 17:36 CTLCardinality.xml

-rw-r--r-- 1 mcc users 3.7M Feb 26 15:55 CTLFireability.txt

-rw-r--r-- 1 mcc users 13M Feb 26 15:55 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 7.0K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 608K Feb 25 16:05 LTLCardinality.txt

-rw-r--r-- 1 mcc users 2.4M Feb 25 16:05 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1018K Feb 25 16:05 LTLFireability.txt

-rw-r--r-- 1 mcc users 2.8M Feb 25 16:05 LTLFireability.xml

-rw-r--r-- 1 mcc users 2.9M Feb 26 21:32 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 17M Feb 26 21:32 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 9.0M Feb 26 20:20 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 32M Feb 26 20:20 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 126K Feb 25 16:05 UpperBounds.txt

-rw-r--r-- 1 mcc users 367K Feb 25 16:05 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 24 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 62M Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-00

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-01

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-02

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-03

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-04

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-05

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-06

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-07

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-08

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-09

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-10

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-11

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-12

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-13

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-14

FORMULA_NAME FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1678544473215

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=ltsminxred

BK_EXAMINATION=LTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=FamilyReunion-PT-L00200M0020C010P010G005

Applying reductions before tool ltsmin

Invoking reducer

Running Version 202303021504

[2023-03-11 14:21:15] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -timeout, 360, -rebuildPNML]

[2023-03-11 14:21:15] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-11 14:21:17] [INFO ] Load time of PNML (sax parser for PT used): 1908 ms

[2023-03-11 14:21:17] [INFO ] Transformed 143908 places.

[2023-03-11 14:21:17] [INFO ] Transformed 134279 transitions.

[2023-03-11 14:21:17] [INFO ] Parsed PT model containing 143908 places and 134279 transitions and 411469 arcs in 2472 ms.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 242 ms.

Working with output stream class java.io.PrintStream

Initial state reduction rules removed 4 formulas.

Reduce places removed 56 places and 0 transitions.

FORMULA FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-07 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-10 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-11 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-12 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Support contains 29158 out of 143852 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 143852/143852 places, 134279/134279 transitions.

Reduce places removed 674 places and 0 transitions.

Discarding 16884 places :

Implicit places reduction removed 16884 places

Iterating post reduction 0 with 17558 rules applied. Total rules applied 17558 place count 126294 transition count 134279

Discarding 1005 places :

Symmetric choice reduction at 1 with 1005 rule applications. Total rules 18563 place count 125289 transition count 132269

Iterating global reduction 1 with 1005 rules applied. Total rules applied 19568 place count 125289 transition count 132269

Discarding 5 places :

Symmetric choice reduction at 1 with 5 rule applications. Total rules 19573 place count 125284 transition count 131264

Iterating global reduction 1 with 5 rules applied. Total rules applied 19578 place count 125284 transition count 131264

Applied a total of 19578 rules in 12085 ms. Remains 125284 /143852 variables (removed 18568) and now considering 131264/134279 (removed 3015) transitions.

// Phase 1: matrix 131264 rows 125284 cols

[2023-03-11 14:22:37] [INFO ] Computed 13271 place invariants in 65750 ms

[2023-03-11 14:22:47] [INFO ] SMT solver returned unknown. Retrying;

[2023-03-11 14:22:47] [INFO ] Implicit Places using invariants in 75471 ms returned []

Implicit Place search using SMT only with invariants took 75498 ms to find 0 implicit places.

[2023-03-11 14:22:47] [INFO ] Invariant cache hit.

[2023-03-11 14:22:56] [INFO ] SMT solver returned unknown. Retrying;

[2023-03-11 14:22:56] [INFO ] Dead Transitions using invariants and state equation in 9292 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 125284/143852 places, 131264/134279 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 96893 ms. Remains : 125284/143852 places, 131264/134279 transitions.

Support contains 29158 out of 125284 places after structural reductions.

[2023-03-11 14:23:01] [INFO ] Flatten gal took : 3501 ms

[2023-03-11 14:23:05] [INFO ] Flatten gal took : 3381 ms

[2023-03-11 14:23:12] [INFO ] Input system was already deterministic with 131264 transitions.

Incomplete random walk after 10000 steps, including 2 resets, run finished after 3022 ms. (steps per millisecond=3 ) properties (out of 25) seen :9

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 108 ms. (steps per millisecond=9 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 17 ms. (steps per millisecond=58 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 17 ms. (steps per millisecond=58 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 168 ms. (steps per millisecond=5 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 13 ms. (steps per millisecond=77 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 11 ms. (steps per millisecond=91 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 11 ms. (steps per millisecond=91 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 11 ms. (steps per millisecond=91 ) properties (out of 16) seen :0

Running SMT prover for 16 properties.

[2023-03-11 14:23:17] [INFO ] Invariant cache hit.

java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Failed to assert expression: java.io.IOException: Stream close...

at fr.lip6.move.gal.structural.smt.SMTUtils.execAndCheckResult(SMTUtils.java:251)

at fr.lip6.move.gal.structural.smt.DeadlockTester.checkResults(DeadlockTester.java:797)

at fr.lip6.move.gal.structural.smt.DeadlockTester.verifyPossible(DeadlockTester.java:611)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMTIncremental(DeadlockTester.java:339)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMT(DeadlockTester.java:223)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.applyReductions(ReachabilitySolver.java:95)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.checkAtomicPropositionsLogic(AtomicReducerSR.java:105)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.strongReductions(AtomicReducerSR.java:44)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.preSolveForLogic(LTLPropertySolver.java:176)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.runStructuralLTLCheck(LTLPropertySolver.java:71)

at fr.lip6.move.gal.application.Application.startNoEx(Application.java:762)

at fr.lip6.move.gal.application.Application.start(Application.java:178)

at fr.lip6.move.gal.itscl.application.Application.start(Application.java:45)

at org.eclipse.equinox.internal.app.EclipseAppHandle.run(EclipseAppHandle.java:203)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.runApplication(EclipseAppLauncher.java:136)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.start(EclipseAppLauncher.java:104)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:402)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:255)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native Method)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(NativeMethodAccessorImpl.java:77)

at java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

at java.base/java.lang.reflect.Method.invoke(Method.java:568)

at org.eclipse.equinox.launcher.Main.invokeFramework(Main.java:659)

at org.eclipse.equinox.launcher.Main.basicRun(Main.java:596)

at org.eclipse.equinox.launcher.Main.run(Main.java:1467)

at org.eclipse.equinox.launcher.Main.main(Main.java:1440)

[2023-03-11 14:23:42] [WARNING] SMT solver failed with error :SMT solver raised an error when submitting script.... while checking expressions.

[2023-03-11 14:23:42] [INFO ] After 25034ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0

Fused 16 Parikh solutions to 1 different solutions.

Parikh walk visited 0 properties in 0 ms.

Support contains 5041 out of 125284 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 125284/125284 places, 131264/131264 transitions.

Graph (complete) has 185724 edges and 125284 vertex of which 123670 are kept as prefixes of interest. Removing 1614 places using SCC suffix rule.177 ms

Discarding 1614 places :

Also discarding 1413 output transitions

Drop transitions removed 1413 transitions

Drop transitions removed 202 transitions

Reduce isomorphic transitions removed 202 transitions.

Discarding 8442 places :

Implicit places reduction removed 8442 places

Drop transitions removed 69689 transitions

Trivial Post-agglo rules discarded 69689 transitions

Performed 69689 trivial Post agglomeration. Transition count delta: 69689

Iterating post reduction 0 with 78333 rules applied. Total rules applied 78334 place count 115228 transition count 59960

Reduce places removed 69689 places and 0 transitions.

Performed 239 Post agglomeration using F-continuation condition.Transition count delta: 239

Iterating post reduction 1 with 69928 rules applied. Total rules applied 148262 place count 45539 transition count 59721

Reduce places removed 239 places and 0 transitions.

Iterating post reduction 2 with 239 rules applied. Total rules applied 148501 place count 45300 transition count 59721

Performed 7634 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 7634 Pre rules applied. Total rules applied 148501 place count 45300 transition count 52087

Deduced a syphon composed of 7634 places in 34 ms

Ensure Unique test removed 2811 places

Reduce places removed 10445 places and 0 transitions.

Iterating global reduction 3 with 18079 rules applied. Total rules applied 166580 place count 34855 transition count 52087

Discarding 2 places :

Implicit places reduction removed 2 places

Drop transitions removed 198 transitions

Trivial Post-agglo rules discarded 198 transitions

Performed 198 trivial Post agglomeration. Transition count delta: 198

Iterating post reduction 3 with 200 rules applied. Total rules applied 166780 place count 34853 transition count 51889

Reduce places removed 198 places and 0 transitions.

Performed 2 Post agglomeration using F-continuation condition.Transition count delta: 2

Iterating post reduction 4 with 200 rules applied. Total rules applied 166980 place count 34655 transition count 51887

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 5 with 2 rules applied. Total rules applied 166982 place count 34653 transition count 51887

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 6 with 1 Pre rules applied. Total rules applied 166982 place count 34653 transition count 51886

Deduced a syphon composed of 1 places in 44 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 6 with 2 rules applied. Total rules applied 166984 place count 34652 transition count 51886

Performed 5426 Post agglomeration using F-continuation condition.Transition count delta: 5426

Deduced a syphon composed of 5426 places in 31 ms

Reduce places removed 5426 places and 0 transitions.

Iterating global reduction 6 with 10852 rules applied. Total rules applied 177836 place count 29226 transition count 46460

Free-agglomeration rule applied 2200 times.

Iterating global reduction 6 with 2200 rules applied. Total rules applied 180036 place count 29226 transition count 44260

Ensure Unique test removed 200 places

Reduce places removed 2400 places and 0 transitions.

Ensure Unique test removed 2000 transitions

Reduce isomorphic transitions removed 2000 transitions.

Iterating post reduction 6 with 4400 rules applied. Total rules applied 184436 place count 26826 transition count 42260

Performed 200 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 7 with 200 Pre rules applied. Total rules applied 184436 place count 26826 transition count 42060

Deduced a syphon composed of 200 places in 19 ms

Ensure Unique test removed 200 places

Reduce places removed 400 places and 0 transitions.

Iterating global reduction 7 with 600 rules applied. Total rules applied 185036 place count 26426 transition count 42060

Free-agglomeration rule (complex) applied 7048 times.

Iterating global reduction 7 with 7048 rules applied. Total rules applied 192084 place count 26426 transition count 85112

Ensure Unique test removed 402 places

Reduce places removed 7450 places and 0 transitions.

Iterating post reduction 7 with 7450 rules applied. Total rules applied 199534 place count 18976 transition count 85112

Discarding 40 places :

Symmetric choice reduction at 8 with 40 rule applications. Total rules 199574 place count 18936 transition count 28972

Iterating global reduction 8 with 40 rules applied. Total rules applied 199614 place count 18936 transition count 28972

Ensure Unique test removed 10 transitions

Reduce isomorphic transitions removed 10 transitions.

Iterating post reduction 8 with 10 rules applied. Total rules applied 199624 place count 18936 transition count 28962

Applied a total of 199624 rules in 39570 ms. Remains 18936 /125284 variables (removed 106348) and now considering 28962/131264 (removed 102302) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 39573 ms. Remains : 18936/125284 places, 28962/131264 transitions.

Incomplete random walk after 10000 steps, including 4 resets, run finished after 972 ms. (steps per millisecond=10 ) properties (out of 16) seen :10

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 38 ms. (steps per millisecond=263 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 37 ms. (steps per millisecond=270 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 39 ms. (steps per millisecond=256 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 37 ms. (steps per millisecond=270 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 36 ms. (steps per millisecond=277 ) properties (out of 6) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 36 ms. (steps per millisecond=277 ) properties (out of 6) seen :0

Running SMT prover for 6 properties.

// Phase 1: matrix 28962 rows 18936 cols

[2023-03-11 14:24:25] [INFO ] Computed 1014 place invariants in 2250 ms

[2023-03-11 14:24:30] [INFO ] [Real]Absence check using 0 positive and 1014 generalized place invariants in 1068 ms returned sat

[2023-03-11 14:24:50] [INFO ] After 18912ms SMT Verify possible using state equation in real domain returned unsat :0 sat :5

[2023-03-11 14:24:50] [INFO ] After 18956ms SMT Verify possible using trap constraints in real domain returned unsat :0 sat :5

Attempting to minimize the solution found.

Minimization took 9 ms.

[2023-03-11 14:24:50] [INFO ] After 25065ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :5

Fused 6 Parikh solutions to 1 different solutions.

Parikh walk visited 0 properties in 0 ms.

Support contains 11 out of 18936 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 18936/18936 places, 28962/28962 transitions.

Graph (complete) has 47081 edges and 18936 vertex of which 17336 are kept as prefixes of interest. Removing 1600 places using SCC suffix rule.10 ms

Discarding 1600 places :

Also discarding 1400 output transitions

Drop transitions removed 1400 transitions

Drop transitions removed 2212 transitions

Trivial Post-agglo rules discarded 2212 transitions

Performed 2212 trivial Post agglomeration. Transition count delta: 2212

Iterating post reduction 0 with 2212 rules applied. Total rules applied 2213 place count 17336 transition count 25350

Reduce places removed 2212 places and 0 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Iterating post reduction 1 with 2213 rules applied. Total rules applied 4426 place count 15124 transition count 25349

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 2 with 1 rules applied. Total rules applied 4427 place count 15123 transition count 25349

Performed 205 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 205 Pre rules applied. Total rules applied 4427 place count 15123 transition count 25144

Deduced a syphon composed of 205 places in 6 ms

Ensure Unique test removed 1 places

Reduce places removed 206 places and 0 transitions.

Iterating global reduction 3 with 411 rules applied. Total rules applied 4838 place count 14917 transition count 25144

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 1 Pre rules applied. Total rules applied 4838 place count 14917 transition count 25143

Deduced a syphon composed of 1 places in 7 ms

Ensure Unique test removed 1 places

Reduce places removed 2 places and 0 transitions.

Iterating global reduction 3 with 3 rules applied. Total rules applied 4841 place count 14915 transition count 25143

Discarding 197 places :

Symmetric choice reduction at 3 with 197 rule applications. Total rules 5038 place count 14718 transition count 23961

Iterating global reduction 3 with 197 rules applied. Total rules applied 5235 place count 14718 transition count 23961

Performed 2212 Post agglomeration using F-continuation condition.Transition count delta: 2212

Deduced a syphon composed of 2212 places in 6 ms

Reduce places removed 2212 places and 0 transitions.

Iterating global reduction 3 with 4424 rules applied. Total rules applied 9659 place count 12506 transition count 21749

Free-agglomeration rule (complex) applied 2416 times.

Iterating global reduction 3 with 2416 rules applied. Total rules applied 12075 place count 12506 transition count 50368

Ensure Unique test removed 201 places

Reduce places removed 2617 places and 0 transitions.

Iterating post reduction 3 with 2617 rules applied. Total rules applied 14692 place count 9889 transition count 50368

Discarding 8052 places :

Symmetric choice reduction at 4 with 8052 rule applications. Total rules 22744 place count 1837 transition count 10266

Ensure Unique test removed 599 places

Iterating global reduction 4 with 8651 rules applied. Total rules applied 31395 place count 1238 transition count 10266

Ensure Unique test removed 8036 transitions

Reduce isomorphic transitions removed 8036 transitions.

Drop transitions removed 198 transitions

Trivial Post-agglo rules discarded 198 transitions

Performed 198 trivial Post agglomeration. Transition count delta: 198

Iterating post reduction 4 with 8234 rules applied. Total rules applied 39629 place count 1238 transition count 2032

Reduce places removed 198 places and 0 transitions.

Iterating post reduction 5 with 198 rules applied. Total rules applied 39827 place count 1040 transition count 2032

Performed 201 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 6 with 201 Pre rules applied. Total rules applied 39827 place count 1040 transition count 1831

Deduced a syphon composed of 201 places in 0 ms

Reduce places removed 201 places and 0 transitions.

Iterating global reduction 6 with 402 rules applied. Total rules applied 40229 place count 839 transition count 1831

Discarding 200 places :

Symmetric choice reduction at 6 with 200 rule applications. Total rules 40429 place count 639 transition count 637

Iterating global reduction 6 with 200 rules applied. Total rules applied 40629 place count 639 transition count 637

Discarding 196 places :

Symmetric choice reduction at 6 with 196 rule applications. Total rules 40825 place count 443 transition count 441

Iterating global reduction 6 with 196 rules applied. Total rules applied 41021 place count 443 transition count 441

Discarding 196 places :

Symmetric choice reduction at 6 with 196 rule applications. Total rules 41217 place count 247 transition count 245

Iterating global reduction 6 with 196 rules applied. Total rules applied 41413 place count 247 transition count 245

Discarding 193 places :

Symmetric choice reduction at 6 with 193 rule applications. Total rules 41606 place count 54 transition count 52

Iterating global reduction 6 with 193 rules applied. Total rules applied 41799 place count 54 transition count 52

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 6 with 2 rules applied. Total rules applied 41801 place count 53 transition count 51

Partial Free-agglomeration rule applied 3 times.

Drop transitions removed 3 transitions

Iterating global reduction 6 with 3 rules applied. Total rules applied 41804 place count 53 transition count 51

Reduce places removed 5 places and 5 transitions.

Iterating global reduction 6 with 5 rules applied. Total rules applied 41809 place count 48 transition count 46

Applied a total of 41809 rules in 5150 ms. Remains 48 /18936 variables (removed 18888) and now considering 46/28962 (removed 28916) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 5150 ms. Remains : 48/18936 places, 46/28962 transitions.

Computed a total of 125284 stabilizing places and 131264 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 125284 transition count 131264

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Running Spot : '/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.ltl.spot.binaries_1.0.0.202303021504/bin/ltl2tgba-linux64' '--check=stutter' '--hoaf=tv' '-f' '!(X(X(X(F((G(p1)||p0))))))'

Support contains 6432 out of 125284 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 125284/125284 places, 131264/131264 transitions.

Discarding 8442 places :

Implicit places reduction removed 8442 places

Iterating post reduction 0 with 8442 rules applied. Total rules applied 8442 place count 116842 transition count 131264

Applied a total of 8442 rules in 2793 ms. Remains 116842 /125284 variables (removed 8442) and now considering 131264/131264 (removed 0) transitions.

// Phase 1: matrix 131264 rows 116842 cols

[2023-03-11 14:25:23] [INFO ] Computed 4829 place invariants in 23774 ms

[2023-03-11 14:25:32] [INFO ] SMT solver returned unknown. Retrying;

[2023-03-11 14:25:32] [INFO ] Implicit Places using invariants in 32761 ms returned []

Implicit Place search using SMT only with invariants took 32762 ms to find 0 implicit places.

[2023-03-11 14:25:32] [INFO ] Invariant cache hit.

[2023-03-11 14:25:41] [INFO ] SMT solver returned unknown. Retrying;

[2023-03-11 14:25:41] [INFO ] Dead Transitions using invariants and state equation in 9354 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 116842/125284 places, 131264/131264 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 44916 ms. Remains : 116842/125284 places, 131264/131264 transitions.

Stuttering acceptance computed with spot in 238 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Running random walk in product with property : FamilyReunion-PT-L00200M0020C010P010G005-LTLFireability-00 automaton TGBA Formula[mat=[[{ cond=(AND p1 (NOT p0)), acceptance={} source=0 dest: 0}, { cond=(AND (NOT p1) (NOT p0)), acceptance={0} source=0 dest: 0}], [{ cond=true, acceptance={} source=1 dest: 0}], [{ cond=true, acceptance={} source=2 dest: 1}], [{ cond=true, acceptance={} source=3 dest: 2}]], initial=3, aps=[p1:(OR (GEQ s81552 1) (GEQ s82072 1) (GEQ s83112 1) (GEQ s82592 1) (GEQ s84152 1) (GEQ s83632 1) (GEQ s84672 1) (GEQ s85192 1) (GEQ s84331 1) (GEQ s83291 ...], nbAcceptance=1, properties=[trans-labels, explicit-labels, trans-acc, deterministic, no-univ-branch, unambiguous, semi-deterministic, stutter-sensitive], stateDesc=[null, null, null, null][false, false, false, false]]

Product exploration timeout after 38350 steps with 9 reset in 10004 ms.

Product exploration timeout after 39560 steps with 9 reset in 10002 ms.

Computed a total of 116842 stabilizing places and 131264 stable transitions

Complete graph has no SCC; deadlocks are unavoidable. place count 116842 transition count 131264

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge (and all enablings converge to false).

Detected that all paths lead to deadlock. Applying this knowledge to assert that all AP eventually converge : F ( (Ga|G!a) & (Gb|G!b)...)

Could not satisfy deadlock states : solver returned unknown

Knowledge obtained : [(AND (NOT p1) (NOT p0)), true, (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : []

Knowledge based reduction with 4 factoid took 170 ms. Reduced automaton from 4 states, 5 edges and 2 AP (stutter sensitive) to 4 states, 5 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 124 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Finished random walk after 1954 steps, including 0 resets, run visited all 2 properties in 525 ms. (steps per millisecond=3 )

Knowledge obtained : [(AND (NOT p1) (NOT p0)), true, (F (OR (G p1) (G (NOT p1)))), (F (OR (G p0) (G (NOT p0))))]

False Knowledge obtained : [(F (AND p1 (NOT p0))), (F (NOT (AND (NOT p1) (NOT p0))))]

Knowledge based reduction with 4 factoid took 286 ms. Reduced automaton from 4 states, 5 edges and 2 AP (stutter sensitive) to 4 states, 5 edges and 2 AP (stutter sensitive).

Stuttering acceptance computed with spot in 134 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

Stuttering acceptance computed with spot in 122 ms :[(AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0)), (AND (NOT p1) (NOT p0))]

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_0_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

TIME LIMIT: Killed by timeout after 223 seconds

MemTotal: 16393216 kB

MemFree: 1746044 kB

After kill :

MemTotal: 16393216 kB

MemFree: 16273688 kB

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_1_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

TIME LIMIT: Killed by timeout after 223 seconds

MemTotal: 16393216 kB

MemFree: 183164 kB

After kill :

MemTotal: 16393216 kB

MemFree: 16182780 kB

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_2_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_3_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_4_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_5_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_6_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_7_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

TIME LIMIT: Killed by timeout after 223 seconds

MemTotal: 16393216 kB

MemFree: 152144 kB

After kill :

MemTotal: 16393216 kB

MemFree: 16192208 kB

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_8_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_9_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

pnml2lts-mc model.pnml -s80% --procs=4 --ltl=/tmp/706/ltl_10_ --buchi-type=spotba --strategy=ufscc --ltl-semantics=spin --state=tree

TIME LIMIT: Killed by timeout after 3600 seconds

MemTotal: 16393216 kB

MemFree: 167764 kB

After kill :

MemTotal: 16393216 kB

MemFree: 16222268 kB

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination LTLFireability -timeout 360 -rebuildPNML

mcc2023

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FamilyReunion-PT-L00200M0020C010P010G005"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="ltsminxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool ltsminxred"

echo " Input is FamilyReunion-PT-L00200M0020C010P010G005, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r169-tall-167838855900428"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/FamilyReunion-PT-L00200M0020C010P010G005.tgz

mv FamilyReunion-PT-L00200M0020C010P010G005 execution

cd execution

if [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "UpperBounds" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] || [ "LTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME LTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;