About the Execution of Smart+red for DLCround-PT-03b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 6095.275 | 3600000.00 | 3640347.00 | 12247.80 | FFTFTTFTFFFFTFTT | normal |

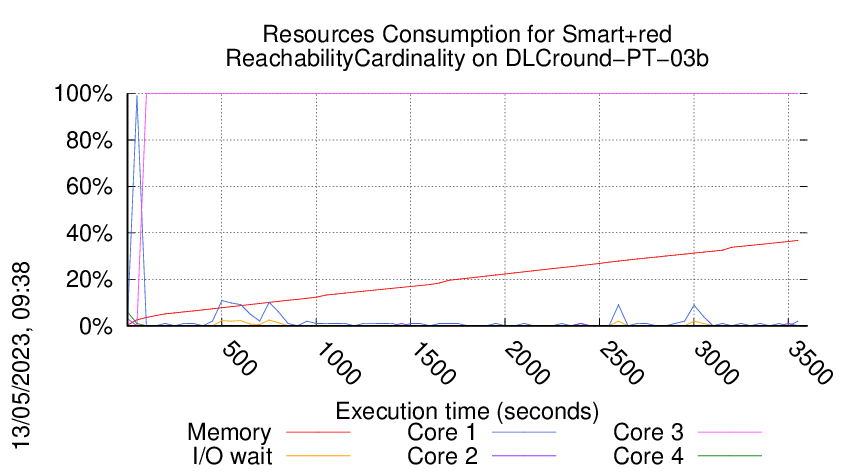

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r107-tall-167814484500630.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool smartxred

Input is DLCround-PT-03b, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r107-tall-167814484500630

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 860K

-rw-r--r-- 1 mcc users 6.2K Feb 25 18:20 CTLCardinality.txt

-rw-r--r-- 1 mcc users 65K Feb 25 18:20 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.7K Feb 25 18:20 CTLFireability.txt

-rw-r--r-- 1 mcc users 52K Feb 25 18:20 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.5K Feb 25 15:52 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Feb 25 15:52 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K Feb 25 15:52 LTLFireability.txt

-rw-r--r-- 1 mcc users 15K Feb 25 15:52 LTLFireability.xml

-rw-r--r-- 1 mcc users 13K Feb 25 18:21 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 131K Feb 25 18:21 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 6.2K Feb 25 18:20 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 47K Feb 25 18:20 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 25 15:52 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Feb 25 15:52 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 432K Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-00

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-01

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-02

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-03

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-04

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-05

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-06

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-07

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-08

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-09

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-10

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-11

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-12

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-13

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-14

FORMULA_NAME DLCround-PT-03b-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1678404431050

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=smartxred

BK_EXAMINATION=ReachabilityCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=DLCround-PT-03b

Applying reductions before tool smart

Invoking reducer

Running Version 202303021504

[2023-03-09 23:27:12] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -timeout, 360, -rebuildPNML]

[2023-03-09 23:27:12] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-09 23:27:12] [INFO ] Load time of PNML (sax parser for PT used): 98 ms

[2023-03-09 23:27:12] [INFO ] Transformed 1383 places.

[2023-03-09 23:27:12] [INFO ] Transformed 1887 transitions.

[2023-03-09 23:27:12] [INFO ] Found NUPN structural information;

[2023-03-09 23:27:12] [INFO ] Parsed PT model containing 1383 places and 1887 transitions and 4809 arcs in 174 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 15 ms.

Working with output stream class java.io.PrintStream

FORMULA DLCround-PT-03b-ReachabilityCardinality-02 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-03b-ReachabilityCardinality-03 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-03b-ReachabilityCardinality-12 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-03b-ReachabilityCardinality-15 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Incomplete random walk after 10000 steps, including 2 resets, run finished after 411 ms. (steps per millisecond=24 ) properties (out of 12) seen :8

FORMULA DLCround-PT-03b-ReachabilityCardinality-14 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-13 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-11 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-10 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-07 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-06 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-05 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-04 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 65 ms. (steps per millisecond=153 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 35 ms. (steps per millisecond=285 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 21 ms. (steps per millisecond=476 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 32 ms. (steps per millisecond=312 ) properties (out of 4) seen :0

Running SMT prover for 4 properties.

// Phase 1: matrix 1887 rows 1383 cols

[2023-03-09 23:27:13] [INFO ] Computed 52 place invariants in 25 ms

[2023-03-09 23:27:13] [INFO ] After 460ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:4

[2023-03-09 23:27:14] [INFO ] [Nat]Absence check using 52 positive place invariants in 31 ms returned sat

[2023-03-09 23:27:15] [INFO ] After 846ms SMT Verify possible using state equation in natural domain returned unsat :1 sat :3

[2023-03-09 23:27:15] [INFO ] Deduced a trap composed of 132 places in 214 ms of which 6 ms to minimize.

[2023-03-09 23:27:15] [INFO ] Deduced a trap composed of 75 places in 169 ms of which 1 ms to minimize.

[2023-03-09 23:27:15] [INFO ] Trap strengthening (SAT) tested/added 3/2 trap constraints in 597 ms

[2023-03-09 23:27:16] [INFO ] Deduced a trap composed of 132 places in 166 ms of which 1 ms to minimize.

[2023-03-09 23:27:16] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 293 ms

[2023-03-09 23:27:16] [INFO ] After 2103ms SMT Verify possible using trap constraints in natural domain returned unsat :1 sat :3

Attempting to minimize the solution found.

Minimization took 352 ms.

[2023-03-09 23:27:16] [INFO ] After 2859ms SMT Verify possible using all constraints in natural domain returned unsat :1 sat :3

FORMULA DLCround-PT-03b-ReachabilityCardinality-09 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 4 Parikh solutions to 3 different solutions.

FORMULA DLCround-PT-03b-ReachabilityCardinality-00 FALSE TECHNIQUES TOPOLOGICAL PARIKH_WALK

Parikh walk visited 1 properties in 50 ms.

Support contains 46 out of 1383 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1383/1383 places, 1887/1887 transitions.

Graph (trivial) has 1248 edges and 1383 vertex of which 202 / 1383 are part of one of the 18 SCC in 17 ms

Free SCC test removed 184 places

Drop transitions removed 208 transitions

Reduce isomorphic transitions removed 208 transitions.

Drop transitions removed 540 transitions

Trivial Post-agglo rules discarded 540 transitions

Performed 540 trivial Post agglomeration. Transition count delta: 540

Iterating post reduction 0 with 540 rules applied. Total rules applied 541 place count 1199 transition count 1139

Reduce places removed 540 places and 0 transitions.

Ensure Unique test removed 17 transitions

Reduce isomorphic transitions removed 17 transitions.

Drop transitions removed 17 transitions

Trivial Post-agglo rules discarded 17 transitions

Performed 17 trivial Post agglomeration. Transition count delta: 17

Iterating post reduction 1 with 574 rules applied. Total rules applied 1115 place count 659 transition count 1105

Reduce places removed 17 places and 0 transitions.

Ensure Unique test removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Drop transitions removed 2 transitions

Trivial Post-agglo rules discarded 2 transitions

Performed 2 trivial Post agglomeration. Transition count delta: 2

Iterating post reduction 2 with 21 rules applied. Total rules applied 1136 place count 642 transition count 1101

Reduce places removed 2 places and 0 transitions.

Performed 33 Post agglomeration using F-continuation condition.Transition count delta: 33

Iterating post reduction 3 with 35 rules applied. Total rules applied 1171 place count 640 transition count 1068

Reduce places removed 33 places and 0 transitions.

Ensure Unique test removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 4 with 35 rules applied. Total rules applied 1206 place count 607 transition count 1066

Performed 16 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 16 Pre rules applied. Total rules applied 1206 place count 607 transition count 1050

Deduced a syphon composed of 16 places in 3 ms

Reduce places removed 16 places and 0 transitions.

Iterating global reduction 5 with 32 rules applied. Total rules applied 1238 place count 591 transition count 1050

Discarding 123 places :

Symmetric choice reduction at 5 with 123 rule applications. Total rules 1361 place count 468 transition count 927

Iterating global reduction 5 with 123 rules applied. Total rules applied 1484 place count 468 transition count 927

Ensure Unique test removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 5 with 2 rules applied. Total rules applied 1486 place count 468 transition count 925

Performed 40 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 6 with 40 Pre rules applied. Total rules applied 1486 place count 468 transition count 885

Deduced a syphon composed of 40 places in 3 ms

Reduce places removed 40 places and 0 transitions.

Iterating global reduction 6 with 80 rules applied. Total rules applied 1566 place count 428 transition count 885

Discarding 21 places :

Symmetric choice reduction at 6 with 21 rule applications. Total rules 1587 place count 407 transition count 750

Iterating global reduction 6 with 21 rules applied. Total rules applied 1608 place count 407 transition count 750

Ensure Unique test removed 5 transitions

Reduce isomorphic transitions removed 5 transitions.

Iterating post reduction 6 with 5 rules applied. Total rules applied 1613 place count 407 transition count 745

Performed 108 Post agglomeration using F-continuation condition with reduction of 4 identical transitions.

Deduced a syphon composed of 108 places in 0 ms

Reduce places removed 108 places and 0 transitions.

Iterating global reduction 7 with 216 rules applied. Total rules applied 1829 place count 299 transition count 633

Ensure Unique test removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 7 with 2 rules applied. Total rules applied 1831 place count 299 transition count 631

Discarding 5 places :

Symmetric choice reduction at 8 with 5 rule applications. Total rules 1836 place count 294 transition count 596

Iterating global reduction 8 with 5 rules applied. Total rules applied 1841 place count 294 transition count 596

Performed 37 Post agglomeration using F-continuation condition with reduction of 12 identical transitions.

Deduced a syphon composed of 37 places in 0 ms

Reduce places removed 37 places and 0 transitions.

Iterating global reduction 8 with 74 rules applied. Total rules applied 1915 place count 257 transition count 786

Drop transitions removed 17 transitions

Reduce isomorphic transitions removed 17 transitions.

Iterating post reduction 8 with 17 rules applied. Total rules applied 1932 place count 257 transition count 769

Discarding 7 places :

Symmetric choice reduction at 9 with 7 rule applications. Total rules 1939 place count 250 transition count 680

Iterating global reduction 9 with 7 rules applied. Total rules applied 1946 place count 250 transition count 680

Ensure Unique test removed 14 transitions

Reduce isomorphic transitions removed 14 transitions.

Iterating post reduction 9 with 14 rules applied. Total rules applied 1960 place count 250 transition count 666

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -13

Deduced a syphon composed of 1 places in 1 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 10 with 2 rules applied. Total rules applied 1962 place count 249 transition count 679

Drop transitions removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 10 with 2 rules applied. Total rules applied 1964 place count 249 transition count 677

Drop transitions removed 46 transitions

Redundant transition composition rules discarded 46 transitions

Iterating global reduction 11 with 46 rules applied. Total rules applied 2010 place count 249 transition count 631

Discarding 3 places :

Symmetric choice reduction at 11 with 3 rule applications. Total rules 2013 place count 246 transition count 608

Iterating global reduction 11 with 3 rules applied. Total rules applied 2016 place count 246 transition count 608

Ensure Unique test removed 3 transitions

Reduce isomorphic transitions removed 3 transitions.

Iterating post reduction 11 with 3 rules applied. Total rules applied 2019 place count 246 transition count 605

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -12

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 12 with 2 rules applied. Total rules applied 2021 place count 245 transition count 617

Drop transitions removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 12 with 2 rules applied. Total rules applied 2023 place count 245 transition count 615

Free-agglomeration rule applied 87 times with reduction of 32 identical transitions.

Iterating global reduction 13 with 87 rules applied. Total rules applied 2110 place count 245 transition count 496

Reduce places removed 87 places and 0 transitions.

Drop transitions removed 83 transitions

Ensure Unique test removed 7 transitions

Reduce isomorphic transitions removed 90 transitions.

Iterating post reduction 13 with 177 rules applied. Total rules applied 2287 place count 158 transition count 406

Discarding 3 places :

Symmetric choice reduction at 14 with 3 rule applications. Total rules 2290 place count 155 transition count 394

Iterating global reduction 14 with 3 rules applied. Total rules applied 2293 place count 155 transition count 394

Drop transitions removed 20 transitions

Redundant transition composition rules discarded 20 transitions

Iterating global reduction 14 with 20 rules applied. Total rules applied 2313 place count 155 transition count 374

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 2314 place count 154 transition count 374

Partial Free-agglomeration rule applied 4 times.

Drop transitions removed 4 transitions

Iterating global reduction 15 with 4 rules applied. Total rules applied 2318 place count 154 transition count 374

Applied a total of 2318 rules in 303 ms. Remains 154 /1383 variables (removed 1229) and now considering 374/1887 (removed 1513) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 304 ms. Remains : 154/1383 places, 374/1887 transitions.

Finished random walk after 3242 steps, including 0 resets, run visited all 2 properties in 26 ms. (steps per millisecond=124 )

FORMULA DLCround-PT-03b-ReachabilityCardinality-08 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-03b-ReachabilityCardinality-01 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

All properties solved without resorting to model-checking.

Total runtime 4759 ms.

======================================================

========== this is Smart for the MCC'2018 ============

======================================================

Running DLCround (PT), instance 03b

Examination ReachabilityCardinality

Parser /home/mcc/BenchKit/bin//../reducer/bin//../../smart/bin//parser/Cardinality.jar

Model checker /home/mcc/BenchKit/bin//../reducer/bin//../../smart/bin//rem_exec//smart

GOT IT HERE. BS

Petri model created: 1383 places, 1887 transitions, 4809 arcs.

Final Score: 159847.241

Took : 50 seconds

Reachability Cardinality file is: ReachabilityCardinality.xml

READY TO PARSE. BS

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-00 (reachable &!potential( (! ( ( (! ( (! ( ( (tk(P136)) <= (tk(P716)) ) & ( ( (tk(P1072)) <= (tk(P393)) ) | ( (tk(P764)) <= (tk(P337)) ) ) )) | ( ( (! ( (tk(P1042)) <= ( 1 ) )) | ( (tk(P1372)) <= (tk(P365)) ) ) & ( (tk(P736)) <= (tk(P414)) ) ) )) | ( ( (tk(P1049)) <= (tk(P728)) ) & (! ( ( ( ( (tk(P1190)) <= (tk(P532)) ) & ( (tk(P78)) <= ( 1 ) ) ) | (! ( (tk(P858)) <= ( 0 ) )) ) | ( (! ( (tk(P288)) <= ( 0 ) )) | ( ( 1 ) <= (tk(P847)) ) ) )) ) ) & ( ( (! ( ( (tk(P930)) <= ( 1 ) ) & ( ( ( ( ( 1 ) <= (tk(P609)) ) | ( (tk(P435)) <= (tk(P265)) ) ) & ( ( (tk(P2)) <= (tk(P397)) ) & ( ( 1 ) <= (tk(P1260)) ) ) ) | ( (tk(P846)) <= (tk(P295)) ) ) )) & ( ( (tk(P905)) <= (tk(P598)) ) | ( ( ( ( ( (tk(P197)) <= (tk(P465)) ) & ( (tk(P1107)) <= (tk(P734)) ) ) & ( (tk(P832)) <= (tk(P383)) ) ) & (! ( ( (tk(P1345)) <= ( 0 ) ) & ( (tk(P1320)) <= (tk(P871)) ) )) ) | ( ( ( ( (tk(P1249)) <= (tk(P440)) ) & ( (tk(P1291)) <= (tk(P335)) ) ) & ( ( ( 1 ) <= (tk(P151)) ) & ( (tk(P985)) <= (tk(P1005)) ) ) ) | (! ( ( ( 1 ) <= (tk(P962)) ) & ( ( 1 ) <= (tk(P582)) ) )) ) ) ) ) & ( (! ( ( (tk(P273)) <= (tk(P674)) ) & ( ( ( ( (tk(P1085)) <= ( 1 ) ) | ( (tk(P4)) <= (tk(P83)) ) ) | ( (tk(P750)) <= (tk(P1117)) ) ) & ( ( (tk(P1212)) <= (tk(P1214)) ) | ( ( ( 1 ) <= (tk(P1223)) ) | ( (tk(P178)) <= (tk(P1232)) ) ) ) ) )) & ( ( (tk(P623)) <= (tk(P1007)) ) | ( (tk(P893)) <= (tk(P127)) ) ) ) ) ))))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-01 (reachable &!potential( ( ( (! ( (tk(P1199)) <= (tk(P782)) )) | ( (tk(P880)) <= ( 1 ) ) ) & ( ( ( ( ( ( ( 1 ) <= (tk(P364)) ) | ( (tk(P1066)) <= (tk(P350)) ) ) | ( (tk(P1166)) <= ( 0 ) ) ) | ( ( ( ( ( ( ( 1 ) <= (tk(P1270)) ) & ( (tk(P826)) <= (tk(P114)) ) ) | ( (tk(P754)) <= ( 1 ) ) ) | ( ( ( 1 ) <= (tk(P88)) ) & ( ( (tk(P1264)) <= (tk(P729)) ) & ( (tk(P860)) <= ( 0 ) ) ) ) ) & ( ( ( (tk(P219)) <= ( 1 ) ) & ( ( 1 ) <= (tk(P214)) ) ) | ( (tk(P1204)) <= ( 1 ) ) ) ) & (! ( ( (tk(P317)) <= (tk(P611)) ) | ( (! ( ( 1 ) <= (tk(P519)) )) & ( ( (tk(P799)) <= (tk(P945)) ) & ( (tk(P1298)) <= (tk(P1078)) ) ) ) )) ) ) | ( (! ( ( ( (! ( ( 1 ) <= (tk(P566)) )) & ( ( (tk(P398)) <= ( 0 ) ) | ( (tk(P956)) <= (tk(P1209)) ) ) ) | ( (tk(P995)) <= (tk(P338)) ) ) | ( ( ( ( ( 1 ) <= (tk(P685)) ) & ( (tk(P195)) <= (tk(P680)) ) ) & (! ( (tk(P490)) <= (tk(P1303)) )) ) | ( (! ( (tk(P273)) <= (tk(P1238)) )) & ( ( (tk(P857)) <= ( 1 ) ) & ( (tk(P633)) <= ( 0 ) ) ) ) ) )) | ( ( (! ( (! ( (tk(P377)) <= (tk(P135)) )) & ( (tk(P289)) <= ( 1 ) ) )) & ( ( ( 1 ) <= (tk(P1136)) ) | ( ( ( (tk(P592)) <= (tk(P520)) ) | ( (tk(P1057)) <= ( 0 ) ) ) | (! ( (tk(P1101)) <= ( 1 ) )) ) ) ) & ( (! ( ( ( 1 ) <= (tk(P192)) ) & ( (tk(P1049)) <= ( 0 ) ) )) & ( (tk(P562)) <= ( 0 ) ) ) ) ) ) | (! ( ( 1 ) <= (tk(P1107)) )) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-02 (reachable &!potential( ( ( (tk(P896)) <= (tk(P128)) ) | (! ( (! ( ( ( ( (! ( (tk(P1320)) <= ( 1 ) )) | ( ( (tk(P355)) <= (tk(P1006)) ) & ( (tk(P837)) <= ( 1 ) ) ) ) | ( ( ( 1 ) <= (tk(P1267)) ) | ( ( (tk(P73)) <= (tk(P310)) ) | ( (tk(P645)) <= (tk(P584)) ) ) ) ) | ( (tk(P311)) <= (tk(P630)) ) ) & ( ( ( ( ( ( 1 ) <= (tk(P722)) ) & ( (tk(P1159)) <= (tk(P217)) ) ) | ( (tk(P871)) <= ( 1 ) ) ) | (! ( (tk(P142)) <= (tk(P69)) )) ) | ( (tk(P126)) <= ( 1 ) ) ) )) & ( ( (tk(P399)) <= ( 1 ) ) & (! ( ( (tk(P453)) <= ( 1 ) ) | ( ( ( (tk(P1205)) <= (tk(P143)) ) & ( ( 1 ) <= (tk(P891)) ) ) & ( ( (tk(P1055)) <= ( 1 ) ) | ( (tk(P205)) <= ( 1 ) ) ) ) )) ) )) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-03 (reachable & potential((! ( ( ( (! ( (tk(P1115)) <= (tk(P1236)) )) & ( ( (! ( (tk(P1346)) <= (tk(P467)) )) | ( ( (tk(P791)) <= (tk(P309)) ) | ( (tk(P1131)) <= (tk(P758)) ) ) ) & ( ( ( ( 1 ) <= (tk(P353)) ) | ( (! ( (tk(P695)) <= ( 1 ) )) & ( ( 1 ) <= (tk(P305)) ) ) ) & ( ( ( (tk(P1011)) <= (tk(P792)) ) | ( ( (tk(P734)) <= (tk(P1353)) ) | ( ( 1 ) <= (tk(P393)) ) ) ) & ( (tk(P1187)) <= (tk(P457)) ) ) ) ) ) | (! ( (tk(P152)) <= (tk(P1049)) )) ) | (! ( ( ( (! ( (! ( (tk(P1092)) <= ( 1 ) )) & (! ( ( 1 ) <= (tk(P486)) )) )) & ( ( (! ( ( 1 ) <= (tk(P1323)) )) | ( ( (tk(P200)) <= ( 1 ) ) | ( ( 1 ) <= (tk(P69)) ) ) ) | ( ( ( (tk(P942)) <= ( 1 ) ) & ( (tk(P1132)) <= ( 0 ) ) ) | ( ( ( 1 ) <= (tk(P368)) ) & ( (tk(P74)) <= ( 1 ) ) ) ) ) ) & (! ( (tk(P1323)) <= (tk(P361)) )) ) & ( (! ( ( ( 1 ) <= (tk(P1041)) ) | (! ( (tk(P417)) <= ( 1 ) )) )) & (! ( ( (tk(P1173)) <= ( 1 ) ) | ( ( 1 ) <= (tk(P252)) ) )) ) )) ))))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-04 (reachable & potential((! ( (tk(P613)) <= ( 0 ) ))))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-05 (reachable & potential(( (! ( (! ( ( ( 1 ) <= (tk(P884)) ) | (! ( ( 1 ) <= (tk(P788)) )) )) | ( ( 1 ) <= (tk(P1339)) ) )) & ( (! ( (tk(P342)) <= ( 0 ) )) | (! ( (! ( ( ( 1 ) <= (tk(P1064)) ) & ( (tk(P64)) <= ( 0 ) ) )) | ( (tk(P986)) <= (tk(P333)) ) )) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-06 (reachable &!potential( ( (tk(P1226)) <= (tk(P547)) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-07 (reachable & potential((! ( (tk(P1261)) <= (tk(P581)) ))))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-08 (reachable &!potential( ( (! ( ( ( ( (tk(P26)) <= ( 0 ) ) & (! ( (tk(P1349)) <= (tk(P53)) )) ) | (! ( ( ( (tk(P1218)) <= (tk(P169)) ) & (! ( (tk(P655)) <= (tk(P529)) )) ) | (! ( (tk(P1009)) <= ( 1 ) )) )) ) & (! ( (! ( (tk(P939)) <= ( 0 ) )) | (! ( ( 1 ) <= (tk(P482)) )) )) )) | ( ( (! ( ( 1 ) <= (tk(P1088)) )) & ( (tk(P1355)) <= ( 1 ) ) ) | ( ( 1 ) <= (tk(P1326)) ) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-09 (reachable & potential(( ( (! ( ( (tk(P724)) <= ( 0 ) ) | (! ( ( ( (! ( (tk(P450)) <= (tk(P566)) )) & ( (tk(P641)) <= (tk(P921)) ) ) & ( ( ( ( 1 ) <= (tk(P403)) ) | ( ( 1 ) <= (tk(P422)) ) ) & (! ( (tk(P529)) <= ( 0 ) )) ) ) & ( (tk(P1285)) <= ( 1 ) ) )) )) & ( (tk(P39)) <= (tk(P218)) ) ) & ( (tk(P1148)) <= (tk(P961)) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-10 (reachable &!potential( ( ( ( 1 ) <= (tk(P475)) ) | ( (! ( (! ( ( ( (! ( ( 1 ) <= (tk(P822)) )) | ( ( (tk(P845)) <= ( 0 ) ) | ( ( 1 ) <= (tk(P1374)) ) ) ) & ( (! ( ( 1 ) <= (tk(P373)) )) & ( (tk(P1011)) <= (tk(P286)) ) ) ) & ( (! ( ( 1 ) <= (tk(P1041)) )) | (! ( ( (tk(P87)) <= ( 0 ) ) & ( (tk(P929)) <= (tk(P659)) ) )) ) )) | ( ( ( (tk(P798)) <= (tk(P791)) ) & ( ( ( ( (tk(P272)) <= ( 0 ) ) | ( ( 1 ) <= (tk(P859)) ) ) | ( ( 1 ) <= (tk(P1145)) ) ) & ( ( ( (tk(P1046)) <= (tk(P53)) ) | ( ( 1 ) <= (tk(P792)) ) ) & ( ( (tk(P559)) <= (tk(P42)) ) & ( (tk(P659)) <= ( 0 ) ) ) ) ) ) | ( ( (! ( (tk(P1165)) <= (tk(P965)) )) & ( ( 1 ) <= (tk(P998)) ) ) | ( ( ( (tk(P689)) <= ( 0 ) ) | ( ( 1 ) <= (tk(P1183)) ) ) & ( ( ( 1 ) <= (tk(P321)) ) | ( (tk(P24)) <= ( 0 ) ) ) ) ) ) )) | ( ( (tk(P721)) <= (tk(P424)) ) | ( (tk(P219)) <= ( 0 ) ) ) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-11 (reachable &!potential( ( ( ( (! ( ( ( 1 ) <= (tk(P48)) ) | (! ( ( ( (tk(P775)) <= ( 0 ) ) & ( (tk(P823)) <= (tk(P618)) ) ) & ( (tk(P136)) <= (tk(P694)) ) )) )) | (! ( ( ( ( ( ( (tk(P672)) <= ( 1 ) ) & ( ( 1 ) <= (tk(P453)) ) ) | ( (tk(P517)) <= (tk(P72)) ) ) & ( (! ( (tk(P229)) <= ( 0 ) )) & ( ( (tk(P1105)) <= ( 0 ) ) | ( ( 1 ) <= (tk(P436)) ) ) ) ) | (! ( ( (tk(P930)) <= (tk(P1110)) ) & ( (tk(P171)) <= (tk(P1214)) ) )) ) & ( (! ( ( (tk(P788)) <= (tk(P1195)) ) & ( ( ( 1 ) <= (tk(P934)) ) & ( (tk(P12)) <= (tk(P420)) ) ) )) | ( (tk(P1334)) <= (tk(P951)) ) ) )) ) | (! ( (tk(P1031)) <= (tk(P856)) )) ) & ( (tk(P643)) <= ( 0 ) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-12 (reachable &!potential( ( (tk(P645)) <= ( 1 ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-13 (reachable &!potential( ( ( ( (! ( (! ( ( 1 ) <= (tk(P908)) )) | ( ( ( ( ( ( 1 ) <= (tk(P873)) ) | ( ( 1 ) <= (tk(P242)) ) ) & ( ( ( 1 ) <= (tk(P338)) ) | ( (tk(P553)) <= ( 1 ) ) ) ) | ( ( ( (tk(P78)) <= ( 1 ) ) | ( (tk(P1054)) <= (tk(P82)) ) ) & ( ( (tk(P494)) <= ( 1 ) ) & ( ( 1 ) <= (tk(P1203)) ) ) ) ) | ( ( (! ( (tk(P1162)) <= ( 0 ) )) | (! ( ( 1 ) <= (tk(P934)) )) ) | ( (tk(P210)) <= ( 0 ) ) ) ) )) & ( ( 1 ) <= (tk(P145)) ) ) | ( ( (tk(P1167)) <= (tk(P1370)) ) & (! ( (! ( (tk(P1150)) <= ( 1 ) )) | (! ( (tk(P1126)) <= ( 1 ) )) )) ) ) | ( ( (tk(P927)) <= (tk(P988)) ) & ( (! ( ( (! ( ( 1 ) <= (tk(P401)) )) | (! ( ( (tk(P612)) <= ( 1 ) ) | ( (tk(P1103)) <= (tk(P541)) ) )) ) | ( ( (tk(P107)) <= (tk(P571)) ) & ( ( (tk(P30)) <= ( 1 ) ) & (! ( (tk(P1327)) <= ( 0 ) )) ) ) )) | ( (tk(P422)) <= (tk(P354)) ) ) ) )))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-14 (reachable & potential((! ( ( ( (! ( ( (! ( ( ( 1 ) <= (tk(P1065)) ) & ( (tk(P1296)) <= ( 1 ) ) )) & ( ( ( (tk(P766)) <= (tk(P430)) ) & ( (tk(P342)) <= (tk(P430)) ) ) | (! ( ( 1 ) <= (tk(P1229)) )) ) ) & ( (tk(P176)) <= ( 0 ) ) )) & (! ( (tk(P1225)) <= (tk(P371)) )) ) | ( ( (tk(P1153)) <= (tk(P115)) ) & ( ( ( ( (! ( (tk(P897)) <= ( 1 ) )) & ( ( (tk(P1203)) <= ( 1 ) ) | ( (tk(P401)) <= ( 0 ) ) ) ) | ( ( ( (tk(P315)) <= ( 1 ) ) & ( (tk(P288)) <= (tk(P425)) ) ) & (! ( (tk(P645)) <= ( 0 ) )) ) ) | (! ( ( 1 ) <= (tk(P456)) )) ) | ( ( ( 1 ) <= (tk(P397)) ) & (! ( ( (tk(P529)) <= (tk(P434)) ) & (! ( (tk(P461)) <= (tk(P1147)) )) )) ) ) ) ) & ( (tk(P842)) <= ( 1 ) ) ))))

PROPERTY: DLCround-PT-03b-ReachabilityCardinality-15 (reachable &!potential( (! ( ( ( (! ( (tk(P759)) <= ( 1 ) )) & ( (! ( (! ( ( 1 ) <= (tk(P450)) )) | ( ( 1 ) <= (tk(P83)) ) )) | ( (! ( ( ( (tk(P928)) <= (tk(P779)) ) | ( ( 1 ) <= (tk(P1332)) ) ) & ( (tk(P335)) <= (tk(P917)) ) )) & ( ( ( ( ( 1 ) <= (tk(P304)) ) | ( (tk(P1170)) <= (tk(P328)) ) ) & ( ( (tk(P632)) <= (tk(P584)) ) | ( ( 1 ) <= (tk(P83)) ) ) ) & (! ( ( ( 1 ) <= (tk(P426)) ) & ( (tk(P315)) <= ( 1 ) ) )) ) ) ) ) & ( ( 1 ) <= (tk(P805)) ) ) & ( (tk(P277)) <= ( 0 ) ) ))))

TIME LIMIT: Killed by timeout after 3600 seconds

MemTotal: 16393216 kB

MemFree: 10055188 kB

After kill :

MemTotal: 16393216 kB

MemFree: 16105192 kB

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ perl -pe 's/.*\.//g'

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityCardinality -timeout 360 -rebuildPNML

Caught signal 15, terminating.

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-03b"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="smartxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool smartxred"

echo " Input is DLCround-PT-03b, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r107-tall-167814484500630"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-03b.tgz

mv DLCround-PT-03b execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;