About the Execution of ITS-Tools for DLCround-PT-05b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 975.451 | 29503.00 | 41647.00 | 9162.90 | TFTFTFTFTFFTTTFF | normal |

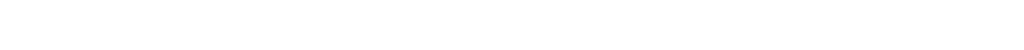

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r101-tall-167814475700662.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool itstools

Input is DLCround-PT-05b, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r101-tall-167814475700662

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.2M

-rw-r--r-- 1 mcc users 7.6K Feb 25 18:23 CTLCardinality.txt

-rw-r--r-- 1 mcc users 83K Feb 25 18:23 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.8K Feb 25 18:23 CTLFireability.txt

-rw-r--r-- 1 mcc users 53K Feb 25 18:23 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.0K Feb 25 15:52 LTLCardinality.txt

-rw-r--r-- 1 mcc users 28K Feb 25 15:52 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.2K Feb 25 15:52 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 15:52 LTLFireability.xml

-rw-r--r-- 1 mcc users 11K Feb 25 18:24 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 109K Feb 25 18:24 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 8.9K Feb 25 18:24 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 76K Feb 25 18:24 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 25 15:52 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Feb 25 15:52 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 674K Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-00

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-01

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-02

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-03

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-04

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-05

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-06

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-07

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-08

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-09

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-10

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-11

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-12

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-13

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-14

FORMULA_NAME DLCround-PT-05b-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1678304636218

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=itstools

BK_EXAMINATION=ReachabilityCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=DLCround-PT-05b

Not applying reductions.

Model is PT

ReachabilityCardinality PT

Running Version 202303021504

[2023-03-08 19:44:03] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2023-03-08 19:44:03] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-08 19:44:03] [INFO ] Load time of PNML (sax parser for PT used): 123 ms

[2023-03-08 19:44:03] [INFO ] Transformed 1999 places.

[2023-03-08 19:44:03] [INFO ] Transformed 2887 transitions.

[2023-03-08 19:44:03] [INFO ] Found NUPN structural information;

[2023-03-08 19:44:03] [INFO ] Parsed PT model containing 1999 places and 2887 transitions and 7649 arcs in 209 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 13 ms.

Working with output stream class java.io.PrintStream

FORMULA DLCround-PT-05b-ReachabilityCardinality-05 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-05b-ReachabilityCardinality-08 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA DLCround-PT-05b-ReachabilityCardinality-14 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

Incomplete random walk after 10000 steps, including 2 resets, run finished after 454 ms. (steps per millisecond=22 ) properties (out of 13) seen :8

FORMULA DLCround-PT-05b-ReachabilityCardinality-15 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-12 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-11 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-10 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-07 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-04 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-03 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-02 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

[2023-03-08 19:44:04] [INFO ] Flatten gal took : 217 ms

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 48 ms. (steps per millisecond=208 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 41 ms. (steps per millisecond=243 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 61 ms. (steps per millisecond=163 ) properties (out of 5) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 24 ms. (steps per millisecond=416 ) properties (out of 5) seen :0

[2023-03-08 19:44:04] [INFO ] Flatten gal took : 140 ms

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 19 ms. (steps per millisecond=526 ) properties (out of 5) seen :0

Running SMT prover for 5 properties.

// Phase 1: matrix 2887 rows 1999 cols

[2023-03-08 19:44:04] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality17288078779409794608.gal : 51 ms

[2023-03-08 19:44:04] [INFO ] Computed 88 place invariants in 45 ms

[2023-03-08 19:44:04] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality14383283147290045021.prop : 1 ms

Invoking ITS tools like this :cd /home/mcc/execution;'/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202303021504/bin/its-reach-linux64' '--gc-threshold' '2000000' '--quiet' '-i' '/tmp/ReachabilityCardinality17288078779409794608.gal' '-t' 'CGAL' '-reachable-file' '/tmp/ReachabilityCardinality14383283147290045021.prop' '--nowitness' '--gen-order' 'FOLLOW'

its-reach command run as :

/home/mcc/BenchKit/itstools/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202303021504/bin/its-reach-linux64 --gc-threshold 2000000 --quiet ...330

Loading property file /tmp/ReachabilityCardinality14383283147290045021.prop.

[2023-03-08 19:44:05] [INFO ] After 684ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:5

[2023-03-08 19:44:06] [INFO ] [Nat]Absence check using 88 positive place invariants in 590 ms returned sat

[2023-03-08 19:44:07] [INFO ] After 1338ms SMT Verify possible using state equation in natural domain returned unsat :1 sat :4

SDD proceeding with computation,5 properties remain. new max is 4

SDD size :1 after 5

SDD proceeding with computation,5 properties remain. new max is 8

SDD size :5 after 10

SDD proceeding with computation,5 properties remain. new max is 16

SDD size :10 after 35

SDD proceeding with computation,5 properties remain. new max is 32

SDD size :35 after 632

SDD proceeding with computation,5 properties remain. new max is 64

SDD size :632 after 5191

SDD proceeding with computation,5 properties remain. new max is 128

SDD size :5191 after 10278

SDD proceeding with computation,5 properties remain. new max is 256

SDD size :10278 after 12934

SDD proceeding with computation,5 properties remain. new max is 512

SDD size :12934 after 30830

SDD proceeding with computation,5 properties remain. new max is 1024

SDD size :30830 after 558277

SDD proceeding with computation,5 properties remain. new max is 2048

SDD size :558277 after 1.23774e+06

[2023-03-08 19:44:07] [INFO ] Deduced a trap composed of 89 places in 328 ms of which 10 ms to minimize.

SDD proceeding with computation,5 properties remain. new max is 4096

SDD size :1.23774e+06 after 2.71434e+07

[2023-03-08 19:44:08] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 541 ms

SDD proceeding with computation,5 properties remain. new max is 8192

SDD size :2.71434e+07 after 4.79306e+07

[2023-03-08 19:44:08] [INFO ] After 2741ms SMT Verify possible using trap constraints in natural domain returned unsat :1 sat :4

Attempting to minimize the solution found.

SDD proceeding with computation,5 properties remain. new max is 16384

SDD size :4.79306e+07 after 1.45121e+09

Minimization took 483 ms.

[2023-03-08 19:44:09] [INFO ] After 4375ms SMT Verify possible using all constraints in natural domain returned unsat :1 sat :4

FORMULA DLCround-PT-05b-ReachabilityCardinality-01 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 5 Parikh solutions to 4 different solutions.

FORMULA DLCround-PT-05b-ReachabilityCardinality-13 TRUE TECHNIQUES TOPOLOGICAL PARIKH_WALK

Parikh walk visited 1 properties in 113 ms.

Support contains 22 out of 1999 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1999/1999 places, 2887/2887 transitions.

Graph (trivial) has 1871 edges and 1999 vertex of which 365 / 1999 are part of one of the 28 SCC in 12 ms

Free SCC test removed 337 places

Drop transitions removed 378 transitions

Reduce isomorphic transitions removed 378 transitions.

Drop transitions removed 757 transitions

Trivial Post-agglo rules discarded 757 transitions

Performed 757 trivial Post agglomeration. Transition count delta: 757

Iterating post reduction 0 with 757 rules applied. Total rules applied 758 place count 1662 transition count 1752

Reduce places removed 757 places and 0 transitions.

Ensure Unique test removed 29 transitions

Reduce isomorphic transitions removed 29 transitions.

Drop transitions removed 23 transitions

Trivial Post-agglo rules discarded 23 transitions

Performed 23 trivial Post agglomeration. Transition count delta: 23

Iterating post reduction 1 with 809 rules applied. Total rules applied 1567 place count 905 transition count 1700

Reduce places removed 23 places and 0 transitions.

Ensure Unique test removed 3 transitions

Reduce isomorphic transitions removed 3 transitions.

Drop transitions removed 3 transitions

Trivial Post-agglo rules discarded 3 transitions

Performed 3 trivial Post agglomeration. Transition count delta: 3

Iterating post reduction 2 with 29 rules applied. Total rules applied 1596 place count 882 transition count 1694

Reduce places removed 3 places and 0 transitions.

Performed 14 Post agglomeration using F-continuation condition.Transition count delta: 14

Iterating post reduction 3 with 17 rules applied. Total rules applied 1613 place count 879 transition count 1680

Reduce places removed 14 places and 0 transitions.

Iterating post reduction 4 with 14 rules applied. Total rules applied 1627 place count 865 transition count 1680

Performed 9 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 9 Pre rules applied. Total rules applied 1627 place count 865 transition count 1671

Deduced a syphon composed of 9 places in 3 ms

Reduce places removed 9 places and 0 transitions.

Iterating global reduction 5 with 18 rules applied. Total rules applied 1645 place count 856 transition count 1671

Discarding 221 places :

Symmetric choice reduction at 5 with 221 rule applications. Total rules 1866 place count 635 transition count 1450

Iterating global reduction 5 with 221 rules applied. Total rules applied 2087 place count 635 transition count 1450

Performed 87 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 87 Pre rules applied. Total rules applied 2087 place count 635 transition count 1363

Deduced a syphon composed of 87 places in 9 ms

Reduce places removed 87 places and 0 transitions.

Iterating global reduction 5 with 174 rules applied. Total rules applied 2261 place count 548 transition count 1363

Discarding 43 places :

Symmetric choice reduction at 5 with 43 rule applications. Total rules 2304 place count 505 transition count 997

Iterating global reduction 5 with 43 rules applied. Total rules applied 2347 place count 505 transition count 997

Ensure Unique test removed 16 transitions

Reduce isomorphic transitions removed 16 transitions.

Iterating post reduction 5 with 16 rules applied. Total rules applied 2363 place count 505 transition count 981

Performed 136 Post agglomeration using F-continuation condition with reduction of 6 identical transitions.

Deduced a syphon composed of 136 places in 0 ms

Reduce places removed 136 places and 0 transitions.

Iterating global reduction 6 with 272 rules applied. Total rules applied 2635 place count 369 transition count 839

Ensure Unique test removed 5 transitions

Reduce isomorphic transitions removed 5 transitions.

Iterating post reduction 6 with 5 rules applied. Total rules applied 2640 place count 369 transition count 834

Discarding 3 places :

Symmetric choice reduction at 7 with 3 rule applications. Total rules 2643 place count 366 transition count 807

Iterating global reduction 7 with 3 rules applied. Total rules applied 2646 place count 366 transition count 807

Performed 46 Post agglomeration using F-continuation condition with reduction of 24 identical transitions.

Deduced a syphon composed of 46 places in 0 ms

Reduce places removed 46 places and 0 transitions.

Iterating global reduction 7 with 92 rules applied. Total rules applied 2738 place count 320 transition count 1145

Drop transitions removed 47 transitions

Reduce isomorphic transitions removed 47 transitions.

Iterating post reduction 7 with 47 rules applied. Total rules applied 2785 place count 320 transition count 1098

Discarding 15 places :

Symmetric choice reduction at 8 with 15 rule applications. Total rules 2800 place count 305 transition count 832

Iterating global reduction 8 with 15 rules applied. Total rules applied 2815 place count 305 transition count 832

Ensure Unique test removed 34 transitions

Reduce isomorphic transitions removed 34 transitions.

Iterating post reduction 8 with 34 rules applied. Total rules applied 2849 place count 305 transition count 798

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -11

Deduced a syphon composed of 1 places in 1 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 9 with 2 rules applied. Total rules applied 2851 place count 304 transition count 809

Drop transitions removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 9 with 2 rules applied. Total rules applied 2853 place count 304 transition count 807

Drop transitions removed 94 transitions

Redundant transition composition rules discarded 94 transitions

Iterating global reduction 10 with 94 rules applied. Total rules applied 2947 place count 304 transition count 713

Discarding 6 places :

Symmetric choice reduction at 10 with 6 rule applications. Total rules 2953 place count 298 transition count 650

Iterating global reduction 10 with 6 rules applied. Total rules applied 2959 place count 298 transition count 650

Ensure Unique test removed 5 transitions

Reduce isomorphic transitions removed 5 transitions.

Iterating post reduction 10 with 5 rules applied. Total rules applied 2964 place count 298 transition count 645

Drop transitions removed 1 transitions

Redundant transition composition rules discarded 1 transitions

Iterating global reduction 11 with 1 rules applied. Total rules applied 2965 place count 298 transition count 644

SDD proceeding with computation,5 properties remain. new max is 32768

Free-agglomeration rule applied 151 times with reduction of 67 identical transitions.

Iterating global reduction 11 with 151 rules applied. Total rules applied 3116 place count 298 transition count 426

Reduce places removed 151 places and 0 transitions.

Drop transitions removed 157 transitions

Ensure Unique test removed 3 transitions

Reduce isomorphic transitions removed 160 transitions.

Graph (complete) has 365 edges and 147 vertex of which 132 are kept as prefixes of interest. Removing 15 places using SCC suffix rule.1 ms

Discarding 15 places :

Also discarding 0 output transitions

Iterating post reduction 11 with 312 rules applied. Total rules applied 3428 place count 132 transition count 266

Drop transitions removed 8 transitions

Ensure Unique test removed 15 transitions

Reduce isomorphic transitions removed 23 transitions.

Iterating post reduction 12 with 23 rules applied. Total rules applied 3451 place count 132 transition count 243

Discarding 16 places :

Symmetric choice reduction at 13 with 16 rule applications. Total rules 3467 place count 116 transition count 222

Iterating global reduction 13 with 16 rules applied. Total rules applied 3483 place count 116 transition count 222

SDD size :1.45121e+09 after 9.12611e+09

Drop transitions removed 18 transitions

Redundant transition composition rules discarded 18 transitions

Iterating global reduction 13 with 18 rules applied. Total rules applied 3501 place count 116 transition count 204

Reduce places removed 1 places and 0 transitions.

Graph (complete) has 290 edges and 115 vertex of which 113 are kept as prefixes of interest. Removing 2 places using SCC suffix rule.0 ms

Discarding 2 places :

Also discarding 0 output transitions

Iterating post reduction 13 with 2 rules applied. Total rules applied 3503 place count 113 transition count 204

Drop transitions removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 14 with 2 rules applied. Total rules applied 3505 place count 113 transition count 202

Discarding 6 places :

Symmetric choice reduction at 15 with 6 rule applications. Total rules 3511 place count 107 transition count 195

Iterating global reduction 15 with 6 rules applied. Total rules applied 3517 place count 107 transition count 195

Partial Free-agglomeration rule applied 1 times.

Drop transitions removed 1 transitions

Iterating global reduction 15 with 1 rules applied. Total rules applied 3518 place count 107 transition count 195

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 15 with 1 rules applied. Total rules applied 3519 place count 106 transition count 194

Applied a total of 3519 rules in 787 ms. Remains 106 /1999 variables (removed 1893) and now considering 194/2887 (removed 2693) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 788 ms. Remains : 106/1999 places, 194/2887 transitions.

Finished random walk after 242 steps, including 0 resets, run visited all 3 properties in 22 ms. (steps per millisecond=11 )

FORMULA DLCround-PT-05b-ReachabilityCardinality-09 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-06 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCround-PT-05b-ReachabilityCardinality-00 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

ITS runner failed with exception null

java.lang.InterruptedException

at java.base/java.lang.Object.wait(Native Method)

at java.base/java.lang.Thread.join(Thread.java:1304)

at java.base/java.lang.Thread.join(Thread.java:1372)

at fr.lip6.move.gal.application.runner.AbstractRunner.join(AbstractRunner.java:27)

at fr.lip6.move.gal.application.runner.its.ITSRunner.join(ITSRunner.java:177)

at fr.lip6.move.gal.application.solver.global.GlobalPropertySolver.verifyWithSDD(GlobalPropertySolver.java:675)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.lambda$2(ReachabilitySolver.java:63)

at java.base/java.lang.Thread.run(Thread.java:833)

All properties solved without resorting to model-checking.

Total runtime 7123 ms.

SDD proceeding with computation,5 properties remain. new max is 65536

SDD size :9.12611e+09 after 3.2004e+11

BK_STOP 1678304665721

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../itstools/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit/bin//../itstools/bin//..//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ perl -pe 's/.*\.//g'

++ sed s/.jar//

++ ls /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../itstools/bin//..//itstools/its-tools -pnfolder /home/mcc/execution -examination ReachabilityCardinality -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//../itstools/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-05b"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool itstools"

echo " Input is DLCround-PT-05b, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r101-tall-167814475700662"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-05b.tgz

mv DLCround-PT-05b execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;