About the Execution of LoLa+red for SieveSingleMsgMbox-PT-d0m18

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 837.735 | 27978.00 | 36984.00 | 69.60 | FFTTTT?TTFFFFFTF | normal |

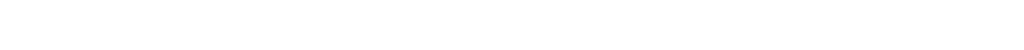

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2023-input.r423-tajo-167905976600370.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2023-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

.....................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lolaxred

Input is SieveSingleMsgMbox-PT-d0m18, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r423-tajo-167905976600370

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 448K

-rw-r--r-- 1 mcc users 5.8K Feb 26 10:27 CTLCardinality.txt

-rw-r--r-- 1 mcc users 56K Feb 26 10:27 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.0K Feb 26 10:26 CTLFireability.txt

-rw-r--r-- 1 mcc users 42K Feb 26 10:26 CTLFireability.xml

-rw-r--r-- 1 mcc users 3.4K Feb 25 17:05 LTLCardinality.txt

-rw-r--r-- 1 mcc users 21K Feb 25 17:05 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.3K Feb 25 17:05 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 17:05 LTLFireability.xml

-rw-r--r-- 1 mcc users 12K Feb 26 10:28 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 127K Feb 26 10:28 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 6.3K Feb 26 10:27 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 49K Feb 26 10:27 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K Feb 25 17:05 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K Feb 25 17:05 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 equiv_col

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 iscolored

-rw-r--r-- 1 mcc users 57K Mar 5 18:23 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-00

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-01

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-02

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-03

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-04

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-05

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-06

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-07

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-08

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-09

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-10

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-11

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-12

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-13

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-14

FORMULA_NAME SieveSingleMsgMbox-PT-d0m18-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1679246704140

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lolaxred

BK_EXAMINATION=CTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=SieveSingleMsgMbox-PT-d0m18

Applying reductions before tool lola

Invoking reducer

Running Version 202303021504

[2023-03-19 17:25:06] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -timeout, 360, -rebuildPNML]

[2023-03-19 17:25:06] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-19 17:25:06] [INFO ] Load time of PNML (sax parser for PT used): 51 ms

[2023-03-19 17:25:06] [INFO ] Transformed 262 places.

[2023-03-19 17:25:06] [INFO ] Transformed 73 transitions.

[2023-03-19 17:25:06] [INFO ] Parsed PT model containing 262 places and 73 transitions and 292 arcs in 118 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 10 ms.

Deduced a syphon composed of 190 places in 1 ms

Reduce places removed 190 places and 0 transitions.

Support contains 58 out of 72 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 72/72 places, 73/73 transitions.

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 0 with 2 rules applied. Total rules applied 2 place count 70 transition count 73

Applied a total of 2 rules in 12 ms. Remains 70 /72 variables (removed 2) and now considering 73/73 (removed 0) transitions.

// Phase 1: matrix 73 rows 70 cols

[2023-03-19 17:25:06] [INFO ] Computed 5 place invariants in 14 ms

[2023-03-19 17:25:06] [INFO ] Implicit Places using invariants in 183 ms returned []

[2023-03-19 17:25:06] [INFO ] Invariant cache hit.

[2023-03-19 17:25:06] [INFO ] State equation strengthened by 31 read => feed constraints.

[2023-03-19 17:25:06] [INFO ] Implicit Places using invariants and state equation in 143 ms returned []

Implicit Place search using SMT with State Equation took 370 ms to find 0 implicit places.

[2023-03-19 17:25:06] [INFO ] Invariant cache hit.

[2023-03-19 17:25:07] [INFO ] Dead Transitions using invariants and state equation in 62 ms found 0 transitions.

Starting structural reductions in LTL mode, iteration 1 : 70/72 places, 73/73 transitions.

Finished structural reductions in LTL mode , in 1 iterations and 446 ms. Remains : 70/72 places, 73/73 transitions.

Support contains 58 out of 70 places after structural reductions.

[2023-03-19 17:25:07] [INFO ] Flatten gal took : 35 ms

[2023-03-19 17:25:07] [INFO ] Flatten gal took : 18 ms

[2023-03-19 17:25:07] [INFO ] Input system was already deterministic with 73 transitions.

Incomplete random walk after 10000 steps, including 2222 resets, run finished after 402 ms. (steps per millisecond=24 ) properties (out of 56) seen :22

Incomplete Best-First random walk after 1001 steps, including 43 resets, run finished after 11 ms. (steps per millisecond=91 ) properties (out of 34) seen :2

Incomplete Best-First random walk after 1001 steps, including 46 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 54 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 48 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 38 resets, run finished after 50 ms. (steps per millisecond=20 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 50 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 48 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 105 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 51 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 43 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 112 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 45 resets, run finished after 7 ms. (steps per millisecond=142 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 111 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 99 resets, run finished after 9 ms. (steps per millisecond=111 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 47 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 46 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 47 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 44 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 51 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 105 resets, run finished after 8 ms. (steps per millisecond=125 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 200 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1001 steps, including 58 resets, run finished after 7 ms. (steps per millisecond=143 ) properties (out of 32) seen :0

Incomplete Best-First random walk after 1000 steps, including 46 resets, run finished after 9 ms. (steps per millisecond=111 ) properties (out of 32) seen :1

Incomplete Best-First random walk after 1001 steps, including 112 resets, run finished after 13 ms. (steps per millisecond=77 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1001 steps, including 79 resets, run finished after 22 ms. (steps per millisecond=45 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1001 steps, including 47 resets, run finished after 11 ms. (steps per millisecond=91 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1000 steps, including 111 resets, run finished after 12 ms. (steps per millisecond=83 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1001 steps, including 38 resets, run finished after 31 ms. (steps per millisecond=32 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1000 steps, including 51 resets, run finished after 37 ms. (steps per millisecond=27 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1000 steps, including 108 resets, run finished after 39 ms. (steps per millisecond=25 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1000 steps, including 47 resets, run finished after 31 ms. (steps per millisecond=32 ) properties (out of 31) seen :0

Incomplete Best-First random walk after 1000 steps, including 39 resets, run finished after 13 ms. (steps per millisecond=76 ) properties (out of 31) seen :0

Running SMT prover for 31 properties.

[2023-03-19 17:25:08] [INFO ] Invariant cache hit.

[2023-03-19 17:25:08] [INFO ] [Real]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-03-19 17:25:08] [INFO ] [Real]Absence check using 2 positive and 3 generalized place invariants in 2 ms returned sat

[2023-03-19 17:25:08] [INFO ] After 57ms SMT Verify possible using state equation in real domain returned unsat :3 sat :2 real:26

[2023-03-19 17:25:08] [INFO ] State equation strengthened by 31 read => feed constraints.

[2023-03-19 17:25:08] [INFO ] After 17ms SMT Verify possible using 31 Read/Feed constraints in real domain returned unsat :3 sat :0 real:28

[2023-03-19 17:25:08] [INFO ] After 279ms SMT Verify possible using all constraints in real domain returned unsat :3 sat :0 real:28

[2023-03-19 17:25:08] [INFO ] [Nat]Absence check using 2 positive place invariants in 1 ms returned sat

[2023-03-19 17:25:08] [INFO ] [Nat]Absence check using 2 positive and 3 generalized place invariants in 1 ms returned sat

[2023-03-19 17:25:08] [INFO ] After 182ms SMT Verify possible using state equation in natural domain returned unsat :5 sat :26

[2023-03-19 17:25:09] [INFO ] After 283ms SMT Verify possible using 31 Read/Feed constraints in natural domain returned unsat :5 sat :26

[2023-03-19 17:25:09] [INFO ] Deduced a trap composed of 28 places in 38 ms of which 4 ms to minimize.

[2023-03-19 17:25:09] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 46 ms

[2023-03-19 17:25:09] [INFO ] After 588ms SMT Verify possible using trap constraints in natural domain returned unsat :5 sat :26

Attempting to minimize the solution found.

Minimization took 173 ms.

[2023-03-19 17:25:09] [INFO ] After 1090ms SMT Verify possible using all constraints in natural domain returned unsat :5 sat :26

Fused 31 Parikh solutions to 26 different solutions.

Parikh walk visited 5 properties in 290 ms.

Support contains 26 out of 70 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 4 places :

Symmetric choice reduction at 0 with 4 rule applications. Total rules 4 place count 66 transition count 69

Iterating global reduction 0 with 4 rules applied. Total rules applied 8 place count 66 transition count 69

Applied a total of 8 rules in 22 ms. Remains 66 /70 variables (removed 4) and now considering 69/73 (removed 4) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 22 ms. Remains : 66/70 places, 69/73 transitions.

Incomplete random walk after 10000 steps, including 2248 resets, run finished after 345 ms. (steps per millisecond=28 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 59 resets, run finished after 27 ms. (steps per millisecond=37 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 49 resets, run finished after 14 ms. (steps per millisecond=71 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 56 resets, run finished after 17 ms. (steps per millisecond=58 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 41 resets, run finished after 11 ms. (steps per millisecond=90 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 118 resets, run finished after 19 ms. (steps per millisecond=52 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 44 resets, run finished after 10 ms. (steps per millisecond=100 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 48 resets, run finished after 15 ms. (steps per millisecond=66 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 94 resets, run finished after 16 ms. (steps per millisecond=62 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 122 resets, run finished after 28 ms. (steps per millisecond=35 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 98 resets, run finished after 28 ms. (steps per millisecond=35 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 44 resets, run finished after 8 ms. (steps per millisecond=125 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 50 resets, run finished after 8 ms. (steps per millisecond=125 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 48 resets, run finished after 24 ms. (steps per millisecond=41 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 200 resets, run finished after 32 ms. (steps per millisecond=31 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 98 resets, run finished after 27 ms. (steps per millisecond=37 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 105 resets, run finished after 9 ms. (steps per millisecond=111 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1000 steps, including 107 resets, run finished after 22 ms. (steps per millisecond=45 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 45 resets, run finished after 28 ms. (steps per millisecond=35 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 108 resets, run finished after 10 ms. (steps per millisecond=100 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 45 resets, run finished after 10 ms. (steps per millisecond=100 ) properties (out of 21) seen :0

Incomplete Best-First random walk after 1001 steps, including 46 resets, run finished after 17 ms. (steps per millisecond=58 ) properties (out of 21) seen :0

Finished probabilistic random walk after 78824 steps, run visited all 21 properties in 540 ms. (steps per millisecond=145 )

Probabilistic random walk after 78824 steps, saw 41997 distinct states, run finished after 552 ms. (steps per millisecond=142 ) properties seen :21

Successfully simplified 5 atomic propositions for a total of 16 simplifications.

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-03 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-10 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-14 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-03-19 17:25:11] [INFO ] Initial state reduction rules for CTL removed 1 formulas.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 7 ms

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-01 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 7 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 73 transitions.

Computed a total of 10 stabilizing places and 13 stable transitions

Graph (complete) has 213 edges and 70 vertex of which 69 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.2 ms

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 6 places :

Symmetric choice reduction at 0 with 6 rule applications. Total rules 6 place count 64 transition count 67

Iterating global reduction 0 with 6 rules applied. Total rules applied 12 place count 64 transition count 67

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 13 place count 63 transition count 66

Iterating global reduction 0 with 1 rules applied. Total rules applied 14 place count 63 transition count 66

Applied a total of 14 rules in 4 ms. Remains 63 /70 variables (removed 7) and now considering 66/73 (removed 7) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 4 ms. Remains : 63/70 places, 66/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 4 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 4 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 66 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 9 places :

Symmetric choice reduction at 0 with 9 rule applications. Total rules 9 place count 61 transition count 64

Iterating global reduction 0 with 9 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 21 place count 59 transition count 62

Iterating global reduction 0 with 1 rules applied. Total rules applied 22 place count 59 transition count 62

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 23 place count 59 transition count 61

Applied a total of 23 rules in 11 ms. Remains 59 /70 variables (removed 11) and now considering 61/73 (removed 12) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 11 ms. Remains : 59/70 places, 61/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 61 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 8 places :

Symmetric choice reduction at 0 with 8 rule applications. Total rules 8 place count 62 transition count 65

Iterating global reduction 0 with 8 rules applied. Total rules applied 16 place count 62 transition count 65

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 17 place count 61 transition count 64

Iterating global reduction 0 with 1 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 21 place count 60 transition count 62

Applied a total of 21 rules in 5 ms. Remains 60 /70 variables (removed 10) and now considering 62/73 (removed 11) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 5 ms. Remains : 60/70 places, 62/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 2 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 62 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 8 places :

Symmetric choice reduction at 0 with 8 rule applications. Total rules 8 place count 62 transition count 65

Iterating global reduction 0 with 8 rules applied. Total rules applied 16 place count 62 transition count 65

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 17 place count 61 transition count 64

Iterating global reduction 0 with 1 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 21 place count 60 transition count 62

Applied a total of 21 rules in 9 ms. Remains 60 /70 variables (removed 10) and now considering 62/73 (removed 11) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 9 ms. Remains : 60/70 places, 62/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 4 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 62 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 8 places :

Symmetric choice reduction at 0 with 8 rule applications. Total rules 8 place count 62 transition count 65

Iterating global reduction 0 with 8 rules applied. Total rules applied 16 place count 62 transition count 65

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 17 place count 61 transition count 64

Iterating global reduction 0 with 1 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 21 place count 60 transition count 62

Applied a total of 21 rules in 8 ms. Remains 60 /70 variables (removed 10) and now considering 62/73 (removed 11) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 8 ms. Remains : 60/70 places, 62/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 2 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 2 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 62 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 8 places :

Symmetric choice reduction at 0 with 8 rule applications. Total rules 8 place count 62 transition count 65

Iterating global reduction 0 with 8 rules applied. Total rules applied 16 place count 62 transition count 65

Applied a total of 16 rules in 5 ms. Remains 62 /70 variables (removed 8) and now considering 65/73 (removed 8) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 5 ms. Remains : 62/70 places, 65/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 65 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 7 places :

Symmetric choice reduction at 0 with 7 rule applications. Total rules 7 place count 63 transition count 66

Iterating global reduction 0 with 7 rules applied. Total rules applied 14 place count 63 transition count 66

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 15 place count 62 transition count 65

Iterating global reduction 0 with 1 rules applied. Total rules applied 16 place count 62 transition count 65

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 17 place count 61 transition count 64

Iterating global reduction 0 with 1 rules applied. Total rules applied 18 place count 61 transition count 64

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 19 place count 61 transition count 63

Applied a total of 19 rules in 20 ms. Remains 61 /70 variables (removed 9) and now considering 63/73 (removed 10) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 20 ms. Remains : 61/70 places, 63/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 4 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 63 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 9 places :

Symmetric choice reduction at 0 with 9 rule applications. Total rules 9 place count 61 transition count 64

Iterating global reduction 0 with 9 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 21 place count 59 transition count 62

Iterating global reduction 0 with 1 rules applied. Total rules applied 22 place count 59 transition count 62

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 23 place count 59 transition count 61

Applied a total of 23 rules in 3 ms. Remains 59 /70 variables (removed 11) and now considering 61/73 (removed 12) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 3 ms. Remains : 59/70 places, 61/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 61 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 6 places :

Symmetric choice reduction at 0 with 6 rule applications. Total rules 6 place count 64 transition count 67

Iterating global reduction 0 with 6 rules applied. Total rules applied 12 place count 64 transition count 67

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 13 place count 63 transition count 66

Iterating global reduction 0 with 1 rules applied. Total rules applied 14 place count 63 transition count 66

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 15 place count 62 transition count 65

Iterating global reduction 0 with 1 rules applied. Total rules applied 16 place count 62 transition count 65

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 17 place count 62 transition count 64

Applied a total of 17 rules in 2 ms. Remains 62 /70 variables (removed 8) and now considering 64/73 (removed 9) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 2 ms. Remains : 62/70 places, 64/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 64 transitions.

Starting structural reductions in SI_CTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 5 places :

Symmetric choice reduction at 0 with 5 rule applications. Total rules 5 place count 65 transition count 68

Iterating global reduction 0 with 5 rules applied. Total rules applied 10 place count 65 transition count 68

Applied a total of 10 rules in 4 ms. Remains 65 /70 variables (removed 5) and now considering 68/73 (removed 5) transitions.

Finished structural reductions in SI_CTL mode , in 1 iterations and 4 ms. Remains : 65/70 places, 68/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 68 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 9 places :

Symmetric choice reduction at 0 with 9 rule applications. Total rules 9 place count 61 transition count 64

Iterating global reduction 0 with 9 rules applied. Total rules applied 18 place count 61 transition count 64

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 19 place count 60 transition count 63

Iterating global reduction 0 with 1 rules applied. Total rules applied 20 place count 60 transition count 63

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 21 place count 59 transition count 62

Iterating global reduction 0 with 1 rules applied. Total rules applied 22 place count 59 transition count 62

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 23 place count 59 transition count 61

Applied a total of 23 rules in 2 ms. Remains 59 /70 variables (removed 11) and now considering 61/73 (removed 12) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 2 ms. Remains : 59/70 places, 61/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 2 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 61 transitions.

Starting structural reductions in LTL mode, iteration 0 : 70/70 places, 73/73 transitions.

Discarding 7 places :

Symmetric choice reduction at 0 with 7 rule applications. Total rules 7 place count 63 transition count 66

Iterating global reduction 0 with 7 rules applied. Total rules applied 14 place count 63 transition count 66

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 15 place count 62 transition count 65

Iterating global reduction 0 with 1 rules applied. Total rules applied 16 place count 62 transition count 65

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 17 place count 61 transition count 64

Iterating global reduction 0 with 1 rules applied. Total rules applied 18 place count 61 transition count 64

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 19 place count 61 transition count 63

Applied a total of 19 rules in 2 ms. Remains 61 /70 variables (removed 9) and now considering 63/73 (removed 10) transitions.

Finished structural reductions in LTL mode , in 1 iterations and 2 ms. Remains : 61/70 places, 63/73 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 2 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 3 ms

[2023-03-19 17:25:11] [INFO ] Input system was already deterministic with 63 transitions.

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 4 ms

[2023-03-19 17:25:11] [INFO ] Flatten gal took : 5 ms

[2023-03-19 17:25:11] [INFO ] Export to MCC of 12 properties in file /home/mcc/execution/CTLFireability.sr.xml took 2 ms.

[2023-03-19 17:25:11] [INFO ] Export to PNML in file /home/mcc/execution/model.sr.pnml of net with 70 places, 73 transitions and 289 arcs took 1 ms.

Total runtime 5163 ms.

There are residual formulas that ITS could not solve within timeout

starting LoLA

BK_INPUT SieveSingleMsgMbox-PT-d0m18

BK_EXAMINATION: CTLFireability

bin directory: /home/mcc/BenchKit/bin//../reducer/bin//../../lola/bin/

current directory: /home/mcc/execution/373

CTLFireability

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-00 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-05 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-04 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-13 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-11 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-09 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-08 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-12 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-07 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SieveSingleMsgMbox-PT-d0m18-CTLFireability-02 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

BK_STOP 1679246732118

--------------------

content from stderr:

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ export PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ PYTHONPATH=/home/mcc/BenchKit/itstools/pylibs

+ export LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

+ LD_LIBRARY_PATH=/home/mcc/BenchKit/itstools/pylibs:

++ sed s/.jar//

++ ls /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202303021504.jar

++ perl -pe 's/.*\.//g'

+ VERSION=202303021504

+ echo 'Running Version 202303021504'

+ /home/mcc/BenchKit/bin//../reducer/bin//../../itstools//itstools/its-tools -pnfolder /home/mcc/execution -examination CTLFireability -timeout 360 -rebuildPNML

lola: MEM LIMIT 32

lola: MEM LIMIT 5

lola: NET

lola: input: PNML file (--pnmlnet)

lola: reading net from /home/mcc/execution/373/model.pnml

lola: reading pnml

lola: PNML file contains place/transition net

lola: finished parsing

lola: closed net file /home/mcc/execution/373/model.pnml

lola: Reading formula.

lola: Using XML format (--xmlformula)

lola: reading XML formula

lola: reading formula from /home/mcc/execution/373/CTLFireability.xml

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: RELEASE

lola: RELEASE

lola: RELEASE

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:544

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:544

lola: RELEASE

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:547

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Rule S: 0 transitions removed,0 places removed

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: LAUNCH task # 1 (type EXCL) for 0 SieveSingleMsgMbox-PT-d0m18-CTLFireability-00

lola: time limit : 276 sec

lola: memory limit: 32 pages

lola: FINISHED task # 1 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-00

lola: result : false

lola: markings : 41

lola: fired transitions : 90

lola: time used : 0.000000

lola: memory pages used : 1

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: LAUNCH task # 10 (type EXCL) for 9 SieveSingleMsgMbox-PT-d0m18-CTLFireability-05

lola: time limit : 299 sec

lola: memory limit: 32 pages

lola: FINISHED task # 10 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-05

lola: result : true

lola: markings : 30

lola: fired transitions : 100

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 7 (type EXCL) for 6 SieveSingleMsgMbox-PT-d0m18-CTLFireability-04

lola: time limit : 327 sec

lola: memory limit: 32 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:749

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: FINISHED task # 7 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-04

lola: result : true

lola: markings : 78476

lola: fired transitions : 327107

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 38 (type EXCL) for 37 SieveSingleMsgMbox-PT-d0m18-CTLFireability-15

lola: time limit : 359 sec

lola: memory limit: 32 pages

lola: FINISHED task # 38 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-15

lola: result : false

lola: markings : 105

lola: fired transitions : 129

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 35 (type EXCL) for 34 SieveSingleMsgMbox-PT-d0m18-CTLFireability-13

lola: time limit : 399 sec

lola: memory limit: 32 pages

lola: FINISHED task # 35 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-13

lola: result : false

lola: markings : 7

lola: fired transitions : 12

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 25 (type EXCL) for 24 SieveSingleMsgMbox-PT-d0m18-CTLFireability-11

lola: time limit : 449 sec

lola: memory limit: 32 pages

lola: FINISHED task # 25 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-11

lola: result : false

lola: markings : 12

lola: fired transitions : 67

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 22 (type EXCL) for 21 SieveSingleMsgMbox-PT-d0m18-CTLFireability-09

lola: time limit : 514 sec

lola: memory limit: 32 pages

lola: FINISHED task # 22 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-09

lola: result : false

lola: markings : 393

lola: fired transitions : 456

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 19 (type EXCL) for 18 SieveSingleMsgMbox-PT-d0m18-CTLFireability-08

lola: time limit : 599 sec

lola: memory limit: 32 pages

lola: FINISHED task # 19 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-08

lola: result : true

lola: markings : 12

lola: fired transitions : 12

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 40 (type EXCL) for 27 SieveSingleMsgMbox-PT-d0m18-CTLFireability-12

lola: time limit : 719 sec

lola: memory limit: 32 pages

lola: FINISHED task # 40 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-12

lola: result : true

lola: markings : 12

lola: fired transitions : 11

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 16 (type EXCL) for 15 SieveSingleMsgMbox-PT-d0m18-CTLFireability-07

lola: time limit : 1199 sec

lola: memory limit: 32 pages

lola: FINISHED task # 16 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-07

lola: result : true

lola: markings : 12

lola: fired transitions : 24

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 4 (type EXCL) for 3 SieveSingleMsgMbox-PT-d0m18-CTLFireability-02

lola: time limit : 1799 sec

lola: memory limit: 32 pages

lola: FINISHED task # 4 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-02

lola: result : true

lola: markings : 653

lola: fired transitions : 1220

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 13 (type EXCL) for 12 SieveSingleMsgMbox-PT-d0m18-CTLFireability-06

lola: time limit : 3599 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SieveSingleMsgMbox-PT-d0m18-CTLFireability-00: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-02: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-04: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-05: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-07: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-08: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-09: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-11: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-12: CONJ false state space / EG

SieveSingleMsgMbox-PT-d0m18-CTLFireability-13: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-15: CTL false CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SieveSingleMsgMbox-PT-d0m18-CTLFireability-06: CTL 0 0 1 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

13 CTL EXCL 5/3599 10/32 SieveSingleMsgMbox-PT-d0m18-CTLFireability-06 2154754 m, 430950 m/sec, 3437771 t fired, .

Time elapsed: 6 secs. Pages in use: 10

# running tasks: 1 of 4 Visible: 12

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SieveSingleMsgMbox-PT-d0m18-CTLFireability-00: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-02: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-04: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-05: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-07: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-08: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-09: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-11: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-12: CONJ false state space / EG

SieveSingleMsgMbox-PT-d0m18-CTLFireability-13: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-15: CTL false CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SieveSingleMsgMbox-PT-d0m18-CTLFireability-06: CTL 0 0 1 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

13 CTL EXCL 10/3599 19/32 SieveSingleMsgMbox-PT-d0m18-CTLFireability-06 4444448 m, 457938 m/sec, 7441635 t fired, .

Time elapsed: 11 secs. Pages in use: 19

# running tasks: 1 of 4 Visible: 12

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SieveSingleMsgMbox-PT-d0m18-CTLFireability-00: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-02: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-04: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-05: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-07: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-08: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-09: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-11: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-12: CONJ false state space / EG

SieveSingleMsgMbox-PT-d0m18-CTLFireability-13: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-15: CTL false CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SieveSingleMsgMbox-PT-d0m18-CTLFireability-06: CTL 0 0 1 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

13 CTL EXCL 15/3599 28/32 SieveSingleMsgMbox-PT-d0m18-CTLFireability-06 6479797 m, 407069 m/sec, 11192823 t fired, .

Time elapsed: 16 secs. Pages in use: 28

# running tasks: 1 of 4 Visible: 12

lola: CANCELED task # 13 (type EXCL) for SieveSingleMsgMbox-PT-d0m18-CTLFireability-06 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SieveSingleMsgMbox-PT-d0m18-CTLFireability-00: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-02: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-04: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-05: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-07: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-08: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-09: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-11: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-12: CONJ false state space / EG

SieveSingleMsgMbox-PT-d0m18-CTLFireability-13: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-15: CTL false CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SieveSingleMsgMbox-PT-d0m18-CTLFireability-06: CTL 0 0 0 0 1 0 1 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 21 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 12

lola: Portfolio finished: no open tasks 12

FINAL RESULTS

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SieveSingleMsgMbox-PT-d0m18-CTLFireability-00: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-02: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-04: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-05: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-06: CTL unknown AGGR

SieveSingleMsgMbox-PT-d0m18-CTLFireability-07: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-08: CTL true CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-09: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-11: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-12: CONJ false state space / EG

SieveSingleMsgMbox-PT-d0m18-CTLFireability-13: CTL false CTL model checker

SieveSingleMsgMbox-PT-d0m18-CTLFireability-15: CTL false CTL model checker

Time elapsed: 21 secs. Pages in use: 32

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="SieveSingleMsgMbox-PT-d0m18"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="lolaxred"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool lolaxred"

echo " Input is SieveSingleMsgMbox-PT-d0m18, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r423-tajo-167905976600370"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/SieveSingleMsgMbox-PT-d0m18.tgz

mv SieveSingleMsgMbox-PT-d0m18 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;