About the Execution of Marcie for ServersAndClients-PT-100020

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 6430.771 | 3600000.00 | 3600071.00 | 10.10 | ????T?F???????F? | normal |

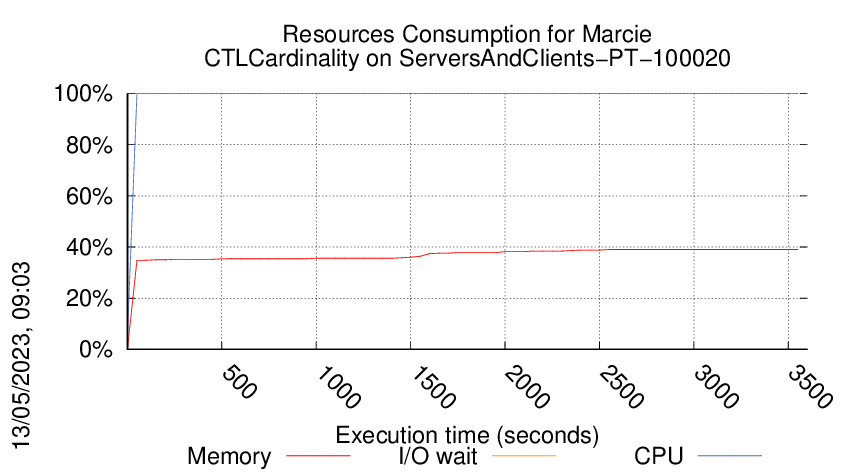

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r353-smll-167891801100457.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.....................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool marcie

Input is ServersAndClients-PT-100020, examination is CTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 1

Run identifier is r353-smll-167891801100457

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 4.7M

-rw-r--r-- 1 mcc users 11K Feb 26 03:28 CTLCardinality.txt

-rw-r--r-- 1 mcc users 114K Feb 26 03:28 CTLCardinality.xml

-rw-r--r-- 1 mcc users 7.0K Feb 26 03:27 CTLFireability.txt

-rw-r--r-- 1 mcc users 61K Feb 26 03:27 CTLFireability.xml

-rw-r--r-- 1 mcc users 3.8K Feb 25 16:51 LTLCardinality.txt

-rw-r--r-- 1 mcc users 23K Feb 25 16:51 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.6K Feb 25 16:51 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 16:51 LTLFireability.xml

-rw-r--r-- 1 mcc users 17K Feb 26 03:30 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 168K Feb 26 03:30 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 11K Feb 26 03:29 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 80K Feb 26 03:29 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K Feb 25 16:51 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.9K Feb 25 16:51 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 equiv_col

-rw-r--r-- 1 mcc users 7 Mar 5 18:23 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:23 iscolored

-rw-r--r-- 1 mcc users 4.1M Mar 5 18:23 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-00

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-01

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-02

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-03

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-04

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-05

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-06

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-07

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-08

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-09

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-10

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-11

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-12

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-13

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-14

FORMULA_NAME ServersAndClients-PT-100020-CTLCardinality-15

=== Now, execution of the tool begins

BK_START 1679945882537

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=marcie

BK_EXAMINATION=CTLCardinality

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=ServersAndClients-PT-100020

Not applying reductions.

Model is PT

CTLCardinality PT

timeout --kill-after=10s --signal=SIGINT 1m for testing only

Marcie built on Linux at 2019-11-18.

A model checker for Generalized Stochastic Petri nets

authors: Alex Tovchigrechko (IDD package and CTL model checking)

Martin Schwarick (Symbolic numerical analysis and CSL model checking)

Christian Rohr (Simulative and approximative numerical model checking)

marcie@informatik.tu-cottbus.de

called as: /home/mcc/BenchKit/bin//../marcie/bin/marcie --net-file=model.pnml --mcc-file=CTLCardinality.xml --memory=6 --mcc-mode

parse successfull

net created successfully

Net: ServersAndClients_PT_100020

(NrP: 2421 NrTr: 4200 NrArc: 12800)

parse formulas

formulas created successfully

place and transition orderings generation:0m 1.198sec

net check time: 0m 0.002sec

init dd package: 0m 3.440sec

RS generation: 23m 4.812sec

-> reachability set: #nodes 240363 (2.4e+05) #states 2,201 (3)

starting MCC model checker

--------------------------

checking: EG [sv15_c70<=1]

normalized: EG [sv15_c70<=1]

abstracting: (sv15_c70<=1)

states: 2,201 (3)

EG iterations: 0

-> the formula is TRUE

FORMULA ServersAndClients-PT-100020-CTLCardinality-04 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.020sec

checking: ~ [AG [EX [sv5_c39<=sv12_c73]]]

normalized: E [true U ~ [EX [sv5_c39<=sv12_c73]]]

abstracting: (sv5_c39<=sv12_c73)

states: 2,200 (3)

MC time: 2m28.038sec

checking: AF [A [[~ [EX [[att22<=sv11_c52 & sv10_c18<=1]]] | EX [EX [sv7_c2<=sv8_c23]]] U 1<=sv6_c40]]

normalized: ~ [EG [~ [[~ [EG [~ [1<=sv6_c40]]] & ~ [E [~ [1<=sv6_c40] U [~ [[EX [EX [sv7_c2<=sv8_c23]] | ~ [EX [[att22<=sv11_c52 & sv10_c18<=1]]]]] & ~ [1<=sv6_c40]]]]]]]]

abstracting: (1<=sv6_c40)

states: 1

abstracting: (sv10_c18<=1)

states: 2,201 (3)

abstracting: (att22<=sv11_c52)

states: 2,179 (3)

.abstracting: (sv7_c2<=sv8_c23)

states: 2,200 (3)

MC time: 2m18.027sec

checking: EF [AG [[E [sv5_c54<=sv3_c40 U ~ [A [sv5_c6<=0 U 1<=sv6_c20]]] & [sv8_c39<=0 | sv13_c96<=1]]]]

normalized: E [true U ~ [E [true U ~ [[[sv8_c39<=0 | sv13_c96<=1] & E [sv5_c54<=sv3_c40 U ~ [[~ [EG [~ [1<=sv6_c20]]] & ~ [E [~ [1<=sv6_c20] U [~ [1<=sv6_c20] & ~ [sv5_c6<=0]]]]]]]]]]]]

abstracting: (sv5_c6<=0)

states: 2,200 (3)

abstracting: (1<=sv6_c20)

states: 1

abstracting: (1<=sv6_c20)

states: 1

MC time: 2m 9.000sec

checking: A [1<=sv10_c20 U [A [~ [AG [A [sv1_c28<=sv10_c0 U sv2_c42<=sv19_c73]]] U EG [EF [sv8_c40<=0]]] & sv1_c72<=0]]

normalized: [~ [EG [~ [[[~ [EG [~ [EG [E [true U sv8_c40<=0]]]]] & ~ [E [~ [EG [E [true U sv8_c40<=0]]] U [~ [EG [E [true U sv8_c40<=0]]] & ~ [E [true U ~ [[~ [E [~ [sv2_c42<=sv19_c73] U [~ [sv1_c28<=sv10_c0] & ~ [sv2_c42<=sv19_c73]]]] & ~ [EG [~ [sv2_c42<=sv19_c73]]]]]]]]]]] & sv1_c72<=0]]]] & ~ [E [~ [[[~ [EG [~ [EG [E [true U sv8_c40<=0]]]]] & ~ [E [~ [EG [E [true U sv8_c40<=0]]] U [~ [EG [E [true U sv8_c40<=0]]] & ~ [E [true U ~ [[~ [E [~ [sv2_c42<=sv19_c73] U [~ [sv1_c28<=sv10_c0] & ~ [sv2_c42<=sv19_c73]]]] & ~ [EG [~ [sv2_c42<=sv19_c73]]]]]]]]]]] & sv1_c72<=0]] U [~ [[[~ [EG [~ [EG [E [true U sv8_c40<=0]]]]] & ~ [E [~ [EG [E [true U sv8_c40<=0]]] U [~ [EG [E [true U sv8_c40<=0]]] & ~ [E [true U ~ [[~ [E [~ [sv2_c42<=sv19_c73] U [~ [sv1_c28<=sv10_c0] & ~ [sv2_c42<=sv19_c73]]]] & ~ [EG [~ [sv2_c42<=sv19_c73]]]]]]]]]]] & sv1_c72<=0]] & ~ [1<=sv10_c20]]]]]

abstracting: (1<=sv10_c20)

states: 1

abstracting: (sv1_c72<=0)

states: 2,200 (3)

abstracting: (sv2_c42<=sv19_c73)

states: 2,200 (3)

.MC time: 2m 0.010sec

checking: AF [AF [[AG [[E [sv17_c2<=sv0_c91 U sv8_c8<=sv2_c17] & AX [sv10_c31<=0]]] & ~ [[EG [1<=sv19_c55] & A [sv9_c59<=sv16_c74 U sv6_c80<=1]]]]]]

normalized: ~ [EG [EG [~ [[~ [E [true U ~ [[E [sv17_c2<=sv0_c91 U sv8_c8<=sv2_c17] & ~ [EX [~ [sv10_c31<=0]]]]]]] & ~ [[EG [1<=sv19_c55] & [~ [EG [~ [sv6_c80<=1]]] & ~ [E [~ [sv6_c80<=1] U [~ [sv6_c80<=1] & ~ [sv9_c59<=sv16_c74]]]]]]]]]]]]

abstracting: (sv9_c59<=sv16_c74)

states: 2,200 (3)

abstracting: (sv6_c80<=1)

states: 2,201 (3)

abstracting: (sv6_c80<=1)

states: 2,201 (3)

abstracting: (sv6_c80<=1)

states: 2,201 (3)

.

EG iterations: 1

abstracting: (1<=sv19_c55)

states: 1

..

EG iterations: 2

abstracting: (sv10_c31<=0)

states: 2,200 (3)

.abstracting: (sv8_c8<=sv2_c17)

states: 2,200 (3)

abstracting: (sv17_c2<=sv0_c91)

states: 2,200 (3)

MC time: 1m52.003sec

checking: ~ [[~ [[EG [EF [AG [sv6_c24<=0]]] | AX [~ [[~ [sys_req80<=sv15_c44] | A [sv1_c47<=1 U sv8_c74<=sv4_c86]]]]]] | AX [A [A [~ [1<=sys_req90] U AF [1<=sv12_c0]] U [E [sv5_c64<=sv13_c66 U init99<=0] & AF [sv17_c2<=1]]]]]]

normalized: ~ [[~ [EX [~ [[~ [E [~ [[~ [EG [~ [sv17_c2<=1]]] & E [sv5_c64<=sv13_c66 U init99<=0]]] U [~ [[~ [E [EG [~ [1<=sv12_c0]] U [EG [~ [1<=sv12_c0]] & 1<=sys_req90]]] & ~ [EG [EG [~ [1<=sv12_c0]]]]]] & ~ [[~ [EG [~ [sv17_c2<=1]]] & E [sv5_c64<=sv13_c66 U init99<=0]]]]]] & ~ [EG [~ [[~ [EG [~ [sv17_c2<=1]]] & E [sv5_c64<=sv13_c66 U init99<=0]]]]]]]]] | ~ [[EG [E [true U ~ [E [true U ~ [sv6_c24<=0]]]]] | ~ [EX [[[~ [EG [~ [sv8_c74<=sv4_c86]]] & ~ [E [~ [sv8_c74<=sv4_c86] U [~ [sv1_c47<=1] & ~ [sv8_c74<=sv4_c86]]]]] | ~ [sys_req80<=sv15_c44]]]]]]]]

abstracting: (sys_req80<=sv15_c44)

states: 2,200 (3)

abstracting: (sv8_c74<=sv4_c86)

states: 2,200 (3)

abstracting: (sv1_c47<=1)

states: 2,201 (3)

abstracting: (sv8_c74<=sv4_c86)

states: 2,200 (3)

abstracting: (sv8_c74<=sv4_c86)

states: 2,200 (3)

..

EG iterations: 2

.abstracting: (sv6_c24<=0)

states: 2,200 (3)

MC time: 1m45.000sec

checking: AG [E [[1<=sv2_c29 | [[AG [1<=sv6_c57] | EG [1<=sv6_c22]] | E [[1<=init89 | sys_req41<=sv0] U EF [sv13_c90<=sv8_c94]]]] U [sv16_c8<=sv6_c63 | AG [A [1<=sv10_c29 U sv5_c28<=0]]]]]

normalized: ~ [E [true U ~ [E [[[E [[1<=init89 | sys_req41<=sv0] U E [true U sv13_c90<=sv8_c94]] | [EG [1<=sv6_c22] | ~ [E [true U ~ [1<=sv6_c57]]]]] | 1<=sv2_c29] U [~ [E [true U ~ [[~ [EG [~ [sv5_c28<=0]]] & ~ [E [~ [sv5_c28<=0] U [~ [1<=sv10_c29] & ~ [sv5_c28<=0]]]]]]]] | sv16_c8<=sv6_c63]]]]]

abstracting: (sv16_c8<=sv6_c63)

states: 2,200 (3)

abstracting: (sv5_c28<=0)

states: 2,200 (3)

abstracting: (1<=sv10_c29)

states: 1

abstracting: (sv5_c28<=0)

states: 2,200 (3)

abstracting: (sv5_c28<=0)

states: 2,200 (3)

..

EG iterations: 2

MC time: 1m38.000sec

checking: AX [[[[[[AX [sv9_c37<=sv7_c78] & [sv7_c23<=sv14_c45 & [init72<=0 | sv16_c47<=1]]] | ~ [1<=sv14_c3]] | ~ [EF [[1<=sv8_c43 & sv19_c53<=sv2_c83]]]] & EX [AX [init76<=0]]] | EG [AG [[EX [sv12_c26<=1] & [sv1_c72<=init62 & sv14_c84<=0]]]]]]

normalized: ~ [EX [~ [[EG [~ [E [true U ~ [[EX [sv12_c26<=1] & [sv1_c72<=init62 & sv14_c84<=0]]]]]] | [[[[[[init72<=0 | sv16_c47<=1] & sv7_c23<=sv14_c45] & ~ [EX [~ [sv9_c37<=sv7_c78]]]] | ~ [1<=sv14_c3]] | ~ [E [true U [1<=sv8_c43 & sv19_c53<=sv2_c83]]]] & EX [~ [EX [~ [init76<=0]]]]]]]]]

abstracting: (init76<=0)

states: 22

MC time: 1m31.049sec

checking: EG [[[[AF [EG [sv11_c45<=sv2_c29]] & [~ [[AG [1<=sv16_c1] | [sv11_c20<=sv4_c64 & 1<=sys_req57]]] & [AG [1<=init47] | sv5_c87<=1]]] & AF [[EF [1<=sv17_c5] & ~ [[sv11_c4<=sv6_c25 & sv15_c40<=sv9_c90]]]]] | EF [[1<=sv14_c1 | EX [~ [sv10_c69<=sv9_c17]]]]]]

normalized: EG [[[[[~ [[[sv11_c20<=sv4_c64 & 1<=sys_req57] | ~ [E [true U ~ [1<=sv16_c1]]]]] & [~ [E [true U ~ [1<=init47]]] | sv5_c87<=1]] & ~ [EG [~ [EG [sv11_c45<=sv2_c29]]]]] & ~ [EG [~ [[~ [[sv11_c4<=sv6_c25 & sv15_c40<=sv9_c90]] & E [true U 1<=sv17_c5]]]]]] | E [true U [EX [~ [sv10_c69<=sv9_c17]] | 1<=sv14_c1]]]]

abstracting: (1<=sv14_c1)

states: 1

abstracting: (sv10_c69<=sv9_c17)

states: 2,200 (3)

.MC time: 1m25.000sec

checking: AX [[E [E [[sv14_c99<=0 | sv18_c50<=1] U sv18_c2<=sys_req11] U ~ [[~ [1<=sv1_c69] & sv1_c18<=sv1_c8]]] & A [EX [E [sv18_c33<=1 U sv16_c74<=sv0_c16]] U [A [[sv11_c78<=0 | sv5_c20<=sv8] U [sv4_c2<=1 | sv4_c65<=sv8_c94]] & ~ [AG [1<=sys_rep60]]]]]]

normalized: ~ [EX [~ [[[~ [EG [~ [[E [true U ~ [1<=sys_rep60]] & [~ [EG [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]] & ~ [E [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]] U [~ [[sv11_c78<=0 | sv5_c20<=sv8]] & ~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]]]]]]]] & ~ [E [~ [[E [true U ~ [1<=sys_rep60]] & [~ [EG [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]] & ~ [E [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]] U [~ [[sv11_c78<=0 | sv5_c20<=sv8]] & ~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]]]]]] U [~ [[E [true U ~ [1<=sys_rep60]] & [~ [EG [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]] & ~ [E [~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]] U [~ [[sv11_c78<=0 | sv5_c20<=sv8]] & ~ [[sv4_c2<=1 | sv4_c65<=sv8_c94]]]]]]]] & ~ [EX [E [sv18_c33<=1 U sv16_c74<=sv0_c16]]]]]]] & E [E [[sv14_c99<=0 | sv18_c50<=1] U sv18_c2<=sys_req11] U ~ [[~ [1<=sv1_c69] & sv1_c18<=sv1_c8]]]]]]]

abstracting: (sv1_c18<=sv1_c8)

states: 2,200 (3)

abstracting: (1<=sv1_c69)

states: 1

abstracting: (sv18_c2<=sys_req11)

states: 2,200 (3)

abstracting: (sv18_c50<=1)

states: 2,201 (3)

abstracting: (sv14_c99<=0)

states: 2,200 (3)

MC time: 1m19.006sec

checking: E [A [AX [[~ [1<=sv7_c22] & [EF [sv10_c61<=0] & AX [sv9_c53<=1]]]] U ~ [EF [[A [sv1_c60<=sv14_c58 U sv18_c36<=1] & ~ [sv16_c86<=0]]]]] U [E [[E [[sv4_c46<=0 & sv18_c42<=sv4_c36] U [sv4_c91<=1 | 1<=sv10_c59]] & AX [EX [sv5_c31<=0]]] U ~ [EF [E [1<=sv11_c96 U sv2_c45<=0]]]] & [init16<=0 | [AX [sv2_c96<=0] & [AG [[1<=sv8_c36 & sv15_c47<=sv2_c32]] & [1<=sv5_c35 & EF [1<=sv15_c88]]]]]]]

normalized: E [[~ [EG [E [true U [~ [sv16_c86<=0] & [~ [EG [~ [sv18_c36<=1]]] & ~ [E [~ [sv18_c36<=1] U [~ [sv1_c60<=sv14_c58] & ~ [sv18_c36<=1]]]]]]]]] & ~ [E [E [true U [~ [sv16_c86<=0] & [~ [EG [~ [sv18_c36<=1]]] & ~ [E [~ [sv18_c36<=1] U [~ [sv1_c60<=sv14_c58] & ~ [sv18_c36<=1]]]]]]] U [EX [~ [[[E [true U sv10_c61<=0] & ~ [EX [~ [sv9_c53<=1]]]] & ~ [1<=sv7_c22]]]] & E [true U [~ [sv16_c86<=0] & [~ [EG [~ [sv18_c36<=1]]] & ~ [E [~ [sv18_c36<=1] U [~ [sv1_c60<=sv14_c58] & ~ [sv18_c36<=1]]]]]]]]]]] U [E [[~ [EX [~ [EX [sv5_c31<=0]]]] & E [[sv4_c46<=0 & sv18_c42<=sv4_c36] U [sv4_c91<=1 | 1<=sv10_c59]]] U ~ [E [true U E [1<=sv11_c96 U sv2_c45<=0]]]] & [[[~ [E [true U ~ [[1<=sv8_c36 & sv15_c47<=sv2_c32]]]] & [E [true U 1<=sv15_c88] & 1<=sv5_c35]] & ~ [EX [~ [sv2_c96<=0]]]] | init16<=0]]]

abstracting: (init16<=0)

states: 22

abstracting: (sv2_c96<=0)

states: 2,200 (3)

.abstracting: (1<=sv5_c35)

states: 1

abstracting: (1<=sv15_c88)

states: 1

MC time: 1m14.000sec

checking: [EG [[[~ [1<=sv11_c49] | EF [[A [1<=sv2_c68 U 1<=sv15_c63] | AX [1<=sv7_c47]]]] | [[[A [sv12_c73<=att67 U sv11_c6<=1] & [E [sv14_c94<=1 U 1<=sv14_c17] | [1<=sv10_c76 | sv7_c17<=1]]] & [1<=sv12_c18 & AF [1<=sv15_c82]]] & [~ [AG [sv17_c91<=sv16_c35]] | [EF [1<=sv2_c93] & [~ [sys_rep74<=1] | [sv8_c2<=sv8_c63 & init44<=1]]]]]]] & AF [EG [A [[EF [sv7_c55<=sv3_c51] & AF [sys_rep28<=sv2_c99]] U sv1_c21<=0]]]]

normalized: [~ [EG [~ [EG [[~ [EG [~ [sv1_c21<=0]]] & ~ [E [~ [sv1_c21<=0] U [~ [[E [true U sv7_c55<=sv3_c51] & ~ [EG [~ [sys_rep28<=sv2_c99]]]]] & ~ [sv1_c21<=0]]]]]]]]] & EG [[[[[[[sv8_c2<=sv8_c63 & init44<=1] | ~ [sys_rep74<=1]] & E [true U 1<=sv2_c93]] | E [true U ~ [sv17_c91<=sv16_c35]]] & [[~ [EG [~ [1<=sv15_c82]]] & 1<=sv12_c18] & [[[1<=sv10_c76 | sv7_c17<=1] | E [sv14_c94<=1 U 1<=sv14_c17]] & [~ [EG [~ [sv11_c6<=1]]] & ~ [E [~ [sv11_c6<=1] U [~ [sv12_c73<=att67] & ~ [sv11_c6<=1]]]]]]]] | [E [true U [~ [EX [~ [1<=sv7_c47]]] | [~ [EG [~ [1<=sv15_c63]]] & ~ [E [~ [1<=sv15_c63] U [~ [1<=sv2_c68] & ~ [1<=sv15_c63]]]]]]] | ~ [1<=sv11_c49]]]]]

abstracting: (1<=sv11_c49)

states: 1

abstracting: (1<=sv15_c63)

states: 1

abstracting: (1<=sv2_c68)

states: 1

abstracting: (1<=sv15_c63)

states: 1

MC time: 1m 9.033sec

checking: A [[[[1<=sv17_c27 & ~ [[[E [sv14_c27<=1 U sys_rep88<=sv15_c46] | EG [sv7_c20<=sv9_c68]] | [E [1<=sv10_c9 U sv6_c54<=1] | E [sv13_c86<=0 U sv16_c6<=sv15_c99]]]]] | E [sv12_c67<=0 U A [EF [sv16_c0<=0] U [sys_req90<=sys_req65 & sv3_c13<=0]]]] | [~ [A [[[sys_req26<=sv7_c64 & 1<=sv6_c99] & E [sv6_c57<=sv5_c44 U 1<=sv16_c96]] U E [sv19_c36<=0 U sv8_c42<=att45]]] & sys_req19<=sv11_c22]] U 1<=sv11_c6]

normalized: [~ [EG [~ [1<=sv11_c6]]] & ~ [E [~ [1<=sv11_c6] U [~ [[[~ [[~ [EG [~ [E [sv19_c36<=0 U sv8_c42<=att45]]]] & ~ [E [~ [E [sv19_c36<=0 U sv8_c42<=att45]] U [~ [E [sv19_c36<=0 U sv8_c42<=att45]] & ~ [[E [sv6_c57<=sv5_c44 U 1<=sv16_c96] & [sys_req26<=sv7_c64 & 1<=sv6_c99]]]]]]]] & sys_req19<=sv11_c22] | [E [sv12_c67<=0 U [~ [EG [~ [[sys_req90<=sys_req65 & sv3_c13<=0]]]] & ~ [E [~ [[sys_req90<=sys_req65 & sv3_c13<=0]] U [~ [E [true U sv16_c0<=0]] & ~ [[sys_req90<=sys_req65 & sv3_c13<=0]]]]]]] | [~ [[[E [sv13_c86<=0 U sv16_c6<=sv15_c99] | E [1<=sv10_c9 U sv6_c54<=1]] | [EG [sv7_c20<=sv9_c68] | E [sv14_c27<=1 U sys_rep88<=sv15_c46]]]] & 1<=sv17_c27]]]] & ~ [1<=sv11_c6]]]]]

abstracting: (1<=sv11_c6)

states: 1

abstracting: (1<=sv17_c27)

states: 1

abstracting: (sys_rep88<=sv15_c46)

states: 2,200 (3)

abstracting: (sv14_c27<=1)

states: 2,201 (3)

MC time: 1m 5.029sec

checking: [A [~ [[AF [[AX [1<=sv12_c66] & EX [sv3_c52<=1]]] | [[~ [sv7_c84<=1] | AG [sv4_c75<=0]] & sv5_c33<=sv19_c37]]] U [[EF [~ [sv7_c91<=1]] | ~ [[[[sys_req40<=1 | sv8_c33<=sv19_c88] & [1<=sv17_c96 & 1<=sv4_c50]] & A [sv12_c9<=0 U sv10_c22<=1]]]] | AF [[AG [sv19_c89<=sv1_c18] | AG [sv10_c14<=sys_rep81]]]]] & ~ [[EG [EF [[sv18_c54<=sv3_c65 | sv14_c41<=sv18_c21]]] & A [[EF [1<=sv18_c72] | [[sv10_c60<=sv14_c84 & sv10_c1<=1] | ~ [1<=sv19_c33]]] U [1<=init36 & ~ [EG [sv12_c88<=1]]]]]]]

normalized: [~ [[[~ [EG [~ [[~ [EG [sv12_c88<=1]] & 1<=init36]]]] & ~ [E [~ [[~ [EG [sv12_c88<=1]] & 1<=init36]] U [~ [[E [true U 1<=sv18_c72] | [[sv10_c60<=sv14_c84 & sv10_c1<=1] | ~ [1<=sv19_c33]]]] & ~ [[~ [EG [sv12_c88<=1]] & 1<=init36]]]]]] & EG [E [true U [sv18_c54<=sv3_c65 | sv14_c41<=sv18_c21]]]]] & [~ [EG [~ [[~ [EG [~ [[~ [E [true U ~ [sv10_c14<=sys_rep81]]] | ~ [E [true U ~ [sv19_c89<=sv1_c18]]]]]]] | [~ [[[~ [EG [~ [sv10_c22<=1]]] & ~ [E [~ [sv10_c22<=1] U [~ [sv12_c9<=0] & ~ [sv10_c22<=1]]]]] & [[1<=sv17_c96 & 1<=sv4_c50] & [sys_req40<=1 | sv8_c33<=sv19_c88]]]] | E [true U ~ [sv7_c91<=1]]]]]]] & ~ [E [~ [[~ [EG [~ [[~ [E [true U ~ [sv10_c14<=sys_rep81]]] | ~ [E [true U ~ [sv19_c89<=sv1_c18]]]]]]] | [~ [[[~ [EG [~ [sv10_c22<=1]]] & ~ [E [~ [sv10_c22<=1] U [~ [sv12_c9<=0] & ~ [sv10_c22<=1]]]]] & [[1<=sv17_c96 & 1<=sv4_c50] & [sys_req40<=1 | sv8_c33<=sv19_c88]]]] | E [true U ~ [sv7_c91<=1]]]]] U [[[[~ [E [true U ~ [sv4_c75<=0]]] | ~ [sv7_c84<=1]] & sv5_c33<=sv19_c37] | ~ [EG [~ [[EX [sv3_c52<=1] & ~ [EX [~ [1<=sv12_c66]]]]]]]] & ~ [[~ [EG [~ [[~ [E [true U ~ [sv10_c14<=sys_rep81]]] | ~ [E [true U ~ [sv19_c89<=sv1_c18]]]]]]] | [~ [[[~ [EG [~ [sv10_c22<=1]]] & ~ [E [~ [sv10_c22<=1] U [~ [sv12_c9<=0] & ~ [sv10_c22<=1]]]]] & [[1<=sv17_c96 & 1<=sv4_c50] & [sys_req40<=1 | sv8_c33<=sv19_c88]]]] | E [true U ~ [sv7_c91<=1]]]]]]]]]]

abstracting: (sv7_c91<=1)

states: 2,201 (3)

abstracting: (sv8_c33<=sv19_c88)

states: 2,200 (3)

abstracting: (sys_req40<=1)

states: 2,201 (3)

abstracting: (1<=sv4_c50)

states: 1

abstracting: (1<=sv17_c96)

states: 1

abstracting: (sv10_c22<=1)

states: 2,201 (3)

abstracting: (sv12_c9<=0)

states: 2,200 (3)

abstracting: (sv10_c22<=1)

states: 2,201 (3)

abstracting: (sv10_c22<=1)

states: 2,201 (3)

.

EG iterations: 1

abstracting: (sv19_c89<=sv1_c18)

states: 2,200 (3)

MC time: 1m 0.000sec

checking: A [[E [EF [[1<=sv19_c84 & [sv14_c86<=0 & sv2_c39<=sv0_c78]]] U [E [~ [sv13_c36<=0] U E [1<=sv18_c31 U 1<=sv2_c25]] | ~ [EG [sv6_c8<=sv17_c76]]]] & ~ [[~ [sv2_c88<=sv1_c21] & sv15_c62<=sys_rep63]]] U AG [[~ [AX [sv3_c20<=sv13_c63]] | [[EF [1<=sv18_c9] | [sv2_c72<=sv12_c74 | AG [1<=sv7_c77]]] | [[E [sv18_c74<=sv17_c90 U sys_rep15<=sv6_c26] | [sv12_c73<=sv12_c83 & 1<=sv2_c51]] | [AG [sv2_c3<=1] & [init78<=sv19 | sv10_c93<=sv19_c34]]]]]]]

normalized: [~ [EG [E [true U ~ [[[[E [true U 1<=sv18_c9] | [~ [E [true U ~ [1<=sv7_c77]]] | sv2_c72<=sv12_c74]] | [[[init78<=sv19 | sv10_c93<=sv19_c34] & ~ [E [true U ~ [sv2_c3<=1]]]] | [[sv12_c73<=sv12_c83 & 1<=sv2_c51] | E [sv18_c74<=sv17_c90 U sys_rep15<=sv6_c26]]]] | EX [~ [sv3_c20<=sv13_c63]]]]]]] & ~ [E [E [true U ~ [[[[E [true U 1<=sv18_c9] | [~ [E [true U ~ [1<=sv7_c77]]] | sv2_c72<=sv12_c74]] | [[[init78<=sv19 | sv10_c93<=sv19_c34] & ~ [E [true U ~ [sv2_c3<=1]]]] | [[sv12_c73<=sv12_c83 & 1<=sv2_c51] | E [sv18_c74<=sv17_c90 U sys_rep15<=sv6_c26]]]] | EX [~ [sv3_c20<=sv13_c63]]]]] U [~ [[E [E [true U [[sv14_c86<=0 & sv2_c39<=sv0_c78] & 1<=sv19_c84]] U [E [~ [sv13_c36<=0] U E [1<=sv18_c31 U 1<=sv2_c25]] | ~ [EG [sv6_c8<=sv17_c76]]]] & ~ [[~ [sv2_c88<=sv1_c21] & sv15_c62<=sys_rep63]]]] & E [true U ~ [[[[E [true U 1<=sv18_c9] | [~ [E [true U ~ [1<=sv7_c77]]] | sv2_c72<=sv12_c74]] | [[[init78<=sv19 | sv10_c93<=sv19_c34] & ~ [E [true U ~ [sv2_c3<=1]]]] | [[sv12_c73<=sv12_c83 & 1<=sv2_c51] | E [sv18_c74<=sv17_c90 U sys_rep15<=sv6_c26]]]] | EX [~ [sv3_c20<=sv13_c63]]]]]]]]]

abstracting: (sv3_c20<=sv13_c63)

states: 2,200 (3)

.abstracting: (sys_rep15<=sv6_c26)

states: 2,200 (3)

abstracting: (sv18_c74<=sv17_c90)

states: 2,200 (3)

MC time: 0m56.054sec

checking: ~ [AG [EX [sv5_c39<=sv12_c73]]]

normalized: E [true U ~ [EX [sv5_c39<=sv12_c73]]]

abstracting: (sv5_c39<=sv12_c73)

states: 2,200 (3)

.-> the formula is FALSE

FORMULA ServersAndClients-PT-100020-CTLCardinality-14 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 3m51.883sec

checking: AF [A [[~ [EX [[att22<=sv11_c52 & sv10_c18<=1]]] | EX [EX [sv7_c2<=sv8_c23]]] U 1<=sv6_c40]]

normalized: ~ [EG [~ [[~ [EG [~ [1<=sv6_c40]]] & ~ [E [~ [1<=sv6_c40] U [~ [[~ [EX [[att22<=sv11_c52 & sv10_c18<=1]]] | EX [EX [sv7_c2<=sv8_c23]]]] & ~ [1<=sv6_c40]]]]]]]]

abstracting: (1<=sv6_c40)

states: 1

abstracting: (sv7_c2<=sv8_c23)

states: 2,200 (3)

..abstracting: (sv10_c18<=1)

states: 2,201 (3)

abstracting: (att22<=sv11_c52)

states: 2,179 (3)

.abstracting: (1<=sv6_c40)

states: 1

abstracting: (1<=sv6_c40)

states: 1

.

EG iterations: 1

.

EG iterations: 1

-> the formula is FALSE

FORMULA ServersAndClients-PT-100020-CTLCardinality-06 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 6m15.076sec

checking: EF [AG [[E [sv5_c54<=sv3_c40 U ~ [A [sv5_c6<=0 U 1<=sv6_c20]]] & [sv8_c39<=0 | sv13_c96<=1]]]]

normalized: E [true U ~ [E [true U ~ [[[sv8_c39<=0 | sv13_c96<=1] & E [sv5_c54<=sv3_c40 U ~ [[~ [EG [~ [1<=sv6_c20]]] & ~ [E [~ [1<=sv6_c20] U [~ [sv5_c6<=0] & ~ [1<=sv6_c20]]]]]]]]]]]]

abstracting: (1<=sv6_c20)

states: 1

abstracting: (sv5_c6<=0)

states: 2,200 (3)

abstracting: (1<=sv6_c20)

states: 1

TIME LIMIT: Killed by timeout after 3600 seconds

MemTotal: 16393916 kB

MemFree: 9787180 kB

After kill :

MemTotal: 16393916 kB

MemFree: 16173348 kB

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

check for maximal unmarked siphon

ok

check for constant places

ok

check if there are places and transitions

ok

check if there are transitions without pre-places

ok

check if at least one transition is enabled in m0

ok

check if there are transitions that can never fire

ok

initing FirstDep: 0m 0.026sec

64466 91622 113979 129456 142681 153167 156343 162936 165912 170654 174828 177162 180926 183425 186506 191689 192129 195244 200047 200627 203597 208461 208758 211393 216935 216963 218740 221845 225494 225997 228419 231625 234111 235138 237543

iterations count:3590420 (854), effective:2200 (0)

initing FirstDep: 0m 0.027sec

net_ddint.h:600: Timeout: after 147 sec

net_ddint.h:600: Timeout: after 137 sec

24480 38456

sat_reach.icc:155: Timeout: after 128 sec

net_ddint.h:442: Timeout: after 119 sec

sat_reach.icc:155: Timeout: after 111 sec

24481

sat_reach.icc:155: Timeout: after 104 sec

iterations count:4200 (1), effective:0 (0)

24904

sat_reach.icc:155: Timeout: after 97 sec

net_ddint.h:600: Timeout: after 90 sec

26669

sat_reach.icc:155: Timeout: after 84 sec

sat_reach.icc:155: Timeout: after 78 sec

25963

sat_reach.icc:155: Timeout: after 73 sec

sat_reach.icc:155: Timeout: after 68 sec

sat_reach.icc:155: Timeout: after 64 sec

24843

sat_reach.icc:155: Timeout: after 59 sec

sat_reach.icc:155: Timeout: after 55 sec

24480 38456

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ServersAndClients-PT-100020"

export BK_EXAMINATION="CTLCardinality"

export BK_TOOL="marcie"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool marcie"

echo " Input is ServersAndClients-PT-100020, examination is CTLCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 1"

echo " Run identifier is r353-smll-167891801100457"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ServersAndClients-PT-100020.tgz

mv ServersAndClients-PT-100020 execution

cd execution

if [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "UpperBounds" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] || [ "CTLCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLCardinality" = "ReachabilityDeadlock" ] || [ "CTLCardinality" = "QuasiLiveness" ] || [ "CTLCardinality" = "StableMarking" ] || [ "CTLCardinality" = "Liveness" ] || [ "CTLCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;