About the Execution of LoLA for BridgeAndVehicles-PT-V20P10N50

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16223.004 | 547788.00 | 3020846.00 | 4526.80 | ????????????T?FF | normal |

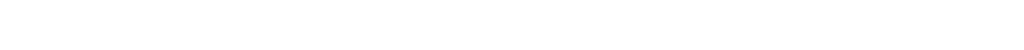

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2023-input.r038-tajo-167813691100194.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2023-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lola

Input is BridgeAndVehicles-PT-V20P10N50, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r038-tajo-167813691100194

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 8.1M

-rw-r--r-- 1 mcc users 19K Feb 25 12:16 CTLCardinality.txt

-rw-r--r-- 1 mcc users 125K Feb 25 12:16 CTLCardinality.xml

-rw-r--r-- 1 mcc users 347K Feb 25 12:12 CTLFireability.txt

-rw-r--r-- 1 mcc users 1.4M Feb 25 12:12 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 7.6K Feb 25 15:35 LTLCardinality.txt

-rw-r--r-- 1 mcc users 35K Feb 25 15:35 LTLCardinality.xml

-rw-r--r-- 1 mcc users 211K Feb 25 15:35 LTLFireability.txt

-rw-r--r-- 1 mcc users 641K Feb 25 15:35 LTLFireability.xml

-rw-r--r-- 1 mcc users 14K Feb 25 12:36 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 87K Feb 25 12:36 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 728K Feb 25 12:33 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 2.8M Feb 25 12:33 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.9K Feb 25 15:35 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.0K Feb 25 15:35 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 10 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 1.8M Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-00

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-01

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-02

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-03

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-04

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-05

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-06

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-07

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-08

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-09

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-10

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-11

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-12

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-13

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-14

FORMULA_NAME BridgeAndVehicles-PT-V20P10N50-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1678411417831

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lola

BK_EXAMINATION=CTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=BridgeAndVehicles-PT-V20P10N50

Not applying reductions.

Model is PT

CTLFireability PT

starting LoLA

BK_INPUT BridgeAndVehicles-PT-V20P10N50

BK_EXAMINATION: CTLFireability

bin directory: /home/mcc/BenchKit/bin//../lola/bin/

current directory: /home/mcc/execution

CTLFireability

FORMULA BridgeAndVehicles-PT-V20P10N50-CTLFireability-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA BridgeAndVehicles-PT-V20P10N50-CTLFireability-14 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA BridgeAndVehicles-PT-V20P10N50-CTLFireability-12 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

BK_STOP 1678411965619

--------------------

content from stderr:

lola: MEM LIMIT 32

lola: MEM LIMIT 5

lola: NET

lola: input: PNML file (--pnmlnet)

lola: reading net from /home/mcc/execution/model.pnml

lola: reading pnml

lola: PNML file contains place/transition net

lola: finished parsing

lola: closed net file /home/mcc/execution/model.pnml

lola: Reading formula.

lola: Using XML format (--xmlformula)

lola: reading XML formula

lola: reading formula from /home/mcc/execution/CTLFireability.xml

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:314