About the Execution of 2022-gold for BART-COL-040

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16225.632 | 3593452.00 | 8776787.00 | 2421.80 | TFT???TTFFFT??FF | normal |

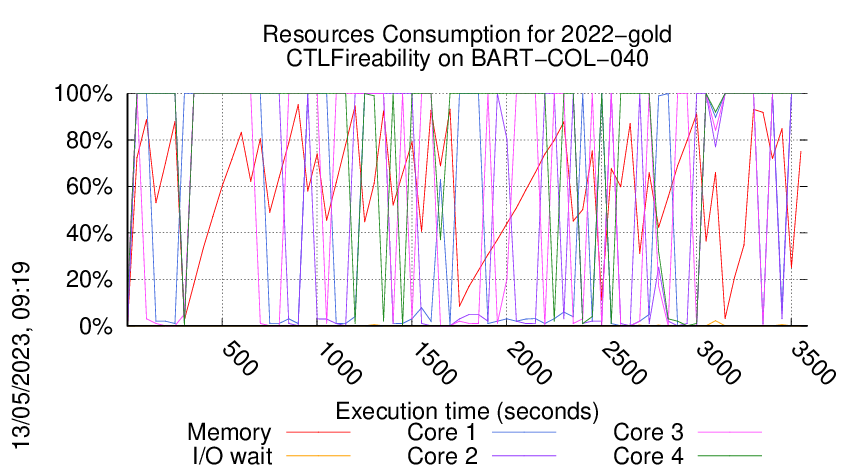

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r030-oct2-167813615200548.qcow2', fmt=qcow2 cluster_size=65536 extended_l2=off compression_type=zlib size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 backing_fmt=qcow2 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool gold2022

Input is BART-COL-040, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r030-oct2-167813615200548

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 684K

-rw-r--r-- 1 mcc users 9.4K Feb 26 06:43 CTLCardinality.txt

-rw-r--r-- 1 mcc users 97K Feb 26 06:43 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.1K Feb 26 04:27 CTLFireability.txt

-rw-r--r-- 1 mcc users 42K Feb 26 04:27 CTLFireability.xml

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 equiv_pt

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 5 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 3.9K Feb 25 15:35 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Feb 25 15:35 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.4K Feb 25 15:35 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 15:35 LTLFireability.xml

-rw-r--r-- 1 mcc users 207K Mar 5 18:22 model.pnml

-rw-r--r-- 1 mcc users 13K Feb 26 09:30 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 113K Feb 26 09:30 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 9.4K Feb 26 07:53 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 73K Feb 26 07:53 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 25 15:35 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K Feb 25 15:35 UpperBounds.xml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME BART-COL-040-CTLFireability-00

FORMULA_NAME BART-COL-040-CTLFireability-01

FORMULA_NAME BART-COL-040-CTLFireability-02

FORMULA_NAME BART-COL-040-CTLFireability-03

FORMULA_NAME BART-COL-040-CTLFireability-04

FORMULA_NAME BART-COL-040-CTLFireability-05

FORMULA_NAME BART-COL-040-CTLFireability-06

FORMULA_NAME BART-COL-040-CTLFireability-07

FORMULA_NAME BART-COL-040-CTLFireability-08

FORMULA_NAME BART-COL-040-CTLFireability-09

FORMULA_NAME BART-COL-040-CTLFireability-10

FORMULA_NAME BART-COL-040-CTLFireability-11

FORMULA_NAME BART-COL-040-CTLFireability-12

FORMULA_NAME BART-COL-040-CTLFireability-13

FORMULA_NAME BART-COL-040-CTLFireability-14

FORMULA_NAME BART-COL-040-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1678449627537

gold2022

Got BK_BIN_PATH=/home/mcc/BenchKit/bin/

---> gold2022 --- TAPAAL v5

Setting MODEL_PATH=.

Setting VERIFYPN=/home/mcc/BenchKit/bin/verifypn

Got BK_TIME_CONFINEMENT=3600

Setting TEMPDIR=/home/mcc/BenchKit/bin/tmp

Got BK_MEMORY_CONFINEMENT=16384

Limiting to 16265216 kB

Total timeout: 3590

Time left: 3590

*************************************

* TAPAAL verifying CTLFireability *

*************************************

TEMPDIR=/home/mcc/BenchKit/bin/tmp

QF=/home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh

MF=/home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR

Time left: 3590

---------------------------------------------------

Step -1: Stripping Colors

---------------------------------------------------

Verifying stripped models (16 in total)

/home/mcc/BenchKit/bin/verifypn -n -c -q 718 -l 29 -d 299 -z 4 -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-15

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-14

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-13

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-12

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-10

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-09

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-08

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-07

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-06

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-05

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-04

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-03

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-02

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-01

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-00

Unable to decide if BART-COL-040-CTLFireability-11 is satisfied.

Query is MAYBE satisfied.

Time left: 3590

---------------------------------------------------

Step 0: Parallel Simplification

---------------------------------------------------

Doing parallel simplification (16 in total)

Total simplification timout is 718 -- reduction timeout is 299

timeout 3590 /home/mcc/BenchKit/bin/verifypn -n -q 718 -l 29 -d 299 -z 4 -s OverApprox --binary-query-io 2 --write-simplified /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --write-reduced /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Time left: 3587

---------------------------------------------------

Step 1: Parallel processing

---------------------------------------------------

Doing parallel verification of individual queries (16 in total)

Each query is verified by 4 parallel strategies for 299 seconds

------------------- QUERY 1 ----------------------

Solution found by parallel processing (step 1)

Search strategy option was ignored as the TAR engine is called.

Query index 0 was solved

Query is satisfied.

Solved using Trace Abstraction Refinement

Spent 0.000319 on verification

@@@0.02,5952@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 1 -n

FORMULA BART-COL-040-CTLFireability-11 TRUE TECHNIQUES COLLATERAL_PROCESSING STRUCTURAL_REDUCTION QUERY_REDUCTION SAT_SMT TRACE_ABSTRACTION_REFINEMENT

Time left: 3586

------------------- QUERY 2 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.066527 on verification

@@@0.09,59720@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 2 -n

FORMULA BART-COL-040-CTLFireability-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3586

------------------- QUERY 3 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.060443 on verification

@@@0.10,59804@@@

Query index 0 was solved

Query is NOT satisfied.

Spent 0.057111 on verification

@@@0.10,59732@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 3 -n

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 3 -n

FORMULA BART-COL-040-CTLFireability-08 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3585

------------------- QUERY 4 ----------------------

No solution found

Command terminated by signal 9

@@@62.83,6062404@@@

Command terminated by signal 9

@@@107.25,9578100@@@

Command terminated by signal 9

@@@275.57,15793164@@@

Time left: 3284

------------------- QUERY 5 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.077225 on verification

@@@0.13,59900@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 5 -n

FORMULA BART-COL-040-CTLFireability-09 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3283

------------------- QUERY 6 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.068953 on verification

@@@0.08,59608@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 6 -n

FORMULA BART-COL-040-CTLFireability-07 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3283

------------------- QUERY 7 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.058437 on verification

@@@0.09,59836@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 7 -n

FORMULA BART-COL-040-CTLFireability-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3283

------------------- QUERY 8 ----------------------

No solution found

Time left: 2981

------------------- QUERY 9 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.11119 on verification

@@@0.12,59768@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 9 -n

FORMULA BART-COL-040-CTLFireability-01 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2980

------------------- QUERY 10 ----------------------

No solution found

Command terminated by signal 9

@@@65.65,6231792@@@

Command terminated by signal 9

@@@113.74,9605604@@@

Time left: 2679

------------------- QUERY 11 ----------------------

No solution found

Command terminated by signal 9

@@@68.96,6654216@@@

Command terminated by signal 9

@@@117.59,9940924@@@

Time left: 2376

------------------- QUERY 12 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.073835 on verification

@@@0.10,59952@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 12 -n

FORMULA BART-COL-040-CTLFireability-14 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2376

------------------- QUERY 13 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.071065 on verification

@@@0.07,59764@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 13 -n

FORMULA BART-COL-040-CTLFireability-02 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2375

------------------- QUERY 14 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.106096 on verification

@@@0.11,59808@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 14 -n

FORMULA BART-COL-040-CTLFireability-00 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2375

------------------- QUERY 15 ----------------------

No solution found

Command terminated by signal 9

@@@84.77,6195792@@@

Command terminated by signal 9

@@@150.22,9325556@@@

Time left: 2073

------------------- QUERY 16 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.071805 on verification

@@@0.11,59780@@@

Query index 0 was solved

Query is satisfied.

Spent 0.074567 on verification

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.IxGXtFaVfR /home/mcc/BenchKit/bin/tmp/tmp.BvgiS3ZLmh --binary-query-io 1 -x 16 -n

FORMULA BART-COL-040-CTLFireability-06 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2073

---------------------------------------------------

Step 2: Sequential processing

---------------------------------------------------

Remaining 5 queries are verified sequentially.

Each query is verified for a dynamic timeout (at least 598 seconds)

Time left: 2072

------------------- QUERY 4 ----------------------

Running query 4 for 598 seconds. Remaining: 5 queries and 2072 seconds

No solution found

Command terminated by signal 9

@@@92.51,8143036@@@

Command terminated by signal 9

@@@197.97,16146832@@@

Time left: 1874

------------------- QUERY 8 ----------------------

Running query 8 for 598 seconds. Remaining: 4 queries and 1874 seconds

No solution found

Time left: 1274

------------------- QUERY 10 ----------------------

Running query 10 for 598 seconds. Remaining: 3 queries and 1274 seconds

No solution found

Command terminated by signal 9

@@@84.75,8214820@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@178.73,15767780@@@

Time left: 1095

------------------- QUERY 11 ----------------------

Running query 11 for 598 seconds. Remaining: 2 queries and 1095 seconds

No solution found

Command terminated by signal 9

@@@84.77,8408256@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@169.08,15190224@@@

Time left: 925

------------------- QUERY 15 ----------------------

Running query 15 for 925 seconds. Remaining: 1 queries and 925 seconds

No solution found

Command terminated by signal 9

@@@137.43,9332280@@@

Command terminated by signal 9

@@@372.85,16143640@@@

Time left: 552

Time left: 552

---------------------------------------------------

Step 4: Random Parallel processing

---------------------------------------------------

Doing random parallel verification of individual queries (5 in total)

Each query is verified by 4 parallel strategies for 110 seconds

------------------- QUERY 4 ----------------------

No solution found

Command terminated by signal 9

@@@47.49,4171720@@@

Command terminated by signal 9

@@@65.31,5506344@@@

Command terminated by signal 9

@@@104.29,8134760@@@

Time left: 439

------------------- QUERY 8 ----------------------

No solution found

Time left: 326

------------------- QUERY 10 ----------------------

No solution found

Command terminated by signal 9

@@@45.38,4137188@@@

Command terminated by signal 9

@@@67.15,5484160@@@

Command terminated by signal 9

@@@103.68,8126140@@@

Time left: 214

------------------- QUERY 11 ----------------------

No solution found

Command terminated by signal 9

@@@45.90,4076872@@@

Command terminated by signal 9

@@@63.31,5446052@@@

Command terminated by signal 9

@@@98.72,8128884@@@

Time left: 101

------------------- QUERY 15 ----------------------

No solution found

Command terminated by signal 9

@@@93.98,4142016@@@

Time left: -3

Out of time, terminating!

terminated-with-cleanup

BK_STOP 1678453220989

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="BART-COL-040"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="gold2022"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool gold2022"

echo " Input is BART-COL-040, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r030-oct2-167813615200548"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/BART-COL-040.tgz

mv BART-COL-040 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;