About the Execution of 2022-gold for Angiogenesis-PT-50

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16226.575 | 3593294.00 | 10288118.00 | 1163.60 | T???TTTF?T??T?F? | normal |

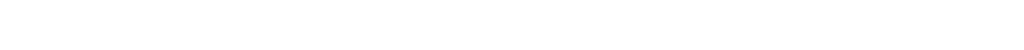

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r030-oct2-167813614800272.qcow2', fmt=qcow2 cluster_size=65536 extended_l2=off compression_type=zlib size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 backing_fmt=qcow2 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool gold2022

Input is Angiogenesis-PT-50, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r030-oct2-167813614800272

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 520K

-rw-r--r-- 1 mcc users 12K Feb 26 14:53 CTLCardinality.txt

-rw-r--r-- 1 mcc users 122K Feb 26 14:53 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.0K Feb 26 14:52 CTLFireability.txt

-rw-r--r-- 1 mcc users 58K Feb 26 14:52 CTLFireability.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.5K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 4.2K Feb 25 15:31 LTLCardinality.txt

-rw-r--r-- 1 mcc users 27K Feb 25 15:31 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.2K Feb 25 15:31 LTLFireability.txt

-rw-r--r-- 1 mcc users 19K Feb 25 15:31 LTLFireability.xml

-rw-r--r-- 1 mcc users 33K Mar 5 18:22 model.pnml

-rw-r--r-- 1 mcc users 10K Feb 26 14:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 92K Feb 26 14:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 8.0K Feb 26 14:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 72K Feb 26 14:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K Feb 25 15:31 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K Feb 25 15:31 UpperBounds.xml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-00

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-01

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-02

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-03

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-04

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-05

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-06

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-07

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-08

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-09

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-10

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-11

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-12

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-13

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-14

FORMULA_NAME Angiogenesis-PT-50-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1678430713971

gold2022

Got BK_BIN_PATH=/home/mcc/BenchKit/bin/

---> gold2022 --- TAPAAL v5

Setting MODEL_PATH=.

Setting VERIFYPN=/home/mcc/BenchKit/bin/verifypn

Got BK_TIME_CONFINEMENT=3600

Setting TEMPDIR=/home/mcc/BenchKit/bin/tmp

Got BK_MEMORY_CONFINEMENT=16384

Limiting to 16265216 kB

Total timeout: 3590

Time left: 3590

*************************************

* TAPAAL verifying CTLFireability *

*************************************

TEMPDIR=/home/mcc/BenchKit/bin/tmp

QF=/home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ

MF=/home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw

Time left: 3590

---------------------------------------------------

Step -1: Stripping Colors

---------------------------------------------------

Verifying stripped models (16 in total)

/home/mcc/BenchKit/bin/verifypn -n -c -q 718 -l 29 -d 299 -z 4 -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

CPN OverApproximation is only usable on colored models

Time left: 3590

---------------------------------------------------

Step 0: Parallel Simplification

---------------------------------------------------

Doing parallel simplification (16 in total)

Total simplification timout is 718 -- reduction timeout is 299

timeout 3590 /home/mcc/BenchKit/bin/verifypn -n -q 718 -l 29 -d 299 -z 4 -s OverApprox --binary-query-io 2 --write-simplified /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --write-reduced /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Time left: 3590

---------------------------------------------------

Step 1: Parallel processing

---------------------------------------------------

Doing parallel verification of individual queries (16 in total)

Each query is verified by 4 parallel strategies for 299 seconds

------------------- QUERY 1 ----------------------

Solution found by parallel processing (step 1)

Search strategy option was ignored as the TAR engine is called.

Query index 0 was solved

Query is satisfied.

Solved using Trace Abstraction Refinement

Spent 0.024734 on verification

@@@0.03,5584@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 1 -n

FORMULA Angiogenesis-PT-50-CTLFireability-05 TRUE TECHNIQUES COLLATERAL_PROCESSING STRUCTURAL_REDUCTION QUERY_REDUCTION SAT_SMT TRACE_ABSTRACTION_REFINEMENT

Time left: 3590

------------------- QUERY 2 ----------------------

No solution found

Command terminated by signal 9

@@@55.53,7031876@@@

Command terminated by signal 9

@@@107.31,10407524@@@

Time left: 3287

------------------- QUERY 3 ----------------------

No solution found

Command terminated by signal 9

@@@70.69,8014060@@@

Command terminated by signal 9

@@@165.06,14074144@@@

Time left: 2986

------------------- QUERY 4 ----------------------

No solution found

Command terminated by signal 9

@@@94.93,7300872@@@

Command terminated by signal 9

@@@192.52,8029256@@@

Time left: 2685

------------------- QUERY 5 ----------------------

No solution found

Command terminated by signal 9

@@@262.60,10041560@@@

Time left: 2383

------------------- QUERY 6 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.099163 on verification

@@@0.15,59156@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 6 -n

FORMULA Angiogenesis-PT-50-CTLFireability-06 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2382

------------------- QUERY 7 ----------------------

No solution found

Command terminated by signal 9

@@@102.25,7811276@@@

Command terminated by signal 9

@@@241.16,11173724@@@

Time left: 2081

------------------- QUERY 8 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.124871 on verification

@@@0.16,60216@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 8 -n

FORMULA Angiogenesis-PT-50-CTLFireability-12 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2080

------------------- QUERY 9 ----------------------

No solution found

Command terminated by signal 9

@@@106.16,7339088@@@

Command terminated by signal 9

@@@211.26,8047776@@@

Time left: 1778

------------------- QUERY 10 ----------------------

No solution found

Command terminated by signal 9

@@@130.72,8394852@@@

Time left: 1476

------------------- QUERY 11 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.176646 on verification

@@@0.22,65964@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 11 -n

FORMULA Angiogenesis-PT-50-CTLFireability-09 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 1476

------------------- QUERY 12 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.242023 on verification

@@@0.24,67024@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 12 -n

FORMULA Angiogenesis-PT-50-CTLFireability-04 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 1475

------------------- QUERY 13 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.086769 on verification

@@@0.13,59440@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 13 -n

FORMULA Angiogenesis-PT-50-CTLFireability-00 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 1475

------------------- QUERY 14 ----------------------

No solution found

Command terminated by signal 9

@@@91.49,6818744@@@

Command terminated by signal 9

@@@183.13,7983468@@@

Time left: 1174

------------------- QUERY 15 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.157688 on verification

@@@0.23,59808@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 15 -n

FORMULA Angiogenesis-PT-50-CTLFireability-07 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 1173

------------------- QUERY 16 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.078726 on verification

@@@0.08,59324@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.ukAJRPItYw /home/mcc/BenchKit/bin/tmp/tmp.7ZLpKh5CkQ --binary-query-io 1 -x 16 -n

FORMULA Angiogenesis-PT-50-CTLFireability-14 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 1172

---------------------------------------------------

Step 2: Sequential processing

---------------------------------------------------

Remaining 8 queries are verified sequentially.

Each query is verified for a dynamic timeout (at least 598 seconds)

Time left: 1172

------------------- QUERY 2 ----------------------

Running query 2 for 598 seconds. Remaining: 8 queries and 1172 seconds

No solution found

Command terminated by signal 9

@@@79.45,9154088@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@177.51,15325116@@@

Time left: 995

------------------- QUERY 3 ----------------------

Running query 3 for 598 seconds. Remaining: 7 queries and 995 seconds

No solution found

Command terminated by signal 9

@@@68.10,8697156@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@155.49,15757172@@@

Time left: 839

------------------- QUERY 4 ----------------------

Running query 4 for 598 seconds. Remaining: 6 queries and 839 seconds

No solution found

Command terminated by signal 9

@@@127.44,9790068@@@

Command terminated by signal 9

@@@341.73,16145880@@@

Time left: 496

------------------- QUERY 5 ----------------------

Time left: 496

---------------------------------------------------

Step 4: Random Parallel processing

---------------------------------------------------

Doing random parallel verification of individual queries (8 in total)

Each query is verified by 4 parallel strategies for 62 seconds

------------------- QUERY 2 ----------------------

No solution found

Command terminated by signal 9

@@@41.12,4641288@@@

Command terminated by signal 9

@@@58.53,6304160@@@

Time left: 432

------------------- QUERY 3 ----------------------

No solution found

Command terminated by signal 9

@@@42.16,4589404@@@

Command terminated by signal 9

@@@61.31,5510364@@@

Time left: 367

------------------- QUERY 4 ----------------------

No solution found

Command terminated by signal 9

@@@50.82,4430560@@@

Time left: 302

------------------- QUERY 5 ----------------------

No solution found

Time left: 237

------------------- QUERY 7 ----------------------

No solution found

Command terminated by signal 9

@@@43.64,4258196@@@

Command terminated by signal 9

@@@62.18,5488968@@@

Time left: 173

------------------- QUERY 9 ----------------------

No solution found

Command terminated by signal 9

@@@49.90,4302784@@@

Time left: 109

------------------- QUERY 10 ----------------------

No solution found

Command terminated by signal 9

@@@57.54,4256240@@@

Time left: 43

------------------- QUERY 14 ----------------------

No solution found

Time left: -3

Out of time, terminating!

terminated-with-cleanup

BK_STOP 1678434307265

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="Angiogenesis-PT-50"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="gold2022"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-5348"

echo " Executing tool gold2022"

echo " Input is Angiogenesis-PT-50, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r030-oct2-167813614800272"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/Angiogenesis-PT-50.tgz

mv Angiogenesis-PT-50 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;