About the Execution of LoLa+red for ASLink-PT-09a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 2208.535 | 720650.00 | 773713.00 | 30.10 | TT?F??T?FFFTFF?T | normal |

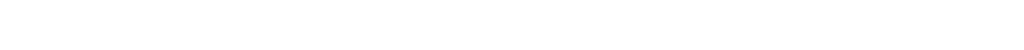

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2023-input.r007-oct2-167813595100138.qcow2', fmt=qcow2 cluster_size=65536 extended_l2=off compression_type=zlib size=4294967296 backing_file=/data/fkordon/mcc2023-input.qcow2 backing_fmt=qcow2 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-5348

Executing tool lolaxred

Input is ASLink-PT-09a, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r007-oct2-167813595100138

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.4M

-rw-r--r-- 1 mcc users 7.3K Feb 26 13:10 CTLCardinality.txt

-rw-r--r-- 1 mcc users 80K Feb 26 13:10 CTLCardinality.xml

-rw-r--r-- 1 mcc users 6.1K Feb 26 13:09 CTLFireability.txt

-rw-r--r-- 1 mcc users 56K Feb 26 13:09 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K Jan 29 11:40 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K Jan 29 11:40 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.9K Feb 25 15:30 LTLCardinality.txt

-rw-r--r-- 1 mcc users 26K Feb 25 15:30 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K Feb 25 15:30 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 25 15:30 LTLFireability.xml

-rw-r--r-- 1 mcc users 15K Feb 26 13:11 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 167K Feb 26 13:11 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 6.8K Feb 26 13:11 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 55K Feb 26 13:11 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 25 15:30 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Feb 25 15:30 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 5 18:22 instance

-rw-r--r-- 1 mcc users 6 Mar 5 18:22 iscolored

-rw-r--r-- 1 mcc users 839K Mar 5 18:22 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ASLink-PT-09a-CTLFireability-00

FORMULA_NAME ASLink-PT-09a-CTLFireability-01

FORMULA_NAME ASLink-PT-09a-CTLFireability-02

FORMULA_NAME ASLink-PT-09a-CTLFireability-03

FORMULA_NAME ASLink-PT-09a-CTLFireability-04

FORMULA_NAME ASLink-PT-09a-CTLFireability-05

FORMULA_NAME ASLink-PT-09a-CTLFireability-06

FORMULA_NAME ASLink-PT-09a-CTLFireability-07

FORMULA_NAME ASLink-PT-09a-CTLFireability-08

FORMULA_NAME ASLink-PT-09a-CTLFireability-09

FORMULA_NAME ASLink-PT-09a-CTLFireability-10

FORMULA_NAME ASLink-PT-09a-CTLFireability-11

FORMULA_NAME ASLink-PT-09a-CTLFireability-12

FORMULA_NAME ASLink-PT-09a-CTLFireability-13

FORMULA_NAME ASLink-PT-09a-CTLFireability-14

FORMULA_NAME ASLink-PT-09a-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1678341953759

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

Invoking MCC driver with

BK_TOOL=lolaxred

BK_EXAMINATION=CTLFireability

BK_BIN_PATH=/home/mcc/BenchKit/bin/

BK_TIME_CONFINEMENT=3600

BK_INPUT=ASLink-PT-09a

Applying reductions before tool lola

Invoking reducer

Running Version 202303021504

[2023-03-09 06:05:55] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -timeout, 360, -rebuildPNML]

[2023-03-09 06:05:55] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2023-03-09 06:05:55] [INFO ] Load time of PNML (sax parser for PT used): 156 ms

[2023-03-09 06:05:55] [INFO ] Transformed 1991 places.

[2023-03-09 06:05:55] [INFO ] Transformed 2919 transitions.

[2023-03-09 06:05:55] [INFO ] Found NUPN structural information;

[2023-03-09 06:05:55] [INFO ] Parsed PT model containing 1991 places and 2919 transitions and 10953 arcs in 258 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 9 ms.

Ensure Unique test removed 31 transitions

Reduce redundant transitions removed 31 transitions.

Support contains 220 out of 1991 places. Attempting structural reductions.

Starting structural reductions in LTL mode, iteration 0 : 1991/1991 places, 2888/2888 transitions.

Ensure Unique test removed 34 places

Discarding 14 places :

Implicit places reduction removed 14 places

Iterating post reduction 0 with 48 rules applied. Total rules applied 48 place count 1943 transition count 2888

Discarding 9 places :

Symmetric choice reduction at 1 with 9 rule applications. Total rules 57 place count 1934 transition count 2854

Ensure Unique test removed 1 places

Iterating global reduction 1 with 10 rules applied. Total rules applied 67 place count 1933 transition count 2854

Ensure Unique test removed 2 transitions

Reduce isomorphic transitions removed 2 transitions.

Iterating post reduction 1 with 2 rules applied. Total rules applied 69 place count 1933 transition count 2852

Applied a total of 69 rules in 411 ms. Remains 1933 /1991 variables (removed 58) and now considering 2852/2888 (removed 36) transitions.

// Phase 1: matrix 2852 rows 1933 cols

[2023-03-09 06:05:56] [INFO ] Computed 335 place invariants in 149 ms

[2023-03-09 06:05:58] [INFO ] Implicit Places using invariants in 1826 ms returned [1, 19, 20, 23, 33, 51, 69, 198, 215, 221, 241, 259, 404, 409, 430, 448, 577, 593, 598, 599, 600, 618, 636, 784, 789, 790, 791, 809, 827, 956, 972, 977, 978, 979, 997, 1015, 1144, 1160, 1165, 1166, 1186, 1204, 1334, 1350, 1355, 1376, 1394, 1523, 1539, 1546, 1564, 1582, 1716, 1729, 1734, 1736, 1771, 1773, 1795, 1796, 1797, 1814, 1822, 1830, 1836, 1842, 1848, 1854, 1862, 1868, 1874]

Discarding 71 places :

Implicit Place search using SMT only with invariants took 1862 ms to find 71 implicit places.

Starting structural reductions in LTL mode, iteration 1 : 1862/1991 places, 2852/2888 transitions.

Discarding 11 places :

Symmetric choice reduction at 0 with 11 rule applications. Total rules 11 place count 1851 transition count 2841

Iterating global reduction 0 with 11 rules applied. Total rules applied 22 place count 1851 transition count 2841

Discarding 7 places :

Symmetric choice reduction at 0 with 7 rule applications. Total rules 29 place count 1844 transition count 2834

Iterating global reduction 0 with 7 rules applied. Total rules applied 36 place count 1844 transition count 2834

Discarding 3 places :

Symmetric choice reduction at 0 with 3 rule applications. Total rules 39 place count 1841 transition count 2831

Iterating global reduction 0 with 3 rules applied. Total rules applied 42 place count 1841 transition count 2831

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 43 place count 1840 transition count 2830

Iterating global reduction 0 with 1 rules applied. Total rules applied 44 place count 1840 transition count 2830

Applied a total of 44 rules in 286 ms. Remains 1840 /1862 variables (removed 22) and now considering 2830/2852 (removed 22) transitions.

// Phase 1: matrix 2830 rows 1840 cols

[2023-03-09 06:05:58] [INFO ] Computed 264 place invariants in 71 ms

[2023-03-09 06:05:59] [INFO ] Implicit Places using invariants in 778 ms returned []

[2023-03-09 06:05:59] [INFO ] Invariant cache hit.

[2023-03-09 06:06:01] [INFO ] Implicit Places using invariants and state equation in 1665 ms returned []

Implicit Place search using SMT with State Equation took 2450 ms to find 0 implicit places.

Starting structural reductions in LTL mode, iteration 2 : 1840/1991 places, 2830/2888 transitions.

Finished structural reductions in LTL mode , in 2 iterations and 5010 ms. Remains : 1840/1991 places, 2830/2888 transitions.

Support contains 220 out of 1840 places after structural reductions.

[2023-03-09 06:06:01] [INFO ] Flatten gal took : 207 ms

[2023-03-09 06:06:01] [INFO ] Flatten gal took : 144 ms

[2023-03-09 06:06:02] [INFO ] Input system was already deterministic with 2830 transitions.

Support contains 217 out of 1840 places (down from 220) after GAL structural reductions.

Incomplete random walk after 10000 steps, including 45 resets, run finished after 486 ms. (steps per millisecond=20 ) properties (out of 93) seen :36

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 6 ms. (steps per millisecond=166 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 2 ms. (steps per millisecond=500 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 5 ms. (steps per millisecond=200 ) properties (out of 57) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 57) seen :0

Running SMT prover for 57 properties.

[2023-03-09 06:06:02] [INFO ] Invariant cache hit.

[2023-03-09 06:06:05] [INFO ] [Real]Absence check using 56 positive place invariants in 34 ms returned sat

[2023-03-09 06:06:06] [INFO ] [Real]Absence check using 56 positive and 208 generalized place invariants in 83 ms returned sat

[2023-03-09 06:06:06] [INFO ] After 3497ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:57

[2023-03-09 06:06:09] [INFO ] [Nat]Absence check using 56 positive place invariants in 46 ms returned sat

[2023-03-09 06:06:09] [INFO ] [Nat]Absence check using 56 positive and 208 generalized place invariants in 158 ms returned sat

[2023-03-09 06:06:31] [INFO ] After 18832ms SMT Verify possible using state equation in natural domain returned unsat :14 sat :42

[2023-03-09 06:06:31] [INFO ] After 18842ms SMT Verify possible using trap constraints in natural domain returned unsat :14 sat :42

Attempting to minimize the solution found.

Minimization took 3 ms.

[2023-03-09 06:06:31] [INFO ] After 25037ms SMT Verify possible using all constraints in natural domain returned unsat :14 sat :42

Fused 57 Parikh solutions to 4 different solutions.

Parikh walk visited 0 properties in 324 ms.

Support contains 120 out of 1840 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1840/1840 places, 2830/2830 transitions.

Ensure Unique test removed 2 places

Discarding 3 places :

Implicit places reduction removed 3 places

Drop transitions removed 281 transitions

Trivial Post-agglo rules discarded 281 transitions

Performed 281 trivial Post agglomeration. Transition count delta: 281

Iterating post reduction 0 with 286 rules applied. Total rules applied 286 place count 1835 transition count 2549

Reduce places removed 281 places and 0 transitions.

Performed 21 Post agglomeration using F-continuation condition.Transition count delta: 21

Iterating post reduction 1 with 302 rules applied. Total rules applied 588 place count 1554 transition count 2528

Reduce places removed 21 places and 0 transitions.

Iterating post reduction 2 with 21 rules applied. Total rules applied 609 place count 1533 transition count 2528

Performed 209 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 209 Pre rules applied. Total rules applied 609 place count 1533 transition count 2319

Deduced a syphon composed of 209 places in 4 ms

Ensure Unique test removed 71 places

Reduce places removed 280 places and 0 transitions.

Iterating global reduction 3 with 489 rules applied. Total rules applied 1098 place count 1253 transition count 2319

Discarding 3 places :

Implicit places reduction removed 3 places

Drop transitions removed 9 transitions

Trivial Post-agglo rules discarded 9 transitions

Performed 9 trivial Post agglomeration. Transition count delta: 9

Iterating post reduction 3 with 12 rules applied. Total rules applied 1110 place count 1250 transition count 2310

Reduce places removed 9 places and 0 transitions.

Iterating post reduction 4 with 9 rules applied. Total rules applied 1119 place count 1241 transition count 2310

Performed 12 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 5 with 12 Pre rules applied. Total rules applied 1119 place count 1241 transition count 2298

Deduced a syphon composed of 12 places in 3 ms

Reduce places removed 12 places and 0 transitions.

Iterating global reduction 5 with 24 rules applied. Total rules applied 1143 place count 1229 transition count 2298

Discarding 3 places :

Symmetric choice reduction at 5 with 3 rule applications. Total rules 1146 place count 1226 transition count 2295

Iterating global reduction 5 with 3 rules applied. Total rules applied 1149 place count 1226 transition count 2295

Drop transitions removed 1 transitions

Trivial Post-agglo rules discarded 1 transitions

Performed 1 trivial Post agglomeration. Transition count delta: 1

Iterating post reduction 5 with 1 rules applied. Total rules applied 1150 place count 1226 transition count 2294

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 6 with 1 rules applied. Total rules applied 1151 place count 1225 transition count 2294

Discarding 2 places :

Symmetric choice reduction at 7 with 2 rule applications. Total rules 1153 place count 1223 transition count 2292

Iterating global reduction 7 with 2 rules applied. Total rules applied 1155 place count 1223 transition count 2292

Performed 93 Post agglomeration using F-continuation condition.Transition count delta: 93

Deduced a syphon composed of 93 places in 3 ms

Ensure Unique test removed 1 places

Reduce places removed 94 places and 0 transitions.

Iterating global reduction 7 with 187 rules applied. Total rules applied 1342 place count 1129 transition count 2199

Discarding 1 places :

Symmetric choice reduction at 7 with 1 rule applications. Total rules 1343 place count 1128 transition count 2198

Iterating global reduction 7 with 1 rules applied. Total rules applied 1344 place count 1128 transition count 2198

Drop transitions removed 1 transitions

Trivial Post-agglo rules discarded 1 transitions

Performed 1 trivial Post agglomeration. Transition count delta: 1

Iterating post reduction 7 with 1 rules applied. Total rules applied 1345 place count 1128 transition count 2197

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 8 with 1 rules applied. Total rules applied 1346 place count 1127 transition count 2197

Discarding 1 places :

Symmetric choice reduction at 9 with 1 rule applications. Total rules 1347 place count 1126 transition count 2196

Iterating global reduction 9 with 1 rules applied. Total rules applied 1348 place count 1126 transition count 2196

Free-agglomeration rule applied 2 times.

Iterating global reduction 9 with 2 rules applied. Total rules applied 1350 place count 1126 transition count 2194

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 9 with 2 rules applied. Total rules applied 1352 place count 1124 transition count 2194

Free-agglomeration rule (complex) applied 42 times.

Iterating global reduction 10 with 42 rules applied. Total rules applied 1394 place count 1124 transition count 2154

Ensure Unique test removed 1 places

Reduce places removed 43 places and 0 transitions.

Iterating post reduction 10 with 43 rules applied. Total rules applied 1437 place count 1081 transition count 2154

Drop transitions removed 1 transitions

Redundant transition composition rules discarded 1 transitions

Iterating global reduction 11 with 1 rules applied. Total rules applied 1438 place count 1081 transition count 2153

Partial Free-agglomeration rule applied 33 times.

Drop transitions removed 33 transitions

Iterating global reduction 11 with 33 rules applied. Total rules applied 1471 place count 1081 transition count 2153

Partial Post-agglomeration rule applied 2 times.

Drop transitions removed 2 transitions

Iterating global reduction 11 with 2 rules applied. Total rules applied 1473 place count 1081 transition count 2153

Drop transitions removed 1 transitions

Redundant transition composition rules discarded 1 transitions

Iterating global reduction 11 with 1 rules applied. Total rules applied 1474 place count 1081 transition count 2152

Applied a total of 1474 rules in 749 ms. Remains 1081 /1840 variables (removed 759) and now considering 2152/2830 (removed 678) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 750 ms. Remains : 1081/1840 places, 2152/2830 transitions.

Incomplete random walk after 10000 steps, including 103 resets, run finished after 332 ms. (steps per millisecond=30 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 43) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 43) seen :0

Interrupted probabilistic random walk after 89715 steps, run timeout after 3001 ms. (steps per millisecond=29 ) properties seen :{2=1, 3=1, 10=1, 19=1, 37=1, 40=1, 41=1}

Probabilistic random walk after 89715 steps, saw 85184 distinct states, run finished after 3002 ms. (steps per millisecond=29 ) properties seen :7

Running SMT prover for 36 properties.

// Phase 1: matrix 2152 rows 1081 cols

[2023-03-09 06:06:35] [INFO ] Computed 183 place invariants in 20 ms

[2023-03-09 06:06:36] [INFO ] After 739ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:36

[2023-03-09 06:06:37] [INFO ] [Nat]Absence check using 43 positive place invariants in 24 ms returned sat

[2023-03-09 06:06:37] [INFO ] [Nat]Absence check using 43 positive and 140 generalized place invariants in 73 ms returned sat

[2023-03-09 06:07:01] [INFO ] After 22599ms SMT Verify possible using state equation in natural domain returned unsat :20 sat :14

[2023-03-09 06:07:01] [INFO ] State equation strengthened by 51 read => feed constraints.

java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Failed to assert expression: java.io.IOException: Stream close...

at fr.lip6.move.gal.structural.smt.SMTUtils.execAndCheckResult(SMTUtils.java:251)

at fr.lip6.move.gal.structural.smt.DeadlockTester.verifyPossible(DeadlockTester.java:642)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMTIncremental(DeadlockTester.java:350)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMT(DeadlockTester.java:223)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.applyReductions(ReachabilitySolver.java:95)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.checkAtomicPropositionsLogic(AtomicReducerSR.java:105)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.strongReductions(AtomicReducerSR.java:44)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.preSolveForLogic(LTLPropertySolver.java:176)

at fr.lip6.move.gal.application.Application.startNoEx(Application.java:626)

at fr.lip6.move.gal.application.Application.start(Application.java:178)

at fr.lip6.move.gal.itscl.application.Application.start(Application.java:45)

at org.eclipse.equinox.internal.app.EclipseAppHandle.run(EclipseAppHandle.java:203)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.runApplication(EclipseAppLauncher.java:136)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.start(EclipseAppLauncher.java:104)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:402)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:255)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native Method)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(NativeMethodAccessorImpl.java:77)

at java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

at java.base/java.lang.reflect.Method.invoke(Method.java:568)

at org.eclipse.equinox.launcher.Main.invokeFramework(Main.java:659)

at org.eclipse.equinox.launcher.Main.basicRun(Main.java:596)

at org.eclipse.equinox.launcher.Main.run(Main.java:1467)

at org.eclipse.equinox.launcher.Main.main(Main.java:1440)

[2023-03-09 06:07:01] [WARNING] SMT solver failed with error :SMT solver raised an error when submitting script.... while checking expressions.

[2023-03-09 06:07:01] [INFO ] After 25038ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0 real:36

Fused 36 Parikh solutions to 8 different solutions.

Parikh walk visited 0 properties in 387 ms.

Support contains 59 out of 1081 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1081/1081 places, 2152/2152 transitions.

Drop transitions removed 9 transitions

Trivial Post-agglo rules discarded 9 transitions

Performed 9 trivial Post agglomeration. Transition count delta: 9

Iterating post reduction 0 with 9 rules applied. Total rules applied 9 place count 1081 transition count 2143

Reduce places removed 9 places and 0 transitions.

Iterating post reduction 1 with 9 rules applied. Total rules applied 18 place count 1072 transition count 2143

Performed 2 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 2 Pre rules applied. Total rules applied 18 place count 1072 transition count 2141

Deduced a syphon composed of 2 places in 2 ms

Ensure Unique test removed 1 places

Reduce places removed 3 places and 0 transitions.

Iterating global reduction 2 with 5 rules applied. Total rules applied 23 place count 1069 transition count 2141

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 1 Pre rules applied. Total rules applied 23 place count 1069 transition count 2140

Deduced a syphon composed of 1 places in 7 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 2 with 2 rules applied. Total rules applied 25 place count 1068 transition count 2140

Discarding 3 places :

Symmetric choice reduction at 2 with 3 rule applications. Total rules 28 place count 1065 transition count 2120

Iterating global reduction 2 with 3 rules applied. Total rules applied 31 place count 1065 transition count 2120

Discarding 3 places :

Implicit places reduction removed 3 places

Iterating post reduction 2 with 3 rules applied. Total rules applied 34 place count 1062 transition count 2120

Performed 5 Post agglomeration using F-continuation condition.Transition count delta: 5

Deduced a syphon composed of 5 places in 7 ms

Reduce places removed 5 places and 0 transitions.

Iterating global reduction 3 with 10 rules applied. Total rules applied 44 place count 1057 transition count 2115

Discarding 2 places :

Symmetric choice reduction at 3 with 2 rule applications. Total rules 46 place count 1055 transition count 2113

Iterating global reduction 3 with 2 rules applied. Total rules applied 48 place count 1055 transition count 2113

Free-agglomeration rule applied 4 times.

Iterating global reduction 3 with 4 rules applied. Total rules applied 52 place count 1055 transition count 2109

Reduce places removed 4 places and 0 transitions.

Iterating post reduction 3 with 4 rules applied. Total rules applied 56 place count 1051 transition count 2109

Free-agglomeration rule (complex) applied 1 times.

Iterating global reduction 4 with 1 rules applied. Total rules applied 57 place count 1051 transition count 2108

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 4 with 1 rules applied. Total rules applied 58 place count 1050 transition count 2108

Drop transitions removed 1 transitions

Redundant transition composition rules discarded 1 transitions

Iterating global reduction 5 with 1 rules applied. Total rules applied 59 place count 1050 transition count 2107

Partial Free-agglomeration rule applied 4 times.

Drop transitions removed 4 transitions

Iterating global reduction 5 with 4 rules applied. Total rules applied 63 place count 1050 transition count 2107

Applied a total of 63 rules in 323 ms. Remains 1050 /1081 variables (removed 31) and now considering 2107/2152 (removed 45) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 323 ms. Remains : 1050/1081 places, 2107/2152 transitions.

Incomplete random walk after 10000 steps, including 111 resets, run finished after 349 ms. (steps per millisecond=28 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1000 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 2 ms. (steps per millisecond=500 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 4 ms. (steps per millisecond=250 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Incomplete Best-First random walk after 1001 steps, including 2 resets, run finished after 3 ms. (steps per millisecond=333 ) properties (out of 16) seen :0

Interrupted probabilistic random walk after 158664 steps, run timeout after 3001 ms. (steps per millisecond=52 ) properties seen :{}

Probabilistic random walk after 158664 steps, saw 54702 distinct states, run finished after 3002 ms. (steps per millisecond=52 ) properties seen :0

Running SMT prover for 16 properties.

// Phase 1: matrix 2107 rows 1050 cols

[2023-03-09 06:07:05] [INFO ] Computed 179 place invariants in 18 ms

[2023-03-09 06:07:06] [INFO ] After 510ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:16

[2023-03-09 06:07:06] [INFO ] [Nat]Absence check using 39 positive place invariants in 9 ms returned sat

[2023-03-09 06:07:06] [INFO ] [Nat]Absence check using 39 positive and 140 generalized place invariants in 38 ms returned sat

[2023-03-09 06:07:31] [INFO ] After 24285ms SMT Verify possible using state equation in natural domain returned unsat :1 sat :12

[2023-03-09 06:07:31] [INFO ] State equation strengthened by 59 read => feed constraints.

java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Failed to assert expression: java.io.IOException: Stream close...

at fr.lip6.move.gal.structural.smt.SMTUtils.execAndCheckResult(SMTUtils.java:251)

at fr.lip6.move.gal.structural.smt.DeadlockTester.verifyPossible(DeadlockTester.java:642)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMTIncremental(DeadlockTester.java:350)

at fr.lip6.move.gal.structural.smt.DeadlockTester.testUnreachableWithSMT(DeadlockTester.java:223)

at fr.lip6.move.gal.application.solver.ReachabilitySolver.applyReductions(ReachabilitySolver.java:95)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.checkAtomicPropositionsLogic(AtomicReducerSR.java:105)

at fr.lip6.move.gal.application.solver.logic.AtomicReducerSR.strongReductions(AtomicReducerSR.java:44)

at fr.lip6.move.gal.application.solver.ltl.LTLPropertySolver.preSolveForLogic(LTLPropertySolver.java:176)

at fr.lip6.move.gal.application.Application.startNoEx(Application.java:626)

at fr.lip6.move.gal.application.Application.start(Application.java:178)

at fr.lip6.move.gal.itscl.application.Application.start(Application.java:45)

at org.eclipse.equinox.internal.app.EclipseAppHandle.run(EclipseAppHandle.java:203)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.runApplication(EclipseAppLauncher.java:136)

at org.eclipse.core.runtime.internal.adaptor.EclipseAppLauncher.start(EclipseAppLauncher.java:104)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:402)

at org.eclipse.core.runtime.adaptor.EclipseStarter.run(EclipseStarter.java:255)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native Method)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(NativeMethodAccessorImpl.java:77)

at java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

at java.base/java.lang.reflect.Method.invoke(Method.java:568)

at org.eclipse.equinox.launcher.Main.invokeFramework(Main.java:659)

at org.eclipse.equinox.launcher.Main.basicRun(Main.java:596)

at org.eclipse.equinox.launcher.Main.run(Main.java:1467)

at org.eclipse.equinox.launcher.Main.main(Main.java:1440)

[2023-03-09 06:07:31] [WARNING] SMT solver failed with error :SMT solver raised an error when submitting script.... while checking expressions.

[2023-03-09 06:07:31] [INFO ] After 25022ms SMT Verify possible using all constraints in natural domain returned unsat :0 sat :0 real:16

Fused 16 Parikh solutions to 10 different solutions.

Parikh walk visited 2 properties in 374 ms.

Support contains 55 out of 1050 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1050/1050 places, 2107/2107 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Deduced a syphon composed of 1 places in 3 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 0 with 2 rules applied. Total rules applied 2 place count 1049 transition count 2106

Free-agglomeration rule (complex) applied 1 times.

Iterating global reduction 0 with 1 rules applied. Total rules applied 3 place count 1049 transition count 2105

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 4 place count 1048 transition count 2105

Applied a total of 4 rules in 81 ms. Remains 1048 /1050 variables (removed 2) and now considering 2105/2107 (removed 2) transitions.

Finished structural reductions in REACHABILITY mode , in 1 iterations and 82 ms. Remains : 1048/1050 places, 2105/2107 transitions.

Incomplete random walk after 10000 steps, including 105 resets, run finished after 288 ms. (steps per millisecond=34 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 13 resets, run finished after 41 ms. (steps per millisecond=243 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 11 resets, run finished after 46 ms. (steps per millisecond=217 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10000 steps, including 12 resets, run finished after 45 ms. (steps per millisecond=222 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 49 ms. (steps per millisecond=204 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 9 resets, run finished after 56 ms. (steps per millisecond=178 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 11 resets, run finished after 63 ms. (steps per millisecond=158 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 54 ms. (steps per millisecond=185 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 9 resets, run finished after 48 ms. (steps per millisecond=208 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 49 ms. (steps per millisecond=204 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 52 ms. (steps per millisecond=192 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 11 resets, run finished after 51 ms. (steps per millisecond=196 ) properties (out of 13) seen :1

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 49 ms. (steps per millisecond=204 ) properties (out of 12) seen :0

Incomplete Best-First random walk after 10000 steps, including 10 resets, run finished after 55 ms. (steps per millisecond=181 ) properties (out of 12) seen :0

Interrupted probabilistic random walk after 160217 steps, run timeout after 3001 ms. (steps per millisecond=53 ) properties seen :{}

Probabilistic random walk after 160217 steps, saw 55140 distinct states, run finished after 3001 ms. (steps per millisecond=53 ) properties seen :0

Running SMT prover for 12 properties.

// Phase 1: matrix 2105 rows 1048 cols

[2023-03-09 06:07:35] [INFO ] Computed 179 place invariants in 17 ms

[2023-03-09 06:07:36] [INFO ] After 245ms SMT Verify possible using all constraints in real domain returned unsat :0 sat :0 real:12

[2023-03-09 06:07:36] [INFO ] [Nat]Absence check using 37 positive place invariants in 10 ms returned sat

[2023-03-09 06:07:36] [INFO ] [Nat]Absence check using 37 positive and 142 generalized place invariants in 64 ms returned sat

[2023-03-09 06:07:46] [INFO ] After 10057ms SMT Verify possible using state equation in natural domain returned unsat :5 sat :7

[2023-03-09 06:07:46] [INFO ] State equation strengthened by 59 read => feed constraints.

[2023-03-09 06:07:50] [INFO ] After 3426ms SMT Verify possible using 59 Read/Feed constraints in natural domain returned unsat :5 sat :7

[2023-03-09 06:07:56] [INFO ] After 9646ms SMT Verify possible using trap constraints in natural domain returned unsat :5 sat :7

Attempting to minimize the solution found.

Minimization took 4607 ms.

[2023-03-09 06:08:01] [INFO ] After 25022ms SMT Verify possible using all constraints in natural domain returned unsat :5 sat :6

Fused 12 Parikh solutions to 7 different solutions.

Parikh walk visited 0 properties in 593 ms.

Support contains 39 out of 1048 places. Attempting structural reductions.

Starting structural reductions in REACHABILITY mode, iteration 0 : 1048/1048 places, 2105/2105 transitions.

Discarding 1 places :

Symmetric choice reduction at 0 with 1 rule applications. Total rules 1 place count 1047 transition count 2099

Iterating global reduction 0 with 1 rules applied. Total rules applied 2 place count 1047 transition count 2099

Discarding 1 places :

Implicit places reduction removed 1 places

Iterating post reduction 0 with 1 rules applied. Total rules applied 3 place count 1046 transition count 2099

Performed 3 Post agglomeration using F-continuation condition.Transition count delta: 3

Deduced a syphon composed of 3 places in 3 ms

Reduce places removed 3 places and 0 transitions.

Iterating global reduction 1 with 6 rules applied. Total rules applied 9 place count 1043 transition count 2096

Discarding 1 places :

Symmetric choice reduction at 1 with 1 rule applications. Total rules 10 place count 1042 transition count 2095