About the Execution of 2021-gold for QuasiCertifProtocol-PT-18

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 2728.483 | 1134289.00 | 3014485.00 | 1791.20 | FTFTTTFTTTTTTFFT | normal |

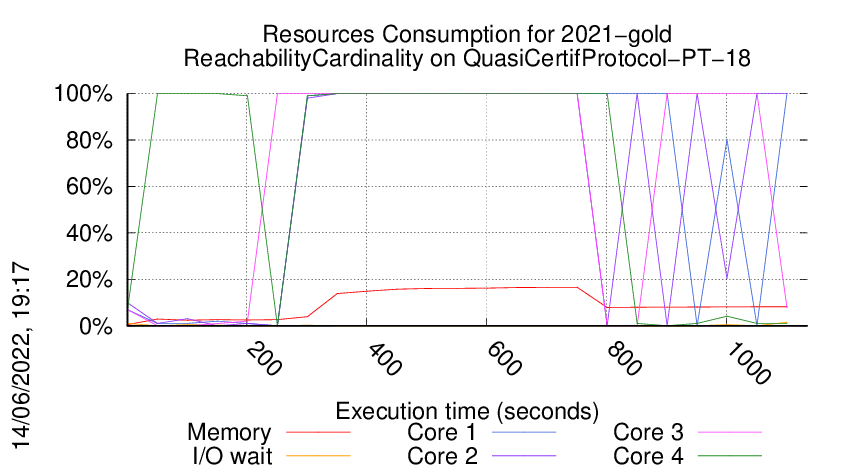

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2022-input.r179-tall-165277027200368.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2022-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.......................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool gold2021

Input is QuasiCertifProtocol-PT-18, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r179-tall-165277027200368

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.6M

-rw-r--r-- 1 mcc users 43K Apr 30 13:31 CTLCardinality.txt

-rw-r--r-- 1 mcc users 295K Apr 30 13:31 CTLCardinality.xml

-rw-r--r-- 1 mcc users 15K Apr 30 13:26 CTLFireability.txt

-rw-r--r-- 1 mcc users 103K Apr 30 13:26 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 10 09:34 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.8K May 10 09:34 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 19K May 9 08:30 LTLCardinality.txt

-rw-r--r-- 1 mcc users 84K May 9 08:30 LTLCardinality.xml

-rw-r--r-- 1 mcc users 6.0K May 9 08:30 LTLFireability.txt

-rw-r--r-- 1 mcc users 30K May 9 08:30 LTLFireability.xml

-rw-r--r-- 1 mcc users 68K Apr 30 13:35 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 468K Apr 30 13:35 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 12K Apr 30 13:32 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 79K Apr 30 13:32 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.6K May 9 08:30 UpperBounds.txt

-rw-r--r-- 1 mcc users 6.5K May 9 08:30 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 10 09:34 equiv_col

-rw-r--r-- 1 mcc users 3 May 10 09:34 instance

-rw-r--r-- 1 mcc users 6 May 10 09:34 iscolored

-rw-r--r-- 1 mcc users 360K May 10 09:34 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-00

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-01

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-02

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-03

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-04

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-05

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-06

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-07

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-08

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-09

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-10

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-11

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-12

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-13

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-14

FORMULA_NAME QuasiCertifProtocol-PT-18-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1655088216922

Running Version 0

[2022-06-13 02:43:38] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -spotpath, /home/mcc/BenchKit/bin//..//ltlfilt, -z3path, /home/mcc/BenchKit/bin//..//z3/bin/z3, -yices2path, /home/mcc/BenchKit/bin//..//yices/bin/yices, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2022-06-13 02:43:38] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2022-06-13 02:43:38] [INFO ] Load time of PNML (sax parser for PT used): 93 ms

[2022-06-13 02:43:38] [INFO ] Transformed 1398 places.

[2022-06-13 02:43:38] [INFO ] Transformed 296 transitions.

[2022-06-13 02:43:38] [INFO ] Parsed PT model containing 1398 places and 296 transitions in 138 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 76 ms.

Working with output stream class java.io.PrintStream

Incomplete random walk after 10000 steps, including 440 resets, run finished after 206 ms. (steps per millisecond=48 ) properties (out of 16) seen :2

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-01 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-00 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 33 resets, run finished after 276 ms. (steps per millisecond=36 ) properties (out of 14) seen :0

Incomplete Best-First random walk after 10001 steps, including 21 resets, run finished after 78 ms. (steps per millisecond=128 ) properties (out of 14) seen :0

Incomplete Best-First random walk after 10001 steps, including 34 resets, run finished after 152 ms. (steps per millisecond=65 ) properties (out of 14) seen :0

Incomplete Best-First random walk after 10001 steps, including 18 resets, run finished after 244 ms. (steps per millisecond=40 ) properties (out of 14) seen :0

Incomplete Best-First random walk after 10001 steps, including 28 resets, run finished after 25 ms. (steps per millisecond=400 ) properties (out of 14) seen :1

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-06 FALSE TECHNIQUES TOPOLOGICAL BESTFIRST_WALK

Incomplete Best-First random walk after 10001 steps, including 12 resets, run finished after 43 ms. (steps per millisecond=232 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 30 resets, run finished after 48 ms. (steps per millisecond=208 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 31 resets, run finished after 20 ms. (steps per millisecond=500 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 34 resets, run finished after 20 ms. (steps per millisecond=500 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 18 resets, run finished after 28 ms. (steps per millisecond=357 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 29 resets, run finished after 34 ms. (steps per millisecond=294 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 32 resets, run finished after 20 ms. (steps per millisecond=500 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 32 resets, run finished after 19 ms. (steps per millisecond=526 ) properties (out of 13) seen :0

Incomplete Best-First random walk after 10001 steps, including 35 resets, run finished after 20 ms. (steps per millisecond=500 ) properties (out of 13) seen :0

Running SMT prover for 13 properties.

// Phase 1: matrix 296 rows 1398 cols

[2022-06-13 02:43:40] [INFO ] Computed 1103 place invariants in 70 ms

[2022-06-13 02:43:40] [INFO ] [Real]Absence check using 3 positive place invariants in 24 ms returned sat

[2022-06-13 02:43:40] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 310 ms returned sat

[2022-06-13 02:43:40] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:43:45] [INFO ] [Real]Absence check using state equation in 4404 ms returned unknown

[2022-06-13 02:43:45] [INFO ] [Real]Absence check using 3 positive place invariants in 13 ms returned sat

[2022-06-13 02:43:45] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 211 ms returned sat

[2022-06-13 02:43:45] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:43:47] [INFO ] [Real]Absence check using state equation in 1851 ms returned sat

[2022-06-13 02:43:47] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:43:47] [INFO ] [Nat]Absence check using 3 positive place invariants in 15 ms returned sat

[2022-06-13 02:43:48] [INFO ] [Nat]Absence check using 3 positive and 1100 generalized place invariants in 230 ms returned sat

[2022-06-13 02:43:48] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2022-06-13 02:43:52] [INFO ] [Nat]Absence check using state equation in 4598 ms returned unknown

[2022-06-13 02:43:52] [INFO ] [Real]Absence check using 3 positive place invariants in 16 ms returned sat

[2022-06-13 02:43:53] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 912 ms returned sat

[2022-06-13 02:43:53] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:43:55] [INFO ] [Real]Absence check using state equation in 1288 ms returned unsat

[2022-06-13 02:43:55] [INFO ] [Real]Absence check using 3 positive place invariants in 20 ms returned sat

[2022-06-13 02:43:55] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 271 ms returned sat

[2022-06-13 02:43:55] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:00] [INFO ] [Real]Absence check using state equation in 4575 ms returned unknown

[2022-06-13 02:44:00] [INFO ] [Real]Absence check using 3 positive place invariants in 13 ms returned unsat

[2022-06-13 02:44:00] [INFO ] [Real]Absence check using 3 positive place invariants in 12 ms returned sat

[2022-06-13 02:44:00] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 291 ms returned sat

[2022-06-13 02:44:00] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:01] [INFO ] [Real]Absence check using state equation in 625 ms returned sat

[2022-06-13 02:44:01] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:44:01] [INFO ] [Nat]Absence check using 3 positive place invariants in 13 ms returned sat

[2022-06-13 02:44:02] [INFO ] [Nat]Absence check using 3 positive and 1100 generalized place invariants in 457 ms returned sat

[2022-06-13 02:44:02] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:03] [INFO ] [Nat]Absence check using state equation in 1864 ms returned sat

[2022-06-13 02:44:04] [INFO ] Computed and/alt/rep : 216/254/216 causal constraints (skipped 60 transitions) in 44 ms.

[2022-06-13 02:44:05] [INFO ] Added : 97 causal constraints over 20 iterations in 1238 ms. Result :sat

Attempting to minimize the solution found.

Minimization took 9 ms.

[2022-06-13 02:44:05] [INFO ] [Real]Absence check using 3 positive place invariants in 14 ms returned sat

[2022-06-13 02:44:05] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 223 ms returned sat

[2022-06-13 02:44:05] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:05] [INFO ] [Real]Absence check using state equation in 73 ms returned unsat

[2022-06-13 02:44:05] [INFO ] [Real]Absence check using 3 positive place invariants in 12 ms returned sat

[2022-06-13 02:44:06] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 207 ms returned sat

[2022-06-13 02:44:06] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:06] [INFO ] [Real]Absence check using state equation in 343 ms returned sat

[2022-06-13 02:44:06] [INFO ] Computed and/alt/rep : 216/254/216 causal constraints (skipped 60 transitions) in 23 ms.

[2022-06-13 02:44:07] [INFO ] Added : 80 causal constraints over 16 iterations in 847 ms. Result :sat

Attempting to minimize the solution found.

Minimization took 6 ms.

[2022-06-13 02:44:07] [INFO ] [Real]Absence check using 3 positive place invariants in 12 ms returned sat

[2022-06-13 02:44:07] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 219 ms returned sat

[2022-06-13 02:44:07] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:08] [INFO ] [Real]Absence check using state equation in 439 ms returned unsat

[2022-06-13 02:44:08] [INFO ] [Real]Absence check using 3 positive place invariants in 13 ms returned sat

[2022-06-13 02:44:08] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 319 ms returned sat

[2022-06-13 02:44:08] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:10] [INFO ] [Real]Absence check using state equation in 2042 ms returned unsat

[2022-06-13 02:44:11] [INFO ] [Real]Absence check using 3 positive place invariants in 14 ms returned sat

[2022-06-13 02:44:11] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 216 ms returned sat

[2022-06-13 02:44:11] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:11] [INFO ] [Real]Absence check using state equation in 234 ms returned unsat

[2022-06-13 02:44:11] [INFO ] [Real]Absence check using 3 positive place invariants in 11 ms returned sat

[2022-06-13 02:44:11] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 209 ms returned sat

[2022-06-13 02:44:11] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:12] [INFO ] [Real]Absence check using state equation in 370 ms returned sat

[2022-06-13 02:44:12] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:44:12] [INFO ] [Nat]Absence check using 3 positive place invariants in 11 ms returned sat

[2022-06-13 02:44:12] [INFO ] [Nat]Absence check using 3 positive and 1100 generalized place invariants in 176 ms returned sat

[2022-06-13 02:44:12] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:12] [INFO ] [Nat]Absence check using state equation in 352 ms returned sat

[2022-06-13 02:44:13] [INFO ] Computed and/alt/rep : 216/254/216 causal constraints (skipped 60 transitions) in 33 ms.

[2022-06-13 02:44:13] [INFO ] Added : 79 causal constraints over 16 iterations in 862 ms. Result :sat

Attempting to minimize the solution found.

Minimization took 11 ms.

[2022-06-13 02:44:14] [INFO ] [Real]Absence check using 3 positive place invariants in 19 ms returned sat

[2022-06-13 02:44:14] [INFO ] [Real]Absence check using 3 positive and 1100 generalized place invariants in 196 ms returned sat

[2022-06-13 02:44:14] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:44:14] [INFO ] [Real]Absence check using state equation in 80 ms returned unsat

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-15 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-13 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-12 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-11 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-09 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-07 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-04 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 13 Parikh solutions to 4 different solutions.

Incomplete Parikh walk after 14100 steps, including 147 resets, run finished after 249 ms. (steps per millisecond=56 ) properties (out of 6) seen :4 could not realise parikh vector

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-14 FALSE TECHNIQUES TOPOLOGICAL PARIKH_WALK

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-10 TRUE TECHNIQUES TOPOLOGICAL PARIKH_WALK

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-08 TRUE TECHNIQUES TOPOLOGICAL PARIKH_WALK

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-05 TRUE TECHNIQUES TOPOLOGICAL PARIKH_WALK

Incomplete Parikh walk after 12200 steps, including 164 resets, run finished after 198 ms. (steps per millisecond=61 ) properties (out of 2) seen :0 could not realise parikh vector

Incomplete Parikh walk after 8400 steps, including 120 resets, run finished after 130 ms. (steps per millisecond=64 ) properties (out of 2) seen :0 could not realise parikh vector

Support contains 978 out of 1398 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 1398/1398 places, 296/296 transitions.

Graph (complete) has 9608 edges and 1398 vertex of which 1378 are kept as prefixes of interest. Removing 20 places using SCC suffix rule.36 ms

Discarding 20 places :

Also discarding 0 output transitions

Applied a total of 1 rules in 155 ms. Remains 1378 /1398 variables (removed 20) and now considering 296/296 (removed 0) transitions.

Finished structural reductions, in 1 iterations. Remains : 1378/1398 places, 296/296 transitions.

[2022-06-13 02:44:15] [INFO ] Flatten gal took : 164 ms

[2022-06-13 02:44:15] [INFO ] Flatten gal took : 77 ms

[2022-06-13 02:44:15] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality9551722109815055574.gal : 26 ms

[2022-06-13 02:44:15] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality554346518459595832.prop : 5 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality9551722109815055574.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality554346518459595832.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality9551722109815055574.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality554346518459595832.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality554346518459595832.prop.

SDD proceeding with computation,2 properties remain. new max is 4

SDD size :1 after 4

SDD proceeding with computation,2 properties remain. new max is 8

SDD size :4 after 8

SDD proceeding with computation,2 properties remain. new max is 16

SDD size :8 after 16

SDD proceeding with computation,2 properties remain. new max is 32

SDD size :16 after 1024

SDD proceeding with computation,2 properties remain. new max is 64

SDD size :1024 after 354522

SDD proceeding with computation,2 properties remain. new max is 128

SDD size :709044 after 724070

SDD proceeding with computation,2 properties remain. new max is 256

SDD size :724070 after 796162

SDD proceeding with computation,2 properties remain. new max is 512

SDD size :796162 after 796431

SDD proceeding with computation,2 properties remain. new max is 1024

SDD size :796431 after 1.44914e+06

SDD proceeding with computation,2 properties remain. new max is 2048

SDD size :1.44914e+06 after 3.11595e+06

SDD proceeding with computation,2 properties remain. new max is 4096

SDD size :3.11595e+06 after 6.02682e+06

SDD proceeding with computation,2 properties remain. new max is 8192

SDD size :6.02682e+06 after 2.25647e+07

SDD proceeding with computation,2 properties remain. new max is 16384

SDD size :2.25647e+07 after 1.77856e+08

SDD proceeding with computation,2 properties remain. new max is 32768

SDD size :1.77856e+08 after 6.36911e+08

SDD proceeding with computation,2 properties remain. new max is 65536

SDD size :6.36911e+08 after 2.28804e+09

SDD proceeding with computation,2 properties remain. new max is 131072

SDD size :2.28804e+09 after 5.55777e+09

Detected timeout of ITS tools.

[2022-06-13 02:44:30] [INFO ] Flatten gal took : 68 ms

[2022-06-13 02:44:30] [INFO ] Applying decomposition

[2022-06-13 02:44:30] [INFO ] Flatten gal took : 80 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/convert-linux64, -i, /tmp/graph13212864151082232191.txt, -o, /tmp/graph13212864151082232191.bin, -w, /tmp/graph13212864151082232191.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/louvain-linux64, /tmp/graph13212864151082232191.bin, -l, -1, -v, -w, /tmp/graph13212864151082232191.weights, -q, 0, -e, 0.001], workingDir=null]

[2022-06-13 02:44:32] [INFO ] Decomposing Gal with order

[2022-06-13 02:44:32] [INFO ] Rewriting arrays to variables to allow decomposition.

[2022-06-13 02:44:32] [INFO ] Removed a total of 320 redundant transitions.

[2022-06-13 02:44:32] [INFO ] Flatten gal took : 230 ms

[2022-06-13 02:44:32] [INFO ] Fuse similar labels procedure discarded/fused a total of 57 labels/synchronizations in 20 ms.

[2022-06-13 02:44:32] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality12212908580148690768.gal : 13 ms

[2022-06-13 02:44:32] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality8016614985829041460.prop : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality12212908580148690768.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality8016614985829041460.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality12212908580148690768.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality8016614985829041460.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality8016614985829041460.prop.

SDD proceeding with computation,2 properties remain. new max is 4

SDD size :1 after 256

SDD proceeding with computation,2 properties remain. new max is 8

SDD size :256 after 512

SDD proceeding with computation,2 properties remain. new max is 16

SDD size :512 after 1024

SDD proceeding with computation,2 properties remain. new max is 32

SDD size :1024 after 2047

SDD proceeding with computation,2 properties remain. new max is 64

SDD size :2047 after 43022

SDD proceeding with computation,2 properties remain. new max is 128

SDD size :43022 after 64844

Detected timeout of ITS tools.

Built C files in :

/tmp/ltsmin274414991432412233

[2022-06-13 02:44:47] [INFO ] Built C files in 30ms conformant to PINS (ltsmin variant)in folder :/tmp/ltsmin274414991432412233

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin274414991432412233]

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin274414991432412233] killed by timeout after 1 SECONDS

java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin274414991432412233] killed by timeout after 1 SECONDS

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:79)

at java.base/java.lang.Thread.run(Thread.java:834)

Incomplete random walk after 1000000 steps, including 44202 resets, run finished after 12670 ms. (steps per millisecond=78 ) properties (out of 2) seen :0

Interrupted Best-First random walk after 191749 steps, including 593 resets, run timeout after 5001 ms. (steps per millisecond=38 ) properties seen :{}

Interrupted Best-First random walk after 843192 steps, including 1796 resets, run timeout after 5001 ms. (steps per millisecond=168 ) properties seen :{}

Interrupted probabilistic random walk after 7941963 steps, run timeout after 30001 ms. (steps per millisecond=264 ) properties seen :{}

Probabilistic random walk after 7941963 steps, saw 1004128 distinct states, run finished after 30002 ms. (steps per millisecond=264 ) properties seen :{}

Running SMT prover for 2 properties.

// Phase 1: matrix 296 rows 1378 cols

[2022-06-13 02:45:41] [INFO ] Computed 1083 place invariants in 32 ms

[2022-06-13 02:45:41] [INFO ] [Real]Absence check using 2 positive place invariants in 16 ms returned sat

[2022-06-13 02:45:42] [INFO ] [Real]Absence check using 2 positive and 1081 generalized place invariants in 291 ms returned sat

[2022-06-13 02:45:42] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:45:47] [INFO ] [Real]Absence check using state equation in 5746 ms returned sat

[2022-06-13 02:45:47] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:45:48] [INFO ] [Nat]Absence check using 2 positive place invariants in 14 ms returned sat

[2022-06-13 02:45:51] [INFO ] [Nat]Absence check using 2 positive and 1081 generalized place invariants in 3334 ms returned sat

[2022-06-13 02:45:51] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2022-06-13 02:45:57] [INFO ] [Nat]Absence check using state equation in 6067 ms returned unknown

[2022-06-13 02:45:57] [INFO ] [Real]Absence check using 2 positive place invariants in 12 ms returned sat

[2022-06-13 02:45:57] [INFO ] [Real]Absence check using 2 positive and 1081 generalized place invariants in 257 ms returned sat

[2022-06-13 02:45:57] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:46:00] [INFO ] [Real]Absence check using state equation in 2634 ms returned sat

[2022-06-13 02:46:00] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:46:00] [INFO ] [Nat]Absence check using 2 positive place invariants in 12 ms returned sat

[2022-06-13 02:46:00] [INFO ] [Nat]Absence check using 2 positive and 1081 generalized place invariants in 237 ms returned sat

[2022-06-13 02:46:00] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2022-06-13 02:46:02] [INFO ] [Nat]Absence check using state equation in 1319 ms returned unsat

FORMULA QuasiCertifProtocol-PT-18-ReachabilityCardinality-03 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 2 Parikh solutions to 1 different solutions.

Support contains 918 out of 1378 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 1378/1378 places, 296/296 transitions.

Graph (complete) has 9584 edges and 1378 vertex of which 1377 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.13 ms

Discarding 1 places :

Also discarding 0 output transitions

Drop transitions removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 0 with 1 rules applied. Total rules applied 2 place count 1377 transition count 295

Applied a total of 2 rules in 55 ms. Remains 1377 /1378 variables (removed 1) and now considering 295/296 (removed 1) transitions.

Finished structural reductions, in 1 iterations. Remains : 1377/1378 places, 295/296 transitions.

[2022-06-13 02:46:02] [INFO ] Flatten gal took : 40 ms

[2022-06-13 02:46:02] [INFO ] Flatten gal took : 38 ms

[2022-06-13 02:46:02] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality17071105962707543634.gal : 6 ms

[2022-06-13 02:46:02] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality7951770797197124518.prop : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality17071105962707543634.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality7951770797197124518.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality17071105962707543634.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality7951770797197124518.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality7951770797197124518.prop.

SDD proceeding with computation,1 properties remain. new max is 4

SDD size :1 after 2

SDD proceeding with computation,1 properties remain. new max is 8

SDD size :2 after 8

SDD proceeding with computation,1 properties remain. new max is 16

SDD size :8 after 64

SDD proceeding with computation,1 properties remain. new max is 32

SDD size :64 after 30827

SDD proceeding with computation,1 properties remain. new max is 64

SDD size :709044 after 908184

SDD proceeding with computation,1 properties remain. new max is 128

SDD size :908184 after 1.00056e+06

SDD proceeding with computation,1 properties remain. new max is 256

SDD size :1.00056e+06 after 1.06258e+06

SDD proceeding with computation,1 properties remain. new max is 512

SDD size :1.06258e+06 after 1.53478e+06

SDD proceeding with computation,1 properties remain. new max is 1024

SDD size :1.53478e+06 after 1.7723e+06

SDD proceeding with computation,1 properties remain. new max is 2048

SDD size :1.7723e+06 after 3.03525e+06

SDD proceeding with computation,1 properties remain. new max is 4096

SDD size :3.03525e+06 after 5.71514e+06

SDD proceeding with computation,1 properties remain. new max is 8192

SDD size :5.71514e+06 after 1.12351e+07

SDD proceeding with computation,1 properties remain. new max is 16384

SDD size :1.12351e+07 after 3.57891e+07

SDD proceeding with computation,1 properties remain. new max is 32768

SDD size :3.57891e+07 after 7.46331e+07

Detected timeout of ITS tools.

[2022-06-13 02:46:17] [INFO ] Flatten gal took : 42 ms

[2022-06-13 02:46:17] [INFO ] Applying decomposition

[2022-06-13 02:46:17] [INFO ] Flatten gal took : 36 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/convert-linux64, -i, /tmp/graph8164482433703496539.txt, -o, /tmp/graph8164482433703496539.bin, -w, /tmp/graph8164482433703496539.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/louvain-linux64, /tmp/graph8164482433703496539.bin, -l, -1, -v, -w, /tmp/graph8164482433703496539.weights, -q, 0, -e, 0.001], workingDir=null]

[2022-06-13 02:46:18] [INFO ] Decomposing Gal with order

[2022-06-13 02:46:18] [INFO ] Rewriting arrays to variables to allow decomposition.

[2022-06-13 02:46:18] [INFO ] Removed a total of 169 redundant transitions.

[2022-06-13 02:46:18] [INFO ] Flatten gal took : 99 ms

[2022-06-13 02:46:18] [INFO ] Fuse similar labels procedure discarded/fused a total of 19 labels/synchronizations in 8 ms.

[2022-06-13 02:46:18] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality15413850194091117230.gal : 6 ms

[2022-06-13 02:46:18] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality8186966151076349643.prop : 1 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality15413850194091117230.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality8186966151076349643.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality15413850194091117230.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality8186966151076349643.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality8186966151076349643.prop.

SDD proceeding with computation,1 properties remain. new max is 4

SDD size :1 after 8

SDD proceeding with computation,1 properties remain. new max is 8

SDD size :8 after 16

SDD proceeding with computation,1 properties remain. new max is 16

SDD size :16 after 32

SDD proceeding with computation,1 properties remain. new max is 32

SDD size :32 after 128

SDD proceeding with computation,1 properties remain. new max is 64

SDD size :128 after 2047

SDD proceeding with computation,1 properties remain. new max is 128

SDD size :2047 after 354522

SDD proceeding with computation,1 properties remain. new max is 256

SDD size :354522 after 3.03563e+06

SDD proceeding with computation,1 properties remain. new max is 512

SDD size :3.03563e+06 after 1.79368e+07

SDD proceeding with computation,1 properties remain. new max is 1024

SDD size :1.79368e+07 after 4.68107e+08

Detected timeout of ITS tools.

Built C files in :

/tmp/ltsmin10991779921004138798

[2022-06-13 02:46:33] [INFO ] Built C files in 17ms conformant to PINS (ltsmin variant)in folder :/tmp/ltsmin10991779921004138798

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin10991779921004138798]

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin10991779921004138798] killed by timeout after 1 SECONDS

java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin10991779921004138798] killed by timeout after 1 SECONDS

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:79)

at java.base/java.lang.Thread.run(Thread.java:834)

Incomplete random walk after 1000000 steps, including 44170 resets, run finished after 11271 ms. (steps per millisecond=88 ) properties (out of 1) seen :0

Interrupted Best-First random walk after 194190 steps, including 611 resets, run timeout after 5001 ms. (steps per millisecond=38 ) properties seen :{}

Interrupted probabilistic random walk after 8449528 steps, run timeout after 30001 ms. (steps per millisecond=281 ) properties seen :{}

Probabilistic random walk after 8449528 steps, saw 1063909 distinct states, run finished after 30001 ms. (steps per millisecond=281 ) properties seen :{}

Running SMT prover for 1 properties.

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:47:21] [INFO ] Computed 1083 place invariants in 30 ms

[2022-06-13 02:47:21] [INFO ] [Real]Absence check using 2 positive place invariants in 14 ms returned sat

[2022-06-13 02:47:21] [INFO ] [Real]Absence check using 2 positive and 1081 generalized place invariants in 278 ms returned sat

[2022-06-13 02:47:21] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:47:23] [INFO ] [Real]Absence check using state equation in 2082 ms returned sat

[2022-06-13 02:47:23] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:47:23] [INFO ] [Nat]Absence check using 2 positive place invariants in 12 ms returned sat

[2022-06-13 02:47:30] [INFO ] SMT solver returned unknown. Retrying;

[2022-06-13 02:47:33] [INFO ] [Nat]Absence check using 2 positive and 1081 generalized place invariants in 9092 ms returned unknown

Support contains 918 out of 1377 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 1377/1377 places, 295/295 transitions.

Applied a total of 0 rules in 39 ms. Remains 1377 /1377 variables (removed 0) and now considering 295/295 (removed 0) transitions.

Finished structural reductions, in 1 iterations. Remains : 1377/1377 places, 295/295 transitions.

Starting structural reductions, iteration 0 : 1377/1377 places, 295/295 transitions.

Applied a total of 0 rules in 20 ms. Remains 1377 /1377 variables (removed 0) and now considering 295/295 (removed 0) transitions.

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:47:33] [INFO ] Computed 1083 place invariants in 14 ms

[2022-06-13 02:47:33] [INFO ] Implicit Places using invariants in 808 ms returned []

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:47:33] [INFO ] Computed 1083 place invariants in 18 ms

[2022-06-13 02:47:35] [INFO ] Implicit Places using invariants and state equation in 1339 ms returned []

Implicit Place search using SMT with State Equation took 2174 ms to find 0 implicit places.

[2022-06-13 02:47:35] [INFO ] Redundant transitions in 17 ms returned []

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:47:35] [INFO ] Computed 1083 place invariants in 14 ms

[2022-06-13 02:47:35] [INFO ] Dead Transitions using invariants and state equation in 481 ms returned []

Finished structural reductions, in 1 iterations. Remains : 1377/1377 places, 295/295 transitions.

Incomplete random walk after 100000 steps, including 4421 resets, run finished after 1333 ms. (steps per millisecond=75 ) properties (out of 1) seen :0

Running SMT prover for 1 properties.

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:47:37] [INFO ] Computed 1083 place invariants in 21 ms

[2022-06-13 02:47:37] [INFO ] [Real]Absence check using 2 positive place invariants in 33 ms returned sat

[2022-06-13 02:47:37] [INFO ] [Real]Absence check using 2 positive and 1081 generalized place invariants in 280 ms returned sat

[2022-06-13 02:47:37] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:47:39] [INFO ] [Real]Absence check using state equation in 2230 ms returned sat

[2022-06-13 02:47:39] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:47:40] [INFO ] [Nat]Absence check using 2 positive place invariants in 14 ms returned sat

[2022-06-13 02:47:46] [INFO ] SMT solver returned unknown. Retrying;

[2022-06-13 02:47:49] [INFO ] [Nat]Absence check using 2 positive and 1081 generalized place invariants in 9101 ms returned unknown

[2022-06-13 02:47:49] [INFO ] Flatten gal took : 39 ms

[2022-06-13 02:47:49] [INFO ] Flatten gal took : 40 ms

[2022-06-13 02:47:49] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality11146105162546100799.gal : 5 ms

[2022-06-13 02:47:49] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality15253534042154466758.prop : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality11146105162546100799.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality15253534042154466758.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality11146105162546100799.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality15253534042154466758.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality15253534042154466758.prop.

SDD proceeding with computation,1 properties remain. new max is 4

SDD size :1 after 2

SDD proceeding with computation,1 properties remain. new max is 8

SDD size :2 after 8

SDD proceeding with computation,1 properties remain. new max is 16

SDD size :8 after 64

SDD proceeding with computation,1 properties remain. new max is 32

SDD size :64 after 30827

SDD proceeding with computation,1 properties remain. new max is 64

SDD size :709044 after 908184

SDD proceeding with computation,1 properties remain. new max is 128

SDD size :908184 after 1.00056e+06

SDD proceeding with computation,1 properties remain. new max is 256

SDD size :1.00056e+06 after 1.06258e+06

SDD proceeding with computation,1 properties remain. new max is 512

SDD size :1.06258e+06 after 1.53478e+06

SDD proceeding with computation,1 properties remain. new max is 1024

SDD size :1.53478e+06 after 1.7723e+06

SDD proceeding with computation,1 properties remain. new max is 2048

SDD size :1.7723e+06 after 3.03525e+06

SDD proceeding with computation,1 properties remain. new max is 4096

SDD size :3.03525e+06 after 5.71514e+06

SDD proceeding with computation,1 properties remain. new max is 8192

SDD size :5.71514e+06 after 1.12351e+07

SDD proceeding with computation,1 properties remain. new max is 16384

SDD size :1.12351e+07 after 3.57891e+07

SDD proceeding with computation,1 properties remain. new max is 32768

SDD size :3.57891e+07 after 7.46331e+07

SDD proceeding with computation,1 properties remain. new max is 65536

Detected timeout of ITS tools.

[2022-06-13 02:48:04] [INFO ] Flatten gal took : 40 ms

[2022-06-13 02:48:04] [INFO ] Applying decomposition

[2022-06-13 02:48:04] [INFO ] Flatten gal took : 34 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/convert-linux64, -i, /tmp/graph11076080801318911506.txt, -o, /tmp/graph11076080801318911506.bin, -w, /tmp/graph11076080801318911506.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/louvain-linux64, /tmp/graph11076080801318911506.bin, -l, -1, -v, -w, /tmp/graph11076080801318911506.weights, -q, 0, -e, 0.001], workingDir=null]

[2022-06-13 02:48:05] [INFO ] Decomposing Gal with order

[2022-06-13 02:48:05] [INFO ] Rewriting arrays to variables to allow decomposition.

[2022-06-13 02:48:05] [INFO ] Removed a total of 169 redundant transitions.

[2022-06-13 02:48:05] [INFO ] Flatten gal took : 92 ms

[2022-06-13 02:48:05] [INFO ] Fuse similar labels procedure discarded/fused a total of 38 labels/synchronizations in 8 ms.

[2022-06-13 02:48:05] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality6956235365308432983.gal : 5 ms

[2022-06-13 02:48:05] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality13098027052821310897.prop : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality6956235365308432983.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality13098027052821310897.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality6956235365308432983.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality13098027052821310897.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality13098027052821310897.prop.

SDD proceeding with computation,1 properties remain. new max is 4

SDD size :1 after 8

SDD proceeding with computation,1 properties remain. new max is 8

SDD size :8 after 16

SDD proceeding with computation,1 properties remain. new max is 16

SDD size :16 after 32

SDD proceeding with computation,1 properties remain. new max is 32

SDD size :32 after 128

SDD proceeding with computation,1 properties remain. new max is 64

SDD size :128 after 2047

SDD proceeding with computation,1 properties remain. new max is 128

SDD size :2047 after 354522

SDD proceeding with computation,1 properties remain. new max is 256

SDD size :354522 after 3.03563e+06

SDD proceeding with computation,1 properties remain. new max is 512

SDD size :3.03563e+06 after 1.79368e+07

SDD proceeding with computation,1 properties remain. new max is 1024

SDD size :1.79368e+07 after 3.84667e+08

SDD proceeding with computation,1 properties remain. new max is 2048

SDD size :3.84667e+08 after 6.62028e+11

Detected timeout of ITS tools.

Built C files in :

/tmp/ltsmin868484183643281166

[2022-06-13 02:48:20] [INFO ] Built C files in 16ms conformant to PINS (ltsmin variant)in folder :/tmp/ltsmin868484183643281166

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin868484183643281166]

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin868484183643281166] killed by timeout after 1 SECONDS

java.lang.RuntimeException: Compilation or link of executable timed out.java.util.concurrent.TimeoutException: Subprocess running CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin868484183643281166] killed by timeout after 1 SECONDS

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:79)

at java.base/java.lang.Thread.run(Thread.java:834)

Applied a total of 0 rules in 42 ms. Remains 1377 /1377 variables (removed 0) and now considering 295/295 (removed 0) transitions.

Running SMT prover for 1 properties.

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:48:21] [INFO ] Computed 1083 place invariants in 13 ms

[2022-06-13 02:48:22] [INFO ] [Real]Absence check using 2 positive place invariants in 41 ms returned sat

[2022-06-13 02:48:22] [INFO ] [Real]Absence check using 2 positive and 1081 generalized place invariants in 277 ms returned sat

[2022-06-13 02:48:22] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2022-06-13 02:48:24] [INFO ] [Real]Absence check using state equation in 2240 ms returned sat

[2022-06-13 02:48:24] [INFO ] Solution in real domain found non-integer solution.

[2022-06-13 02:48:24] [INFO ] [Nat]Absence check using 2 positive place invariants in 15 ms returned sat

[2022-06-13 02:48:30] [INFO ] SMT solver returned unknown. Retrying;

[2022-06-13 02:48:33] [INFO ] [Nat]Absence check using 2 positive and 1081 generalized place invariants in 9092 ms returned unknown

[2022-06-13 02:48:33] [INFO ] Flatten gal took : 37 ms

Using solver Z3 to compute partial order matrices.

Built C files in :

/tmp/ltsmin9741383426598185016

[2022-06-13 02:48:34] [INFO ] Computing symmetric may disable matrix : 295 transitions.

[2022-06-13 02:48:34] [INFO ] Computation of Complete disable matrix. took 4 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2022-06-13 02:48:34] [INFO ] Computing symmetric may enable matrix : 295 transitions.

[2022-06-13 02:48:34] [INFO ] Computation of Complete enable matrix. took 3 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2022-06-13 02:48:34] [INFO ] Applying decomposition

[2022-06-13 02:48:34] [INFO ] Flatten gal took : 33 ms

[2022-06-13 02:48:34] [INFO ] Computing Do-Not-Accords matrix : 295 transitions.

[2022-06-13 02:48:34] [INFO ] Computation of Completed DNA matrix. took 16 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2022-06-13 02:48:34] [INFO ] Flatten gal took : 132 ms

[2022-06-13 02:48:34] [INFO ] Input system was already deterministic with 295 transitions.

[2022-06-13 02:48:34] [INFO ] Built C files in 218ms conformant to PINS (ltsmin variant)in folder :/tmp/ltsmin9741383426598185016

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.ltsmin.binaries_1.0.0.202104292328/bin/include/, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/tmp/ltsmin9741383426598185016]

[2022-06-13 02:48:35] [INFO ] Ran tautology test, simplified 0 / 1 in 1236 ms.

[2022-06-13 02:48:35] [INFO ] BMC solution for property QuasiCertifProtocol-PT-18-ReachabilityCardinality-02(UNSAT) depth K=0 took 168 ms

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 295 rows 1377 cols

[2022-06-13 02:48:35] [INFO ] Computed 1083 place invariants in 86 ms

inv : n7_3_10 - n7_3_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n7_17_2 - n7_17_16 + n8_17_2 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n9_10_7 - n9_10_18 + CstopOK_7 - CstopOK_18 = 0

inv : n7_17_6 - n7_17_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : n9_1_12 - n9_1_18 + CstopOK_12 - CstopOK_18 = 0

inv : n8_5_2 - n8_17_2 - n8_4_15 + n8_17_15 - n8_5_16 + n8_4_16 = 0

inv : n8_6_7 - n8_18_7 - n8_4_15 + n8_18_15 - n8_6_16 + n8_4_16 = 0

inv : n7_14_4 - n7_14_16 + n8_0_4 - n8_0_16 = 0

inv : n7_12_18 - n7_12_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_10_2 - n8_17_2 - n8_10_15 + n8_17_15 = 0

inv : n7_0_1 - n7_0_17 + n8_0_1 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n9_4_9 - n9_4_18 + CstopOK_9 - CstopOK_18 = 0

inv : n7_15_3 - n7_15_16 + n8_4_3 - n8_4_16 = 0

inv : -n1_0 + n1_10 + n2_10 - n2_0 = 0

inv : n6_9 - n5_18 + n5_9 - n6_18 = 0

inv : n9_4_0 + CstopOK_0 - n9_4_18 - CstopOK_18 = 0

inv : n7_0_3 - n7_0_17 + n8_4_3 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : n9_10_2 + CstopOK_2 - n9_10_18 - CstopOK_18 = 0

inv : n8_1_0 - n8_0_0 - n8_1_16 + n8_0_16 = 0

inv : n7_15_14 - n7_15_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : -n1_0 + n2_14 + n1_14 - n2_0 = 0

inv : n9_13_1 + CstopOK_1 - n9_13_17 - CstopOK_17 = 0

inv : Cstart_8 - Cstart_10 - n8_11_10 + n8_15_8 + n8_11_15 - n8_15_15 = 0

inv : n8_3_13 - n8_18_13 - n8_4_15 + n8_18_15 - n8_3_16 + n8_4_16 = 0

inv : n9_1_13 - n9_1_18 + CstopOK_13 - CstopOK_18 = 0

inv : malicious_reservoir + CstopAbort + SstopAbort = 10

inv : n9_4_6 - n9_4_18 + CstopOK_6 - CstopOK_18 = 0

inv : n8_10_1 - n8_0_1 + n8_4_15 - n8_10_15 + n8_0_16 - n8_4_16 = 0

inv : n7_1_10 - n7_1_17 + n8_11_10 - n8_15_17 - n8_11_15 + n8_15_15 = 0

inv : n8_9_18 - n8_18_18 - n8_9_15 + n8_18_15 = 0

inv : n9_3_16 - n9_3_18 - CstopOK_18 + CstopOK_16 = 0

inv : n9_9_9 - n9_9_18 + CstopOK_9 - CstopOK_18 = 0

inv : n8_16_4 - n8_0_4 + n8_4_15 - n8_16_15 + n8_0_16 - n8_4_16 = 0

inv : n7_5_5 - n7_5_16 + n8_4_5 - n8_4_16 = 0

inv : n8_18_6 - n8_12_6 + n8_12_15 - n8_18_15 = 0

inv : n7_6_15 - n7_6_16 + n8_4_15 - n8_4_16 = 0

inv : -n1_0 + n1_13 + n2_13 - n2_0 = 0

inv : n9_7_1 + CstopOK_1 - n9_7_18 - CstopOK_18 = 0

inv : n8_14_17 - n8_15_17 - n8_14_15 + n8_15_15 = 0

inv : n8_12_8 - n8_15_8 - n8_12_15 + n8_15_15 = 0

inv : n7_6_13 - n7_6_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_1_13 - n8_18_13 - n8_4_15 - n8_1_16 + n8_18_15 + n8_4_16 = 0

inv : n7_5_18 - n7_5_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_11_1 - n7_11_16 + n8_0_1 - n8_0_16 = 0

inv : n9_18_9 - n9_18_17 + CstopOK_9 - CstopOK_17 = 0

inv : n8_9_10 - n8_11_10 - n8_9_15 + n8_11_15 = 0

inv : n8_5_7 - n8_18_7 - n8_4_15 + n8_18_15 - n8_5_16 + n8_4_16 = 0

inv : n7_0_14 - n7_0_17 - n8_15_17 + n8_17_14 - n8_17_15 + n8_15_15 = 0

inv : n9_6_13 - n9_6_18 + CstopOK_13 - CstopOK_18 = 0

inv : n9_15_3 + CstopOK_3 - n9_15_17 - CstopOK_17 = 0

inv : n9_0_12 - n9_0_18 + CstopOK_12 - CstopOK_18 = 0

inv : n9_9_14 - n9_9_18 - CstopOK_18 + CstopOK_14 = 0

inv : n9_17_6 - n9_17_17 + CstopOK_6 - CstopOK_17 = 0

inv : n7_13_0 - n7_13_16 + n8_0_0 - n8_0_16 = 0

inv : n7_15_11 - n7_15_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n9_3_3 + CstopOK_3 - n9_3_18 - CstopOK_18 = 0

inv : Cstart_5 - Cstart_10 + n8_4_5 - n8_11_10 - n8_4_15 + n8_11_15 = 0

inv : n8_6_13 - n8_18_13 - n8_4_15 + n8_18_15 - n8_6_16 + n8_4_16 = 0

inv : n7_0_12 - n7_0_17 + n8_4_12 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : n9_0_17 - n9_0_18 - CstopOK_18 + CstopOK_17 = 0

inv : n7_12_11 - n7_12_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n8_8_8 - n8_15_8 - n8_8_15 + n8_15_15 = 0

inv : n7_13_6 - n7_13_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : n7_10_6 - n7_10_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : Cstart_15 - Cstart_10 - n8_11_10 + n8_11_15 = 0

inv : n8_17_0 - n8_0_0 + n8_4_15 - n8_17_15 + n8_0_16 - n8_4_16 = 0

inv : n8_6_2 - n8_17_2 - n8_4_15 + n8_17_15 - n8_6_16 + n8_4_16 = 0

inv : n9_11_16 - n9_11_18 - CstopOK_18 + CstopOK_16 = 0

inv : n7_3_9 - n7_3_16 + n8_0_9 - n8_0_16 = 0

inv : n7_8_17 - n7_8_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n9_17_2 + CstopOK_2 - n9_17_17 - CstopOK_17 = 0

inv : n9_2_7 - n9_2_18 + CstopOK_7 - CstopOK_18 = 0

inv : n9_2_12 - n9_2_18 + CstopOK_12 - CstopOK_18 = 0

inv : n7_14_10 - n7_14_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n8_9_6 - n8_12_6 - n8_9_15 + n8_12_15 = 0

inv : n8_11_12 - n8_4_12 + n8_4_15 - n8_11_15 = 0

inv : n9_9_6 - n9_9_18 + CstopOK_6 - CstopOK_18 = 0

inv : n8_9_16 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n9_14_14 - n9_14_17 + CstopOK_14 - CstopOK_17 = 0

inv : n9_13_3 + CstopOK_3 - n9_13_17 - CstopOK_17 = 0

inv : n8_14_0 - n8_0_0 + n8_4_15 - n8_14_15 + n8_0_16 - n8_4_16 = 0

inv : n7_4_18 - n7_4_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_8_10 - n8_11_10 - n8_8_15 + n8_11_15 = 0

inv : -n8_4_5 + n8_7_5 + n8_4_15 - n8_7_15 = 0

inv : n9_10_8 - n9_10_18 + CstopOK_8 - CstopOK_18 = 0

inv : n9_13_6 - n9_13_17 + CstopOK_6 - CstopOK_17 = 0

inv : n7_10_12 - n7_10_16 + n8_4_12 - n8_4_16 = 0

inv : n9_1_3 + CstopOK_3 - n9_1_18 - CstopOK_18 = 0

inv : n3_2 - n3_4 + n4_2 - n4_4 = 0

inv : n8_11_1 - n8_0_1 + n8_4_15 - n8_11_15 + n8_0_16 - n8_4_16 = 0

inv : n1_5 - n1_0 + n2_5 - n2_0 = 0

inv : n8_18_17 - n8_15_17 + n8_15_15 - n8_18_15 = 0

inv : n8_16_10 - n8_11_10 + n8_11_15 - n8_16_15 = 0

inv : n6_10 - n5_18 + n5_10 - n6_18 = 0

inv : n9_13_9 - n9_13_17 + CstopOK_9 - CstopOK_17 = 0

inv : n9_6_7 - n9_6_18 + CstopOK_7 - CstopOK_18 = 0

inv : n9_0_3 + CstopOK_3 - n9_0_18 - CstopOK_18 = 0

inv : n9_6_10 - n9_6_18 + CstopOK_10 - CstopOK_18 = 0

inv : n9_0_2 + CstopOK_2 - n9_0_18 - CstopOK_18 = 0

inv : n8_11_4 - n8_0_4 + n8_4_15 - n8_11_15 + n8_0_16 - n8_4_16 = 0

inv : n6_0 - n5_18 - n6_18 + n5_0 = 0

inv : n8_18_9 - n8_0_9 + n8_4_15 - n8_18_15 + n8_0_16 - n8_4_16 = 0

inv : n7_7_5 - n7_7_16 + n8_4_5 - n8_4_16 = 0

inv : n8_14_14 - n8_17_14 + n8_17_15 - n8_14_15 = 0

inv : n9_14_4 + CstopOK_4 - n9_14_17 - CstopOK_17 = 0

inv : n8_3_7 - n8_18_7 - n8_4_15 + n8_18_15 - n8_3_16 + n8_4_16 = 0

inv : n8_9_7 - n8_18_7 - n8_9_15 + n8_18_15 = 0

inv : n8_13_17 - n8_15_17 - n8_13_15 + n8_15_15 = 0

inv : n9_8_0 + CstopOK_0 - n9_8_18 - CstopOK_18 = 0

inv : n7_10_2 - n7_10_16 + n8_17_2 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n8_6_3 - n8_4_3 - n8_6_16 + n8_4_16 = 0

inv : n7_3_14 - n7_3_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : -n8_4_3 + n8_3_3 - n8_3_16 + n8_4_16 = 0

inv : -n8_0_1 + n8_1_1 - n8_1_16 + n8_0_16 = 0

inv : n8_9_14 - n8_17_14 - n8_9_15 + n8_17_15 = 0

inv : n8_12_14 - n8_17_14 - n8_12_15 + n8_17_15 = 0

inv : n7_5_6 - n7_5_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : n9_5_10 - n9_5_18 + CstopOK_10 - CstopOK_18 = 0

inv : n7_4_8 - n7_4_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_10_5 - n7_10_16 + n8_4_5 - n8_4_16 = 0

inv : n7_13_13 - n7_13_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n9_2_9 - n9_2_18 + CstopOK_9 - CstopOK_18 = 0

inv : n7_5_8 - n7_5_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n8_15_18 - n8_18_18 - n8_15_15 + n8_18_15 = 0

inv : n9_18_14 - n9_18_17 + CstopOK_14 - CstopOK_17 = 0

inv : n7_1_0 - n7_1_17 + n8_0_0 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n8_10_17 - n8_15_17 - n8_10_15 + n8_15_15 = 0

inv : n7_4_7 - n7_4_16 + n8_18_7 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : -n8_4_15 + n8_3_15 - n8_3_16 + n8_4_16 = 0

inv : n7_7_8 - n7_7_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n9_0_6 - n9_0_18 + CstopOK_6 - CstopOK_18 = 0

inv : n8_17_10 - n8_11_10 + n8_11_15 - n8_17_15 = 0

inv : n9_6_17 - n9_6_18 - CstopOK_18 + CstopOK_17 = 0

inv : Cstart_0 + n8_0_0 - Cstart_10 - n8_11_10 - n8_4_15 + n8_11_15 - n8_0_16 + n8_4_16 = 0

inv : n8_6_0 - n8_0_0 + n8_0_16 - n8_6_16 = 0

inv : n7_9_12 - n7_9_16 + n8_4_12 - n8_4_16 = 0

inv : n7_6_10 - n7_6_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n7_8_5 - n7_8_16 + n8_4_5 - n8_4_16 = 0

inv : n8_14_13 - n8_18_13 - n8_14_15 + n8_18_15 = 0

inv : n9_17_8 - n9_17_17 + CstopOK_8 - CstopOK_17 = 0

inv : n7_17_18 - n7_17_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n9_16_2 + CstopOK_2 - n9_16_17 - CstopOK_17 = 0

inv : n8_13_1 - n8_0_1 + n8_4_15 - n8_13_15 + n8_0_16 - n8_4_16 = 0

inv : n9_2_11 - n9_2_18 + CstopOK_11 - CstopOK_18 = 0

inv : n8_18_12 - n8_4_12 + n8_4_15 - n8_18_15 = 0

inv : n8_16_7 - n8_18_7 - n8_16_15 + n8_18_15 = 0

inv : n3_3 - n3_4 + n4_3 - n4_4 = 0

inv : n8_11_13 - n8_18_13 - n8_11_15 + n8_18_15 = 0

inv : n7_10_0 - n7_10_16 + n8_0_0 - n8_0_16 = 0

inv : n8_1_3 - n8_4_3 - n8_1_16 + n8_4_16 = 0

inv : n6_1 - n5_18 - n6_18 + n5_1 = 0

inv : n7_2_18 - n7_2_17 - n8_15_17 + n8_18_18 + n8_15_15 - n8_18_15 = 0

inv : n7_15_10 - n7_15_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n8_1_6 - n8_12_6 - n8_4_15 + n8_12_15 - n8_1_16 + n8_4_16 = 0

inv : n7_2_7 - n7_2_17 + n8_18_7 - n8_15_17 + n8_15_15 - n8_18_15 = 0

inv : n8_3_18 - n8_18_18 - n8_4_15 + n8_18_15 - n8_3_16 + n8_4_16 = 0

inv : n7_15_15 - n7_15_16 + n8_4_15 - n8_4_16 = 0

inv : n9_12_3 + CstopOK_3 - n9_12_17 - CstopOK_17 = 0

inv : n8_12_17 - n8_15_17 - n8_12_15 + n8_15_15 = 0

inv : n8_4_10 - n8_11_10 - n8_4_15 + n8_11_15 = 0

inv : n9_3_2 + CstopOK_2 - n9_3_18 - CstopOK_18 = 0

inv : n9_3_14 - n9_3_18 - CstopOK_18 + CstopOK_14 = 0

inv : n7_14_9 - n7_14_16 + n8_0_9 - n8_0_16 = 0

inv : n8_10_18 - n8_18_18 - n8_10_15 + n8_18_15 = 0

inv : n9_6_5 + CstopOK_5 - n9_6_18 - CstopOK_18 = 0

inv : n8_17_18 - n8_18_18 - n8_17_15 + n8_18_15 = 0

inv : n9_11_5 + CstopOK_5 - n9_11_18 - CstopOK_18 = 0

inv : -n8_4_5 + n8_6_5 - n8_6_16 + n8_4_16 = 0

inv : n7_16_8 - n7_16_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_12_14 - n7_12_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n7_18_7 - n7_18_16 + n8_18_7 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_10_10 - n8_11_10 - n8_10_15 + n8_11_15 = 0

inv : n9_5_2 + CstopOK_2 - n9_5_18 - CstopOK_18 = 0

inv : n8_2_17 - n8_15_17 - n8_4_15 + n8_15_15 - n8_2_16 + n8_4_16 = 0

inv : n9_14_10 - n9_14_17 + CstopOK_10 - CstopOK_17 = 0

inv : n8_2_2 - n8_17_2 - n8_4_15 + n8_17_15 - n8_2_16 + n8_4_16 = 0

inv : n7_1_11 - n7_1_17 + n8_9_11 - n8_15_17 - n8_9_15 + n8_15_15 = 0

inv : n9_16_14 - n9_16_17 + CstopOK_14 - CstopOK_17 = 0

inv : n8_16_16 + n8_4_15 - n8_16_15 - n8_4_16 = 0

inv : n7_6_17 - n7_6_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_9_17 - n7_9_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n9_4_16 - n9_4_18 - CstopOK_18 + CstopOK_16 = 0

inv : n9_3_4 + CstopOK_4 - n9_3_18 - CstopOK_18 = 0

inv : n7_7_3 - n7_7_16 + n8_4_3 - n8_4_16 = 0

inv : n8_2_5 - n8_4_5 - n8_2_16 + n8_4_16 = 0

inv : n9_5_15 - n9_5_18 - CstopOK_18 + CstopOK_15 = 0

inv : n7_0_7 - n7_0_17 + n8_18_7 - n8_15_17 + n8_15_15 - n8_18_15 = 0

inv : n9_10_0 + CstopOK_0 - n9_10_18 - CstopOK_18 = 0

inv : n7_13_11 - n7_13_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n7_1_6 - n7_1_17 + n8_12_6 - n8_15_17 - n8_12_15 + n8_15_15 = 0

inv : n8_6_12 - n8_4_12 - n8_6_16 + n8_4_16 = 0

inv : n8_1_18 - n8_18_18 - n8_4_15 - n8_1_16 + n8_18_15 + n8_4_16 = 0

inv : n7_13_4 - n7_13_16 + n8_0_4 - n8_0_16 = 0

inv : n9_3_0 + CstopOK_0 - n9_3_18 - CstopOK_18 = 0

inv : n9_7_6 - n9_7_18 + CstopOK_6 - CstopOK_18 = 0

inv : n9_18_18 - n9_18_17 + CstopOK_18 - CstopOK_17 = 0

inv : n9_13_11 - n9_13_17 + CstopOK_11 - CstopOK_17 = 0

inv : n8_10_8 - n8_15_8 - n8_10_15 + n8_15_15 = 0

inv : n7_9_13 - n7_9_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_17_5 - n7_17_16 + n8_4_5 - n8_4_16 = 0

inv : n7_8_14 - n7_8_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n7_11_4 - n7_11_16 + n8_0_4 - n8_0_16 = 0

inv : n8_15_3 - n8_4_3 + n8_4_15 - n8_15_15 = 0

inv : n8_7_1 - n8_0_1 + n8_4_15 - n8_7_15 + n8_0_16 - n8_4_16 = 0

inv : n8_11_7 - n8_18_7 - n8_11_15 + n8_18_15 = 0

inv : n7_1_1 - n7_1_17 + n8_0_1 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n9_12_9 - n9_12_17 + CstopOK_9 - CstopOK_17 = 0

inv : n8_16_17 - n8_15_17 - n8_16_15 + n8_15_15 = 0

inv : n9_6_16 - n9_6_18 - CstopOK_18 + CstopOK_16 = 0

inv : n8_5_9 - n8_0_9 + n8_0_16 - n8_5_16 = 0

inv : n7_3_0 - n7_3_16 + n8_0_0 - n8_0_16 = 0

inv : n7_6_9 - n7_6_16 + n8_0_9 - n8_0_16 = 0

inv : n9_11_7 - n9_11_18 + CstopOK_7 - CstopOK_18 = 0

inv : n6_3 - n5_18 + n5_3 - n6_18 = 0

inv : n8_8_1 - n8_0_1 + n8_4_15 - n8_8_15 + n8_0_16 - n8_4_16 = 0

inv : n8_16_1 - n8_0_1 + n8_4_15 - n8_16_15 + n8_0_16 - n8_4_16 = 0

inv : n7_18_3 - n7_18_16 + n8_4_3 - n8_4_16 = 0

inv : n8_14_10 - n8_11_10 + n8_11_15 - n8_14_15 = 0

inv : n7_2_0 - n7_2_17 + n8_0_0 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n9_14_12 - n9_14_17 + CstopOK_12 - CstopOK_17 = 0

inv : n7_11_15 - n7_11_16 + n8_4_15 - n8_4_16 = 0

inv : n7_1_8 - n7_1_17 + n8_15_8 - n8_15_17 = 0

inv : n9_2_10 - n9_2_18 + CstopOK_10 - CstopOK_18 = 0

inv : n7_0_5 - n7_0_17 + n8_4_5 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : n9_2_14 - n9_2_18 - CstopOK_18 + CstopOK_14 = 0

inv : n7_1_2 - n7_1_17 + n8_17_2 - n8_15_17 - n8_17_15 + n8_15_15 = 0

inv : n8_0_6 - n8_12_6 - n8_4_15 + n8_12_15 - n8_0_16 + n8_4_16 = 0

inv : n7_14_18 - n7_14_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_12_0 - n7_12_16 + n8_0_0 - n8_0_16 = 0

inv : n8_2_12 - n8_4_12 - n8_2_16 + n8_4_16 = 0

inv : n1_2 - n1_0 + n2_2 - n2_0 = 0

inv : n9_1_11 - n9_1_18 + CstopOK_11 - CstopOK_18 = 0

inv : n8_4_11 - n8_9_11 - n8_4_15 + n8_9_15 = 0

inv : n7_11_9 - n7_11_16 + n8_0_9 - n8_0_16 = 0

inv : n9_12_16 - n9_12_17 + CstopOK_16 - CstopOK_17 = 0

inv : n8_4_1 - n8_0_1 + n8_0_16 - n8_4_16 = 0

inv : n7_8_12 - n7_8_16 + n8_4_12 - n8_4_16 = 0

inv : n8_14_3 - n8_4_3 + n8_4_15 - n8_14_15 = 0

inv : n9_15_0 + CstopOK_0 - n9_15_17 - CstopOK_17 = 0

inv : n7_11_6 - n7_11_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : n8_5_18 - n8_18_18 - n8_4_15 + n8_18_15 - n8_5_16 + n8_4_16 = 0

inv : n7_16_18 - n7_16_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_4_11 - n7_4_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n8_11_2 - n8_17_2 - n8_11_15 + n8_17_15 = 0

inv : n8_13_9 - n8_0_9 + n8_4_15 - n8_13_15 + n8_0_16 - n8_4_16 = 0

inv : n9_4_13 - n9_4_18 + CstopOK_13 - CstopOK_18 = 0

inv : n9_11_17 - n9_11_18 - CstopOK_18 + CstopOK_17 = 0

inv : n7_7_11 - n7_7_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n8_16_0 - n8_0_0 + n8_4_15 - n8_16_15 + n8_0_16 - n8_4_16 = 0

inv : n8_3_9 - n8_0_9 + n8_0_16 - n8_3_16 = 0

inv : n7_1_4 - n7_1_17 + n8_0_4 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n8_4_0 - n8_0_0 + n8_0_16 - n8_4_16 = 0

inv : n9_15_2 + CstopOK_2 - n9_15_17 - CstopOK_17 = 0

inv : n9_9_4 + CstopOK_4 - n9_9_18 - CstopOK_18 = 0

inv : n8_2_0 - n8_0_0 - n8_2_16 + n8_0_16 = 0

inv : n8_11_8 - n8_15_8 - n8_11_15 + n8_15_15 = 0

inv : n9_18_13 - n9_18_17 + CstopOK_13 - CstopOK_17 = 0

inv : n7_13_1 - n7_13_16 + n8_0_1 - n8_0_16 = 0

inv : n7_11_8 - n7_11_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_16_7 - n7_16_16 + n8_18_7 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n9_4_11 - n9_4_18 + CstopOK_11 - CstopOK_18 = 0

inv : n9_14_9 - n9_14_17 + CstopOK_9 - CstopOK_17 = 0

inv : n8_7_0 - n8_0_0 + n8_4_15 - n8_7_15 + n8_0_16 - n8_4_16 = 0

inv : n9_5_7 - n9_5_18 + CstopOK_7 - CstopOK_18 = 0

inv : n7_2_3 - n7_2_17 + n8_4_3 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : n8_17_13 - n8_18_13 - n8_17_15 + n8_18_15 = 0

inv : n9_15_7 - n9_15_17 + CstopOK_7 - CstopOK_17 = 0

inv : n7_14_17 - n7_14_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_17_9 - n7_17_16 + n8_0_9 - n8_0_16 = 0

inv : -n3_4 + n4_15 - n4_4 + n3_15 = 0

inv : n7_14_5 - n7_14_16 + n8_4_5 - n8_4_16 = 0

inv : -n1_0 + n1_8 + n2_8 - n2_0 = 0

inv : n7_13_3 - n7_13_16 + n8_4_3 - n8_4_16 = 0

inv : n8_4_18 - n8_18_18 - n8_4_15 + n8_18_15 = 0

inv : n7_5_10 - n7_5_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n7_13_15 - n7_13_16 + n8_4_15 - n8_4_16 = 0

inv : n9_11_0 + CstopOK_0 - n9_11_18 - CstopOK_18 = 0

inv : n9_11_15 - n9_11_18 - CstopOK_18 + CstopOK_15 = 0

inv : n7_16_15 - n7_16_16 + n8_4_15 - n8_4_16 = 0

inv : n7_0_2 - n7_0_17 + n8_17_2 - n8_15_17 - n8_17_15 + n8_15_15 = 0

inv : n8_1_12 - n8_4_12 - n8_1_16 + n8_4_16 = 0

inv : n9_12_5 + CstopOK_5 - n9_12_17 - CstopOK_17 = 0

inv : n6_4 - n5_18 + n5_4 - n6_18 = 0

inv : n7_11_13 - n7_11_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : -n1_0 + n2_15 + n1_15 - n2_0 = 0

inv : n8_8_3 - n8_4_3 + n8_4_15 - n8_8_15 = 0

inv : n9_3_10 - n9_3_18 + CstopOK_10 - CstopOK_18 = 0

inv : n8_15_6 - n8_12_6 + n8_12_15 - n8_15_15 = 0

inv : n8_12_5 - n8_4_5 + n8_4_15 - n8_12_15 = 0

inv : n9_2_3 + CstopOK_3 - n9_2_18 - CstopOK_18 = 0

inv : n7_17_14 - n7_17_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n8_4_17 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : Cstart_4 - Cstart_10 + n8_0_4 - n8_11_10 - n8_4_15 + n8_11_15 - n8_0_16 + n8_4_16 = 0

inv : n9_18_11 - n9_18_17 + CstopOK_11 - CstopOK_17 = 0

inv : n7_6_7 - n7_6_16 + n8_18_7 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_6_14 - n7_6_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n8_8_7 - n8_18_7 - n8_8_15 + n8_18_15 = 0

inv : n9_3_6 - n9_3_18 + CstopOK_6 - CstopOK_18 = 0

inv : n7_8_15 - n7_8_16 + n8_4_15 - n8_4_16 = 0

inv : n7_6_11 - n7_6_16 + n8_9_11 + n8_4_15 - n8_9_15 - n8_4_16 = 0

inv : n9_2_1 + CstopOK_1 - n9_2_18 - CstopOK_18 = 0

inv : n9_12_15 - n9_12_17 + CstopOK_15 - CstopOK_17 = 0

inv : n9_17_13 - n9_17_17 + CstopOK_13 - CstopOK_17 = 0

inv : Cstart_9 - Cstart_10 - n8_11_10 + n8_0_9 - n8_4_15 + n8_11_15 - n8_0_16 + n8_4_16 = 0

inv : n9_16_0 + CstopOK_0 - n9_16_17 - CstopOK_17 = 0

inv : n6_7 - n5_18 + n5_7 - n6_18 = 0

inv : n8_15_16 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n9_0_5 + CstopOK_5 - n9_0_18 - CstopOK_18 = 0

inv : n9_8_3 + CstopOK_3 - n9_8_18 - CstopOK_18 = 0

inv : n7_6_8 - n7_6_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n9_3_15 - n9_3_18 - CstopOK_18 + CstopOK_15 = 0

inv : n9_15_4 + CstopOK_4 - n9_15_17 - CstopOK_17 = 0

inv : n8_0_11 - n8_9_11 - n8_4_15 + n8_9_15 - n8_0_16 + n8_4_16 = 0

inv : n8_1_15 - n8_4_15 - n8_1_16 + n8_4_16 = 0

inv : n8_1_8 - n8_15_8 - n8_4_15 + n8_15_15 - n8_1_16 + n8_4_16 = 0

inv : n9_5_16 - n9_5_18 - CstopOK_18 + CstopOK_16 = 0

inv : -n8_9_11 + n8_7_11 + n8_9_15 - n8_7_15 = 0

inv : n8_12_13 - n8_18_13 - n8_12_15 + n8_18_15 = 0

inv : n9_0_16 - n9_0_18 - CstopOK_18 + CstopOK_16 = 0

inv : n7_8_2 - n7_8_16 + n8_17_2 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n8_13_16 + n8_4_15 - n8_13_15 - n8_4_16 = 0

inv : n8_11_9 - n8_0_9 + n8_4_15 - n8_11_15 + n8_0_16 - n8_4_16 = 0

inv : n9_18_16 - n9_18_17 + CstopOK_16 - CstopOK_17 = 0

inv : n9_5_11 - n9_5_18 + CstopOK_11 - CstopOK_18 = 0

inv : n9_18_1 + CstopOK_1 - n9_18_17 - CstopOK_17 = 0

inv : n7_2_12 - n7_2_17 + n8_4_12 - n8_15_17 - n8_4_15 + n8_15_15 = 0

inv : n7_13_7 - n7_13_16 + n8_18_7 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n7_3_15 - n7_3_16 + n8_4_15 - n8_4_16 = 0

inv : n8_13_2 - n8_17_2 - n8_13_15 + n8_17_15 = 0

inv : n7_13_14 - n7_13_16 + n8_17_14 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n8_12_11 - n8_9_11 + n8_9_15 - n8_12_15 = 0

inv : n8_6_17 - n8_15_17 - n8_4_15 + n8_15_15 - n8_6_16 + n8_4_16 = 0

inv : n9_14_2 + CstopOK_2 - n9_14_17 - CstopOK_17 = 0

inv : n9_10_10 - n9_10_18 + CstopOK_10 - CstopOK_18 = 0

inv : n8_1_11 - n8_9_11 - n8_4_15 + n8_9_15 - n8_1_16 + n8_4_16 = 0

inv : n9_14_0 + CstopOK_0 - n9_14_17 - CstopOK_17 = 0

inv : n9_16_3 + CstopOK_3 - n9_16_17 - CstopOK_17 = 0

inv : n8_0_3 - n8_4_3 - n8_0_16 + n8_4_16 = 0

inv : n8_7_7 - n8_18_7 - n8_7_15 + n8_18_15 = 0

inv : Cstart_16 - Cstart_10 - n8_11_10 - n8_4_15 + n8_11_15 + n8_4_16 = 0

inv : n7_7_6 - n7_7_16 + n8_12_6 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : Cstart_6 - Cstart_10 - n8_11_10 + n8_12_6 - n8_12_15 + n8_11_15 = 0

inv : n7_7_4 - n7_7_16 + n8_0_4 - n8_0_16 = 0

inv : n9_15_8 - n9_15_17 + CstopOK_8 - CstopOK_17 = 0

inv : n9_7_5 + CstopOK_5 - n9_7_18 - CstopOK_18 = 0

inv : n7_11_3 - n7_11_16 + n8_4_3 - n8_4_16 = 0

inv : n9_6_2 + CstopOK_2 - n9_6_18 - CstopOK_18 = 0

inv : n9_12_11 - n9_12_17 + CstopOK_11 - CstopOK_17 = 0

inv : s6_1 + s6_0 + s6_3 + s6_2 + s6_5 + s6_4 + s6_7 + s6_6 + s6_10 + s6_11 + s6_8 + s6_9 + s6_14 + s6_15 + s6_12 + s6_13 + s6_18 + SstopAbort + s6_16 + s6_17 + s5_2 + s5_3 + s5_0 + s5_1 + s5_7 + s5_6 + s5_5 + s5_4 + s5_11 + s5_10 + s5_9 + s5_8 + s5_15 + s5_14 + s5_13 + s5_12 + s4_0 + s5_18 + s5_17 + s5_16 + s4_5 + s4_6 + s4_7 + s4_8 + s4_1 + s4_2 + s4_3 + s4_4 + s4_13 + s4_14 + s4_15 + s4_16 + s4_9 + s4_10 + s4_11 + s4_12 + s3_3 + s3_2 + s3_5 + s3_4 + s4_18 + s4_17 + s3_1 + s3_0 + s3_11 + s3_10 + s3_13 + s3_12 + s3_7 + s3_6 + s3_9 + s3_8 + s2_1 + s2_2 + s3_18 + s2_0 + s3_16 + s3_17 + s3_14 + s3_15 + s2_9 + s2_10 + s2_7 + s2_8 + s2_5 + s2_6 + s2_3 + s2_4 + s2_18 + s2_17 + s2_16 + s2_15 + s2_14 + s2_13 + s2_12 + s2_11 + Sstart_7 + Sstart_6 + Sstart_5 + Sstart_4 + Sstart_3 + Sstart_2 + Sstart_1 + Sstart_0 + Sstart_17 + Sstart_16 + Sstart_18 + Sstart_9 + Sstart_8 + Sstart_11 + Sstart_10 + Sstart_13 + Sstart_12 + Sstart_15 + Sstart_14 + n9_9_18 + n9_10_18 + n9_11_18 + n9_6_18 + n9_5_18 + n9_8_18 + n9_7_18 + n9_2_18 + n9_1_18 + n9_4_18 + n9_3_18 + n9_17_17 + n9_16_17 + n9_0_18 + n9_18_17 + n9_13_17 + n9_12_17 + n9_15_17 + n9_14_17 + 12*CstopOK_18 + 7*CstopOK_17 = 19

inv : n9_0_15 - n9_0_18 - CstopOK_18 + CstopOK_15 = 0

inv : n8_3_14 - n8_17_14 - n8_4_15 + n8_17_15 - n8_3_16 + n8_4_16 = 0

inv : n7_18_9 - n7_18_16 + n8_0_9 - n8_0_16 = 0

inv : n7_9_10 - n7_9_16 + n8_11_10 + n8_4_15 - n8_11_15 - n8_4_16 = 0

inv : n9_9_8 - n9_9_18 + CstopOK_8 - CstopOK_18 = 0

inv : n9_11_14 - n9_11_18 - CstopOK_18 + CstopOK_14 = 0

inv : n7_10_17 - n7_10_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n8_11_14 - n8_17_14 - n8_11_15 + n8_17_15 = 0

inv : n8_12_16 + n8_4_15 - n8_12_15 - n8_4_16 = 0

inv : n7_17_4 - n7_17_16 + n8_0_4 - n8_0_16 = 0

inv : n9_13_12 - n9_13_17 + CstopOK_12 - CstopOK_17 = 0

inv : n7_18_8 - n7_18_16 + n8_15_8 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n8_0_17 - n8_15_17 - n8_4_15 + n8_15_15 - n8_0_16 + n8_4_16 = 0

inv : n9_18_3 + CstopOK_3 - n9_18_17 - CstopOK_17 = 0

inv : n8_18_14 - n8_17_14 + n8_17_15 - n8_18_15 = 0

inv : n8_16_3 - n8_4_3 + n8_4_15 - n8_16_15 = 0

inv : n9_12_12 - n9_12_17 + CstopOK_12 - CstopOK_17 = 0

inv : n9_1_7 - n9_1_18 + CstopOK_7 - CstopOK_18 = 0

inv : n9_8_12 - n9_8_18 + CstopOK_12 - CstopOK_18 = 0

inv : n7_14_3 - n7_14_16 + n8_4_3 - n8_4_16 = 0

inv : n7_18_12 - n7_18_16 + n8_4_12 - n8_4_16 = 0

inv : n9_16_12 - n9_16_17 + CstopOK_12 - CstopOK_17 = 0

inv : n9_5_6 - n9_5_18 + CstopOK_6 - CstopOK_18 = 0

inv : n7_12_13 - n7_12_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n9_10_16 - n9_10_18 - CstopOK_18 + CstopOK_16 = 0

inv : n9_14_18 - n9_14_17 + CstopOK_18 - CstopOK_17 = 0

inv : n8_4_8 - n8_15_8 - n8_4_15 + n8_15_15 = 0

inv : n7_14_0 - n7_14_16 + n8_0_0 - n8_0_16 = 0

inv : Cstart_3 - Cstart_10 + n8_4_3 - n8_11_10 - n8_4_15 + n8_11_15 = 0

inv : n8_3_6 - n8_12_6 - n8_4_15 + n8_12_15 - n8_3_16 + n8_4_16 = 0

inv : n9_12_13 - n9_12_17 + CstopOK_13 - CstopOK_17 = 0

inv : n8_0_12 - n8_4_12 - n8_0_16 + n8_4_16 = 0

inv : n9_4_10 - n9_4_18 + CstopOK_10 - CstopOK_18 = 0

inv : n7_3_4 - n7_3_16 + n8_0_4 - n8_0_16 = 0

inv : n8_7_10 - n8_11_10 - n8_7_15 + n8_11_15 = 0

inv : n9_2_0 + CstopOK_0 - n9_2_18 - CstopOK_18 = 0

inv : n8_3_17 - n8_15_17 - n8_4_15 + n8_15_15 - n8_3_16 + n8_4_16 = 0

inv : n7_18_13 - n7_18_16 + n8_18_13 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_14_11 - n8_9_11 + n8_9_15 - n8_14_15 = 0

inv : n7_16_0 - n7_16_16 + n8_0_0 - n8_0_16 = 0

inv : n7_11_18 - n7_11_16 + n8_18_18 + n8_4_15 - n8_18_15 - n8_4_16 = 0

inv : n8_12_18 - n8_18_18 - n8_12_15 + n8_18_15 = 0

inv : n7_11_17 - n7_11_16 + n8_15_17 + n8_4_15 - n8_15_15 - n8_4_16 = 0

inv : n7_15_1 - n7_15_16 + n8_0_1 - n8_0_16 = 0

inv : n9_17_4 + CstopOK_4 - n9_17_17 - CstopOK_17 = 0

inv : n8_8_9 - n8_0_9 + n8_4_15 - n8_8_15 + n8_0_16 - n8_4_16 = 0

inv : n9_9_15 - n9_9_18 - CstopOK_18 + CstopOK_15 = 0

inv : n8_1_2 - n8_17_2 - n8_4_15 + n8_17_15 - n8_1_16 + n8_4_16 = 0

inv : n9_10_6 - n9_10_18 + CstopOK_6 - CstopOK_18 = 0

inv : n9_10_13 - n9_10_18 + CstopOK_13 - CstopOK_18 = 0

inv : n9_1_5 + CstopOK_5 - n9_1_18 - CstopOK_18 = 0

inv : n9_7_17 - n9_7_18 - CstopOK_18 + CstopOK_17 = 0

inv : n9_17_16 - n9_17_17 + CstopOK_16 - CstopOK_17 = 0

inv : n7_3_2 - n7_3_16 + n8_17_2 + n8_4_15 - n8_17_15 - n8_4_16 = 0

inv : n9_10_17 - n9_10_18 - CstopOK_18 + CstopOK_17 = 0

inv : n9_18_8 - n9_18_17 + CstopOK_8 - CstopOK_17 = 0

inv : n8_17_6 - n8_12_6 + n8_12_15 - n8_17_15 = 0

inv : n9_17_11 - n9_17_17 + CstopOK_11 - CstopOK_17 = 0

inv : n8_0_13 - n8_18_13 - n8_4_15 + n8_18_15 - n8_0_16 + n8_4_16 = 0

inv : n8_14_16 + n8_4_15 - n8_14_15 - n8_4_16 = 0

inv : -n3_4 + n4_17 + n3_17 - n4_4 = 0

inv : n8_3_11 - n8_9_11 - n8_4_15 + n8_9_15 - n8_3_16 + n8_4_16 = 0

inv : n7_16_2 - n7_16_16 + n8_17_2 + n8_4_15 - n8_17_15 - n8_4_16 = 0