About the Execution of Tapaal for BART-COL-040

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 16222.336 | 3592648.00 | 8540576.00 | 2846.20 | F??TFTTF?FF??FF? | normal |

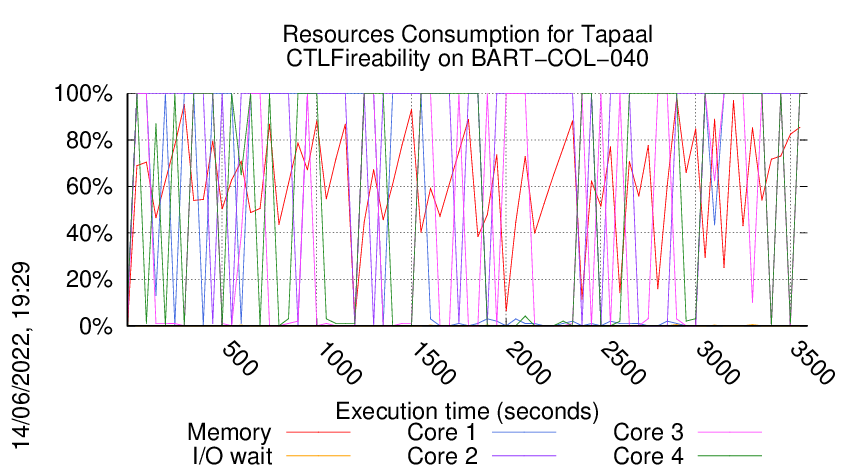

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2022-input.r003-tajo-165245683100570.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2022-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

.................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool tapaal

Input is BART-COL-040, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r003-tajo-165245683100570

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 440K

-rw-r--r-- 1 mcc users 7.8K Apr 29 21:49 CTLCardinality.txt

-rw-r--r-- 1 mcc users 77K Apr 29 21:49 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.6K Apr 29 20:17 CTLFireability.txt

-rw-r--r-- 1 mcc users 48K Apr 29 20:17 CTLFireability.xml

-rw-r--r-- 1 mcc users 5 May 10 09:33 equiv_pt

-rw-r--r-- 1 mcc users 4.2K May 10 09:33 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K May 10 09:33 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4 May 10 09:33 instance

-rw-r--r-- 1 mcc users 5 May 10 09:33 iscolored

-rw-r--r-- 1 mcc users 3.7K May 9 07:06 LTLCardinality.txt

-rw-r--r-- 1 mcc users 24K May 9 07:06 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.4K May 9 07:06 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K May 9 07:06 LTLFireability.xml

-rw-r--r-- 1 mcc users 207K May 10 09:33 model.pnml

-rw-r--r-- 1 mcc users 1.6K May 9 07:06 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 9 07:06 UpperBounds.xml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME BART-COL-040-CTLFireability-00

FORMULA_NAME BART-COL-040-CTLFireability-01

FORMULA_NAME BART-COL-040-CTLFireability-02

FORMULA_NAME BART-COL-040-CTLFireability-03

FORMULA_NAME BART-COL-040-CTLFireability-04

FORMULA_NAME BART-COL-040-CTLFireability-05

FORMULA_NAME BART-COL-040-CTLFireability-06

FORMULA_NAME BART-COL-040-CTLFireability-07

FORMULA_NAME BART-COL-040-CTLFireability-08

FORMULA_NAME BART-COL-040-CTLFireability-09

FORMULA_NAME BART-COL-040-CTLFireability-10

FORMULA_NAME BART-COL-040-CTLFireability-11

FORMULA_NAME BART-COL-040-CTLFireability-12

FORMULA_NAME BART-COL-040-CTLFireability-13

FORMULA_NAME BART-COL-040-CTLFireability-14

FORMULA_NAME BART-COL-040-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1652564615081

tapaal

Got BK_BIN_PATH=/home/mcc/BenchKit/bin/

---> tapaal --- TAPAAL v5

Setting MODEL_PATH=.

Setting VERIFYPN=/home/mcc/BenchKit/bin/verifypn

Got BK_TIME_CONFINEMENT=3600

Setting TEMPDIR=/home/mcc/BenchKit/bin/tmp

Got BK_MEMORY_CONFINEMENT=16384

Limiting to 16265216 kB

Total timeout: 3590

Time left: 3590

*************************************

* TAPAAL verifying CTLFireability *

*************************************

TEMPDIR=/home/mcc/BenchKit/bin/tmp

QF=/home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv

MF=/home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet

Time left: 3590

---------------------------------------------------

Step -1: Stripping Colors

---------------------------------------------------

Verifying stripped models (16 in total)

/home/mcc/BenchKit/bin/verifypn -n -c -q 718 -l 29 -d 299 -z 4 -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-15

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-14

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-13

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-12

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-11

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-10

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-09

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-08

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-07

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-06

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-05

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-04

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-03

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-02

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-01

Warning: CPN OverApproximation is only available for Reachability queries without deadlock, negated fireability and UpperBounds, skipping BART-COL-040-CTLFireability-00

WARNING: Could not run CPN over-approximation on any queries, terminating.

Time left: 3590

---------------------------------------------------

Step 0: Parallel Simplification

---------------------------------------------------

Doing parallel simplification (16 in total)

Total simplification timout is 718 -- reduction timeout is 299

timeout 3590 /home/mcc/BenchKit/bin/verifypn -n -q 718 -l 29 -d 299 -z 4 -s OverApprox --binary-query-io 2 --write-simplified /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --write-reduced /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet -x 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 ./model.pnml ./CTLFireability.xml

Time left: 3587

---------------------------------------------------

Step 1: Parallel processing

---------------------------------------------------

Doing parallel verification of individual queries (16 in total)

Each query is verified by 4 parallel strategies for 299 seconds

------------------- QUERY 1 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.056928 on verification

@@@0.13,59888@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 1 -n

FORMULA BART-COL-040-CTLFireability-04 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 3587

------------------- QUERY 2 ----------------------

No solution found

Command terminated by signal 9

@@@65.55,8879816@@@

Command terminated by signal 9

@@@131.31,9359980@@@

Time left: 3285

------------------- QUERY 3 ----------------------

No solution found

Command terminated by signal 9

@@@87.55,7957996@@@

Command terminated by signal 9

@@@180.70,8508664@@@

Time left: 2983

------------------- QUERY 4 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.225276 on verification

@@@0.30,59952@@@

Query index 0 was solved

Query is satisfied.

Spent 0.225722 on verification

@@@0.32,59480@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 4 -n

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 4 -n

FORMULA BART-COL-040-CTLFireability-03 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2982

------------------- QUERY 5 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.151684 on verification

@@@0.19,59624@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 5 -n

FORMULA BART-COL-040-CTLFireability-07 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2982

------------------- QUERY 6 ----------------------

No solution found

Command terminated by signal 9

@@@89.61,8197160@@@

Command terminated by signal 9

@@@159.93,10622984@@@

Time left: 2680

------------------- QUERY 7 ----------------------

No solution found

Command terminated by signal 9

@@@59.57,6225792@@@

Command terminated by signal 9

@@@100.96,9723144@@@

Command terminated by signal 9

@@@276.34,15749068@@@

Time left: 2378

------------------- QUERY 8 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.075862 on verification

@@@0.09,59820@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 8 -n

FORMULA BART-COL-040-CTLFireability-14 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2377

------------------- QUERY 9 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 7.49334 on verification

@@@7.53,671656@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 9 -n

FORMULA BART-COL-040-CTLFireability-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2369

------------------- QUERY 10 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.092399 on verification

@@@0.10,59784@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -tar\ -s\ RDFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 10 -n

FORMULA BART-COL-040-CTLFireability-05 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2369

------------------- QUERY 11 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.047615 on verification

@@@0.05,59936@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ BestFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 11 -n

FORMULA BART-COL-040-CTLFireability-13 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2369

------------------- QUERY 12 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is satisfied.

Spent 0.04762 on verification

@@@0.05,59896@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 12 -n

FORMULA BART-COL-040-CTLFireability-06 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2368

------------------- QUERY 13 ----------------------

No solution found

Command terminated by signal 9

@@@67.38,6619744@@@

Command terminated by signal 9

@@@120.03,9182624@@@

Command terminated by signal 9

@@@296.81,15702004@@@

Time left: 2067

------------------- QUERY 14 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.111403 on verification

@@@0.14,60164@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 14 -n

FORMULA BART-COL-040-CTLFireability-09 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2067

------------------- QUERY 15 ----------------------

Solution found by parallel processing (step 1)

Query index 0 was solved

Query is NOT satisfied.

Spent 0.119301 on verification

@@@0.13,59620@@@

parallel: This job succeeded:

eval /usr/bin/time -f "@@@%e,%M@@@" /home/mcc/BenchKit/bin/verifypn -n -s\ DFS\ -q\ 0\ -l\ 0\ -d\ 119 /home/mcc/BenchKit/bin/tmp/tmp.FM8w8MlFet /home/mcc/BenchKit/bin/tmp/tmp.Ah1YCcYwdv --binary-query-io 1 -x 15 -n

FORMULA BART-COL-040-CTLFireability-00 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION SAT_SMT STUBBORN_SETS CTL_CZERO

Time left: 2067

------------------- QUERY 16 ----------------------

No solution found

Command terminated by signal 9

@@@74.40,6809484@@@

Command terminated by signal 9

@@@125.71,8645080@@@

Time left: 1764

---------------------------------------------------

Step 2: Sequential processing

---------------------------------------------------

Remaining 6 queries are verified sequentially.

Each query is verified for a dynamic timeout (at least 598 seconds)

Time left: 1764

------------------- QUERY 2 ----------------------

Running query 2 for 598 seconds. Remaining: 6 queries and 1764 seconds

No solution found

Command terminated by signal 9

@@@72.67,8673064@@@

Command terminated by signal 9

@@@169.42,16146512@@@

Time left: 1595

------------------- QUERY 3 ----------------------

Running query 3 for 598 seconds. Remaining: 5 queries and 1595 seconds

No solution found

Command terminated by signal 9

@@@142.40,10221908@@@

Command terminated by signal 9

@@@398.57,16147208@@@

Time left: 1196

------------------- QUERY 6 ----------------------

Running query 6 for 598 seconds. Remaining: 4 queries and 1196 seconds

No solution found

Command terminated by signal 9

@@@101.51,8273292@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@197.63,15755468@@@

Time left: 998

------------------- QUERY 7 ----------------------

Running query 7 for 598 seconds. Remaining: 3 queries and 998 seconds

No solution found

Command terminated by signal 9

@@@86.12,8762276@@@

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

Command terminated by signal 6

@@@196.05,15773948@@@

Time left: 802

------------------- QUERY 13 ----------------------

Running query 13 for 598 seconds. Remaining: 2 queries and 802 seconds

No solution found

Command terminated by signal 9

@@@116.15,8505020@@@

Command terminated by signal 9

@@@249.22,16145008@@@

Time left: 552

------------------- QUERY 16 ----------------------

Time left: 552

---------------------------------------------------

Step 4: Random Parallel processing

---------------------------------------------------

Doing random parallel verification of individual queries (6 in total)

Each query is verified by 4 parallel strategies for 92 seconds

------------------- QUERY 2 ----------------------

No solution found

Command terminated by signal 9

@@@49.75,5996240@@@

Command terminated by signal 9

@@@71.33,5703936@@@

Time left: 457

------------------- QUERY 3 ----------------------

No solution found

Command terminated by signal 9

@@@71.19,5604136@@@

Time left: 363

------------------- QUERY 6 ----------------------

No solution found

Command terminated by signal 9

@@@64.00,4774844@@@

Command terminated by signal 9

@@@85.08,5523984@@@

Time left: 268

------------------- QUERY 7 ----------------------

No solution found

Command terminated by signal 9

@@@53.15,4379520@@@

Command terminated by signal 9

@@@72.11,5651120@@@

Time left: 172

------------------- QUERY 13 ----------------------

No solution found

Command terminated by signal 9

@@@48.32,4154788@@@

Command terminated by signal 9

@@@65.88,5631804@@@

Time left: 77

------------------- QUERY 16 ----------------------

No solution found

Command terminated by signal 9

@@@46.68,4230792@@@

Command terminated by signal 9

@@@64.45,5627444@@@

Time left: -2

Out of time, terminating!

terminated-with-cleanup

BK_STOP 1652568207729

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="BART-COL-040"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="tapaal"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool tapaal"

echo " Input is BART-COL-040, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r003-tajo-165245683100570"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/BART-COL-040.tgz

mv BART-COL-040 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;