About the Execution of LoLA for SmallOperatingSystem-PT-MT2048DC0512

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 10983.468 | 230494.00 | 199193.00 | 417.60 | ????F?????????T? | normal |

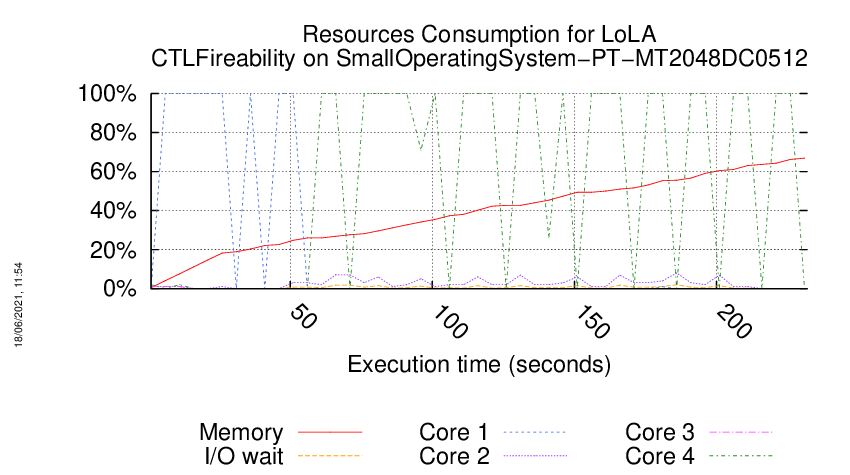

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2021-input.r251-tall-162106741500106.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2021-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

..................

=====================================================================

Generated by BenchKit 2-4028

Executing tool lola

Input is SmallOperatingSystem-PT-MT2048DC0512, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r251-tall-162106741500106

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 428K

-rw-r--r-- 1 mcc users 19K May 5 16:58 CTLCardinality.txt

-rw-r--r-- 1 mcc users 128K May 10 09:44 CTLCardinality.xml

-rw-r--r-- 1 mcc users 14K May 5 16:58 CTLFireability.txt

-rw-r--r-- 1 mcc users 94K May 10 09:44 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 6 14:48 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.7K May 6 14:48 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.1K Mar 28 16:42 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Mar 28 16:42 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.6K Mar 28 16:42 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Mar 28 16:42 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.7K Mar 27 13:41 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 21K Mar 27 13:41 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 3.7K Mar 25 19:28 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 20K Mar 25 19:28 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.0K Mar 22 08:16 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Mar 22 08:16 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 5 16:52 equiv_col

-rw-r--r-- 1 mcc users 13 May 5 16:52 instance

-rw-r--r-- 1 mcc users 6 May 5 16:52 iscolored

-rw-r--r-- 1 mcc users 8.1K May 5 16:52 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14

FORMULA_NAME SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1621118718188

starting LoLA

BK_INPUT SmallOperatingSystem-PT-MT2048DC0512

BK_EXAMINATION: CTLFireability

bin directory: /home/mcc/BenchKit/bin

current directory: /home/mcc/execution

CTLFireability

FORMULA SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

BK_STOP 1621118948682

--------------------

content from stderr:

lola: MEM LIMIT 32

lola: MEM LIMIT 5

lola: NET

lola: input: PNML file (--pnmlnet)

lola: reading net from /home/mcc/execution/model.pnml

lola: reading pnml

lola: PNML file contains place/transition net

lola: finished parsing

lola: closed net file /home/mcc/execution/model.pnml

lola: Reading formula.

lola: Using XML format (--xmlformula)

lola: reading XML formula

lola: reading formula from /home/mcc/execution/CTLFireability.xml

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:340

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:550

lola: rewrite Frontend/Parser/formula_rewrite.k:454

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: RELEASE

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:457

lola: rewrite Frontend/Parser/formula_rewrite.k:475

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:445

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:340

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:457

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:253

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: RELEASE

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:337

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: RELEASE

lola: rewrite Frontend/Parser/formula_rewrite.k:250

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:553

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:397

lola: rewrite Frontend/Parser/formula_rewrite.k:397

lola: rewrite Frontend/Parser/formula_rewrite.k:388

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:328

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:299

lola: rewrite Frontend/Parser/formula_rewrite.k:314

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:317

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:322

lola: rewrite Frontend/Parser/formula_rewrite.k:334

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: rewrite Frontend/Parser/formula_rewrite.k:445

lola: rewrite Frontend/Parser/formula_rewrite.k:454

lola: rewrite Frontend/Parser/formula_rewrite.k:325

lola: rewrite Frontend/Parser/formula_rewrite.k:331

lola: rewrite Frontend/Parser/formula_rewrite.k:296

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Rule S: 0 transitions removed,0 places removed

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: LAUNCH task # 1 (type EXCL) for 0 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00

lola: time limit : 133 sec

lola: memory limit: 32 pages

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: LAUNCH task # 57 (type FNDP) for 12 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: Created skeleton in 0.000000 secs.

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: LAUNCH task # 58 (type EQUN) for 12 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:721

lola: rewrite Frontend/Parser/formula_rewrite.k:787

lola: LAUNCH task # 60 (type SRCH) for 12 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: time limit : 32000000 sec

lola: memory limit: 5 pages

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: FINISHED task # 60 (type SRCH) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: result : unknown

lola: time used : 0.000000

lola: memory pages used : 1

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:815

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:811

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:809

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:814

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: FINISHED task # 57 (type FNDP) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: result : true

lola: fired transitions : 5123

lola: tried executions : 1

lola: time used : 0.000000

lola: memory pages used : 0

lola: CANCELED task # 58 (type EQUN) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04 (obsolete)

lola: FINISHED task # 58 (type EQUN) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04

lola: result : unknown

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:808

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:812

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:810

lola: rewrite Frontend/Parser/formula_rewrite.k:807

lola: rewrite Frontend/Parser/formula_rewrite.k:806

lola: Created skeleton in 0.000000 secs.

lola: rewrite Frontend/Parser/formula_rewrite.k:813

lola: rewrite Frontend/Parser/formula_rewrite.k:806

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

1 CTL EXCL 5/211 7/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 1608414 m, 321682 m/sec, 4815013 t fired, .

Time elapsed: 5 secs. Pages in use: 7

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

1 CTL EXCL 10/211 13/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 3064038 m, 291124 m/sec, 9179249 t fired, .

Time elapsed: 10 secs. Pages in use: 13

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

1 CTL EXCL 15/211 19/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 4523668 m, 291926 m/sec, 13551922 t fired, .

Time elapsed: 15 secs. Pages in use: 19

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

1 CTL EXCL 20/211 26/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 5975398 m, 290346 m/sec, 17900896 t fired, .

Time elapsed: 20 secs. Pages in use: 26

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

1 CTL EXCL 25/211 32/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 7420802 m, 289080 m/sec, 22230889 t fired, .

Time elapsed: 25 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 1 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 30 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 51 (type EXCL) for 46 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14

lola: time limit : 223 sec

lola: memory limit: 32 pages

lola: FINISHED task # 51 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14

lola: result : true

lola: time used : 0.000000

lola: memory pages used : 1

lola: LAUNCH task # 44 (type EXCL) for 43 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13

lola: time limit : 255 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

44 CTL EXCL 5/255 20/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13 4716012 m, 943202 m/sec, 9413068 t fired, .

Time elapsed: 35 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 44 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 2 0 0 2 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 40 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 41 (type EXCL) for 36 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12

lola: time limit : 273 sec

lola: memory limit: 32 pages

lola: FINISHED task # 41 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12

lola: result : true

lola: markings : 3154425

lola: fired transitions : 6295541

lola: time used : 3.000000

lola: memory pages used : 14

lola: LAUNCH task # 39 (type EXCL) for 36 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12

lola: time limit : 296 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 1 0 3 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 2/296 6/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12 1271501 m, 254300 m/sec, 2536144 t fired, .

Time elapsed: 45 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 1 0 3 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

39 CTL EXCL 7/296 25/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12 5780487 m, 901797 m/sec, 11535547 t fired, .

Time elapsed: 50 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 39 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 55 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 34 (type EXCL) for 33 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11

lola: time limit : 322 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

34 CTL EXCL 5/322 13/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11 2960545 m, 592109 m/sec, 9655332 t fired, .

Time elapsed: 60 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

34 CTL EXCL 10/322 24/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11 5672502 m, 542391 m/sec, 17786618 t fired, .

Time elapsed: 65 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 34 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 70 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 31 (type EXCL) for 30 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10

lola: time limit : 353 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

31 CTL EXCL 5/353 6/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10 1313877 m, 262775 m/sec, 5246117 t fired, .

Time elapsed: 75 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

31 CTL EXCL 10/353 13/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10 2890076 m, 315239 m/sec, 11541683 t fired, .

Time elapsed: 80 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

31 CTL EXCL 15/353 19/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10 4522301 m, 326445 m/sec, 18061281 t fired, .

Time elapsed: 85 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

31 CTL EXCL 20/353 26/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10 6138252 m, 323190 m/sec, 24515800 t fired, .

Time elapsed: 90 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 31 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 95 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 28 (type EXCL) for 27 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09

lola: time limit : 389 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

28 CTL EXCL 5/389 20/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09 4664358 m, 932871 m/sec, 9309732 t fired, .

Time elapsed: 100 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 28 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 105 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 25 (type EXCL) for 24 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08

lola: time limit : 436 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

25 CTL EXCL 5/436 11/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08 2564840 m, 512968 m/sec, 10250267 t fired, .

Time elapsed: 110 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

25 CTL EXCL 10/436 21/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08 4879282 m, 462888 m/sec, 19498792 t fired, .

Time elapsed: 115 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

25 CTL EXCL 15/436 31/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08 7193090 m, 462761 m/sec, 28744790 t fired, .

Time elapsed: 120 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 25 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 125 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 22 (type EXCL) for 21 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07

lola: time limit : 496 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

22 CTL EXCL 5/496 21/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07 5211767 m, 1042353 m/sec, 8744151 t fired, .

Time elapsed: 130 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

22 CTL EXCL 10/496 28/32 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07 6699407 m, 297528 m/sec, 16189690 t fired, .

Time elapsed: 135 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: CANCELED task # 22 (type EXCL) for SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07 (memory limit exceeded)

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-08: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-09: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-10: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-11: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-12: CONJ 0 0 0 0 3 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-13: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-15: CTL 0 1 0 0 1 0 0 0

TASK CATEGORY TYPE TIME/TLIMIT MEM PG/PGLIMIT FORMULA STATUS

Time elapsed: 140 secs. Pages in use: 32

# running tasks: 1 of 4 Visible: 16

lola: LAUNCH task # 19 (type EXCL) for 18 SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06

lola: time limit : 576 sec

lola: memory limit: 32 pages

FINISHED FORMULA: CATEGORY VALUE PRODUCED BY

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-04: AG false findpath

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-14: DISJ true CTL model checker

PENDING FORMULAS: CATEGORY IDL ACT RUN SUS FIN C/T C/M OBS

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-00: CTL 0 0 0 0 1 0 1 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-01: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-02: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-03: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-05: CTL 0 1 0 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-06: CTL 0 0 1 0 1 0 0 0

SmallOperatingSystem-PT-MT2048DC0512-CTLFireability-07: CTL 0 0 0 0 1 0 1 0