About the Execution of ITS-Tools for ShieldRVs-PT-004B

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 12425.728 | 2682957.00 | 2716032.00 | 9780.20 | ??F??T????FT???? | normal |

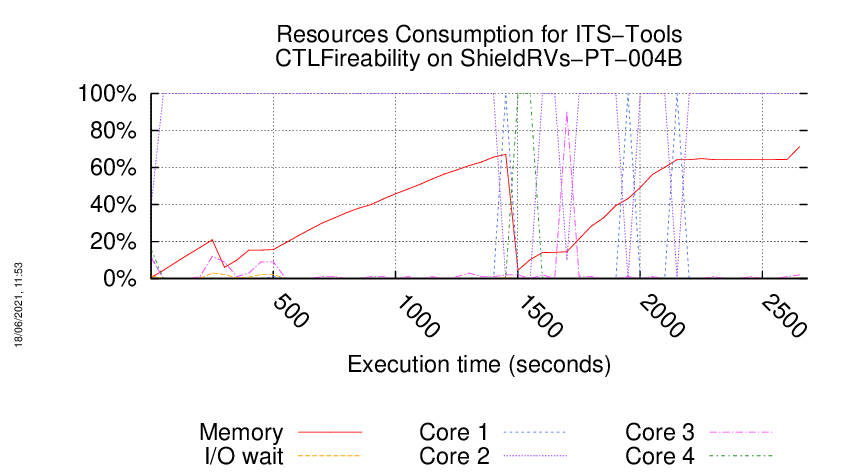

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2021-input.r235-smll-162106564400058.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fkordon/mcc2021-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.......................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is ShieldRVs-PT-004B, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r235-smll-162106564400058

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 380K

-rw-r--r-- 1 mcc users 9.9K May 5 16:58 CTLCardinality.txt

-rw-r--r-- 1 mcc users 94K May 10 09:44 CTLCardinality.xml

-rw-r--r-- 1 mcc users 8.8K May 5 16:58 CTLFireability.txt

-rw-r--r-- 1 mcc users 85K May 10 09:44 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 6 14:48 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.5K May 6 14:48 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.9K Mar 28 16:40 LTLCardinality.txt

-rw-r--r-- 1 mcc users 20K Mar 28 16:40 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9K Mar 28 16:40 LTLFireability.txt

-rw-r--r-- 1 mcc users 15K Mar 28 16:40 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.4K Mar 27 12:36 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 18K Mar 27 12:36 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.3K Mar 25 18:41 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 12K Mar 25 18:41 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Mar 22 08:16 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Mar 22 08:16 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 5 16:52 equiv_col

-rw-r--r-- 1 mcc users 5 May 5 16:52 instance

-rw-r--r-- 1 mcc users 6 May 5 16:52 iscolored

-rw-r--r-- 1 mcc users 49K May 5 16:52 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-00

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-01

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-02

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-03

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-04

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-05

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-06

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-07

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-08

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-09

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-10

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-11

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-12

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-13

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-14

FORMULA_NAME ShieldRVs-PT-004B-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1621116644020

Running Version 0

[2021-05-15 22:10:47] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -spotpath, /home/mcc/BenchKit/bin//..//ltlfilt, -z3path, /home/mcc/BenchKit/bin//..//z3/bin/z3, -yices2path, /home/mcc/BenchKit/bin//..//yices/bin/yices, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2021-05-15 22:10:47] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2021-05-15 22:10:47] [INFO ] Load time of PNML (sax parser for PT used): 112 ms

[2021-05-15 22:10:47] [INFO ] Transformed 163 places.

[2021-05-15 22:10:47] [INFO ] Transformed 183 transitions.

[2021-05-15 22:10:47] [INFO ] Found NUPN structural information;

[2021-05-15 22:10:47] [INFO ] Parsed PT model containing 163 places and 183 transitions in 196 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 29 ms.

Support contains 155 out of 163 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 163/163 places, 183/183 transitions.

Applied a total of 0 rules in 23 ms. Remains 163 /163 variables (removed 0) and now considering 183/183 (removed 0) transitions.

// Phase 1: matrix 183 rows 163 cols

[2021-05-15 22:10:47] [INFO ] Computed 17 place invariants in 26 ms

[2021-05-15 22:10:47] [INFO ] Implicit Places using invariants in 300 ms returned []

// Phase 1: matrix 183 rows 163 cols

[2021-05-15 22:10:47] [INFO ] Computed 17 place invariants in 6 ms

[2021-05-15 22:10:47] [INFO ] Implicit Places using invariants and state equation in 245 ms returned []

Implicit Place search using SMT with State Equation took 598 ms to find 0 implicit places.

// Phase 1: matrix 183 rows 163 cols

[2021-05-15 22:10:48] [INFO ] Computed 17 place invariants in 6 ms

[2021-05-15 22:10:48] [INFO ] Dead Transitions using invariants and state equation in 190 ms returned []

Finished structural reductions, in 1 iterations. Remains : 163/163 places, 183/183 transitions.

[2021-05-15 22:10:48] [INFO ] Flatten gal took : 69 ms

[2021-05-15 22:10:48] [INFO ] Flatten gal took : 29 ms

[2021-05-15 22:10:48] [INFO ] Input system was already deterministic with 183 transitions.

Incomplete random walk after 100000 steps, including 526 resets, run finished after 315 ms. (steps per millisecond=317 ) properties (out of 80) seen :79

Running SMT prover for 1 properties.

// Phase 1: matrix 183 rows 163 cols

[2021-05-15 22:10:49] [INFO ] Computed 17 place invariants in 4 ms

[2021-05-15 22:10:49] [INFO ] [Real]Absence check using 17 positive place invariants in 9 ms returned sat

[2021-05-15 22:10:49] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2021-05-15 22:10:49] [INFO ] [Real]Absence check using state equation in 76 ms returned sat

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 19 places in 114 ms of which 6 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 33 places in 79 ms of which 2 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 20 places in 57 ms of which 2 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 21 places in 52 ms of which 3 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 20 places in 57 ms of which 2 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Deduced a trap composed of 20 places in 39 ms of which 1 ms to minimize.

[2021-05-15 22:10:49] [INFO ] Trap strengthening (SAT) tested/added 7/6 trap constraints in 507 ms

[2021-05-15 22:10:49] [INFO ] Solution in real domain found non-integer solution.

[2021-05-15 22:10:49] [INFO ] [Nat]Absence check using 17 positive place invariants in 10 ms returned sat

[2021-05-15 22:10:49] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2021-05-15 22:10:49] [INFO ] [Nat]Absence check using state equation in 75 ms returned sat

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 19 places in 55 ms of which 1 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 33 places in 49 ms of which 1 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 20 places in 48 ms of which 0 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 20 places in 47 ms of which 1 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 27 places in 30 ms of which 1 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Deduced a trap composed of 26 places in 29 ms of which 0 ms to minimize.

[2021-05-15 22:10:50] [INFO ] Trap strengthening (SAT) tested/added 7/6 trap constraints in 365 ms

[2021-05-15 22:10:50] [INFO ] Computed and/alt/rep : 182/515/182 causal constraints (skipped 0 transitions) in 19 ms.

[2021-05-15 22:10:51] [INFO ] Added : 175 causal constraints over 38 iterations in 962 ms. Result :sat

Reduce places removed 1 places and 1 transitions.

Drop transitions removed 16 transitions

Trivial Post-agglo rules discarded 16 transitions

Performed 16 trivial Post agglomeration. Transition count delta: 16

Iterating post reduction 0 with 16 rules applied. Total rules applied 16 place count 162 transition count 166

Reduce places removed 16 places and 0 transitions.

Iterating post reduction 1 with 16 rules applied. Total rules applied 32 place count 146 transition count 166

Performed 20 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 20 Pre rules applied. Total rules applied 32 place count 146 transition count 146

Deduced a syphon composed of 20 places in 2 ms

Reduce places removed 20 places and 0 transitions.

Iterating global reduction 2 with 40 rules applied. Total rules applied 72 place count 126 transition count 146

Discarding 27 places :

Symmetric choice reduction at 2 with 27 rule applications. Total rules 99 place count 99 transition count 119

Iterating global reduction 2 with 27 rules applied. Total rules applied 126 place count 99 transition count 119

Performed 8 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 8 Pre rules applied. Total rules applied 126 place count 99 transition count 111

Deduced a syphon composed of 8 places in 1 ms

Reduce places removed 8 places and 0 transitions.

Iterating global reduction 2 with 16 rules applied. Total rules applied 142 place count 91 transition count 111

Performed 25 Post agglomeration using F-continuation condition.Transition count delta: 25

Deduced a syphon composed of 25 places in 0 ms

Reduce places removed 25 places and 0 transitions.

Iterating global reduction 2 with 50 rules applied. Total rules applied 192 place count 66 transition count 86

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 193 place count 65 transition count 85

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 194 place count 64 transition count 84

Applied a total of 194 rules in 93 ms. Remains 64 /163 variables (removed 99) and now considering 84/183 (removed 99) transitions.

[2021-05-15 22:10:51] [INFO ] Flatten gal took : 15 ms

[2021-05-15 22:10:51] [INFO ] Flatten gal took : 16 ms

[2021-05-15 22:10:51] [INFO ] Input system was already deterministic with 84 transitions.

[2021-05-15 22:10:51] [INFO ] Flatten gal took : 13 ms

[2021-05-15 22:10:51] [INFO ] Flatten gal took : 13 ms

[2021-05-15 22:10:51] [INFO ] Time to serialize gal into /tmp/CTLFireability17784672934208350524.gal : 7 ms

[2021-05-15 22:10:51] [INFO ] Time to serialize properties into /tmp/CTLFireability15776469923024898267.ctl : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability17784672934208350524.gal, -t, CGAL, -ctl, /tmp/CTLFireability15776469923024898267.ctl, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability17784672934208350524.gal -t CGAL -ctl /tmp/CTLFireability15776469923024898267.ctl --gen-order FOLLOW

No direction supplied, using forward translation only.

Parsed 1 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,3.36293e+08,0.450645,16656,2,2110,5,38072,6,0,342,87749,0

Converting to forward existential form...Done !

original formula: !(AF(((((((((p6==1)&&(p15==1))&&(p42==1))||(p17==1))||(((p71==1)&&(p79==1))&&(p105==1)))||(p84==1))||(((p110==1)&&(p121==1))&&(p144==1)))||(p157==1))))

=> equivalent forward existential formula: [FwdG(Init,!(((((((((p6==1)&&(p15==1))&&(p42==1))||(p17==1))||(((p71==1)&&(p79==1))&&(p105==1)))||(p84==1))||(((p110==1)&&(p121==1))&&(p144==1)))||(p157==1))))] != FALSE

Hit Full ! (commute/partial/dont) 37/105/47

(forward)formula 0,0,3.10437,78108,1,0,92,294128,20,3,2080,541767,91

FORMULA ShieldRVs-PT-004B-CTLFireability-02 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

Reduce places removed 1 places and 1 transitions.

Drop transitions removed 17 transitions

Trivial Post-agglo rules discarded 17 transitions

Performed 17 trivial Post agglomeration. Transition count delta: 17

Iterating post reduction 0 with 17 rules applied. Total rules applied 17 place count 162 transition count 165

Reduce places removed 17 places and 0 transitions.

Iterating post reduction 1 with 17 rules applied. Total rules applied 34 place count 145 transition count 165

Performed 20 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 20 Pre rules applied. Total rules applied 34 place count 145 transition count 145

Deduced a syphon composed of 20 places in 0 ms

Reduce places removed 20 places and 0 transitions.

Iterating global reduction 2 with 40 rules applied. Total rules applied 74 place count 125 transition count 145

Discarding 27 places :

Symmetric choice reduction at 2 with 27 rule applications. Total rules 101 place count 98 transition count 118

Iterating global reduction 2 with 27 rules applied. Total rules applied 128 place count 98 transition count 118

Performed 11 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 11 Pre rules applied. Total rules applied 128 place count 98 transition count 107

Deduced a syphon composed of 11 places in 0 ms

Reduce places removed 11 places and 0 transitions.

Iterating global reduction 2 with 22 rules applied. Total rules applied 150 place count 87 transition count 107

Performed 26 Post agglomeration using F-continuation condition.Transition count delta: 26

Deduced a syphon composed of 26 places in 0 ms

Reduce places removed 26 places and 0 transitions.

Iterating global reduction 2 with 52 rules applied. Total rules applied 202 place count 61 transition count 81

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 203 place count 60 transition count 80

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 204 place count 59 transition count 79

Applied a total of 204 rules in 35 ms. Remains 59 /163 variables (removed 104) and now considering 79/183 (removed 104) transitions.

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 7 ms

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 8 ms

[2021-05-15 22:10:54] [INFO ] Input system was already deterministic with 79 transitions.

Finished random walk after 3 steps, including 0 resets, run visited all 1 properties in 1 ms. (steps per millisecond=3 )

FORMULA ShieldRVs-PT-004B-CTLFireability-05 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Reduce places removed 1 places and 1 transitions.

Drop transitions removed 17 transitions

Trivial Post-agglo rules discarded 17 transitions

Performed 17 trivial Post agglomeration. Transition count delta: 17

Iterating post reduction 0 with 17 rules applied. Total rules applied 17 place count 162 transition count 165

Reduce places removed 17 places and 0 transitions.

Iterating post reduction 1 with 17 rules applied. Total rules applied 34 place count 145 transition count 165

Performed 20 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 20 Pre rules applied. Total rules applied 34 place count 145 transition count 145

Deduced a syphon composed of 20 places in 1 ms

Reduce places removed 20 places and 0 transitions.

Iterating global reduction 2 with 40 rules applied. Total rules applied 74 place count 125 transition count 145

Discarding 28 places :

Symmetric choice reduction at 2 with 28 rule applications. Total rules 102 place count 97 transition count 117

Iterating global reduction 2 with 28 rules applied. Total rules applied 130 place count 97 transition count 117

Performed 11 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 11 Pre rules applied. Total rules applied 130 place count 97 transition count 106

Deduced a syphon composed of 11 places in 0 ms

Reduce places removed 11 places and 0 transitions.

Iterating global reduction 2 with 22 rules applied. Total rules applied 152 place count 86 transition count 106

Performed 25 Post agglomeration using F-continuation condition.Transition count delta: 25

Deduced a syphon composed of 25 places in 1 ms

Reduce places removed 25 places and 0 transitions.

Iterating global reduction 2 with 50 rules applied. Total rules applied 202 place count 61 transition count 81

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 203 place count 60 transition count 80

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 204 place count 59 transition count 79

Applied a total of 204 rules in 34 ms. Remains 59 /163 variables (removed 104) and now considering 79/183 (removed 104) transitions.

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 7 ms

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 8 ms

[2021-05-15 22:10:54] [INFO ] Input system was already deterministic with 79 transitions.

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 8 ms

[2021-05-15 22:10:54] [INFO ] Flatten gal took : 7 ms

[2021-05-15 22:10:54] [INFO ] Time to serialize gal into /tmp/CTLFireability18093414144235205466.gal : 4 ms

[2021-05-15 22:10:54] [INFO ] Time to serialize properties into /tmp/CTLFireability1733283040309899729.ctl : 1 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability18093414144235205466.gal, -t, CGAL, -ctl, /tmp/CTLFireability1733283040309899729.ctl, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability18093414144235205466.gal -t CGAL -ctl /tmp/CTLFireability1733283040309899729.ctl --gen-order FOLLOW

No direction supplied, using forward translation only.

Parsed 1 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,1.71347e+08,0.415808,14856,2,1760,5,32694,6,0,318,72638,0

Converting to forward existential form...Done !

original formula: !(EF(EG(!(AG(((((p29==1)&&(p43==1))&&(p66==1))||(p40==1)))))))

=> equivalent forward existential formula: [FwdG(FwdU(Init,TRUE),!(!(E(TRUE U !(((((p29==1)&&(p43==1))&&(p66==1))||(p40==1)))))))] = FALSE

Reverse transition relation is NOT exact ! Due to transitions t0, t1, t2, t3, t4, t5, t6, t7, t8, t9, t10, t11, t12, t13, t14, t15, t16, t17, t18, t19, t20, t21, t22, t23, t24, t45, t46, t47, t48, t49, t50, t51, t52, t53, t54, t55, t56, t57, t58, t59, t60, t61, t62, t63, t64, t65, t66, t67, t68, t69, t70, t71, t72, t73, t74, t75, t76, t77, t78, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/20/59/79

(forward)formula 0,0,3.25962,79396,1,0,300,331544,184,87,2656,590282,246

FORMULA ShieldRVs-PT-004B-CTLFireability-10 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

Reduce places removed 1 places and 1 transitions.

Drop transitions removed 14 transitions

Trivial Post-agglo rules discarded 14 transitions

Performed 14 trivial Post agglomeration. Transition count delta: 14

Iterating post reduction 0 with 14 rules applied. Total rules applied 14 place count 162 transition count 168

Reduce places removed 14 places and 0 transitions.

Iterating post reduction 1 with 14 rules applied. Total rules applied 28 place count 148 transition count 168

Performed 19 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 19 Pre rules applied. Total rules applied 28 place count 148 transition count 149

Deduced a syphon composed of 19 places in 1 ms

Reduce places removed 19 places and 0 transitions.

Iterating global reduction 2 with 38 rules applied. Total rules applied 66 place count 129 transition count 149

Discarding 26 places :

Symmetric choice reduction at 2 with 26 rule applications. Total rules 92 place count 103 transition count 123

Iterating global reduction 2 with 26 rules applied. Total rules applied 118 place count 103 transition count 123

Performed 11 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 11 Pre rules applied. Total rules applied 118 place count 103 transition count 112

Deduced a syphon composed of 11 places in 0 ms

Reduce places removed 11 places and 0 transitions.

Iterating global reduction 2 with 22 rules applied. Total rules applied 140 place count 92 transition count 112

Performed 24 Post agglomeration using F-continuation condition.Transition count delta: 24

Deduced a syphon composed of 24 places in 0 ms

Reduce places removed 24 places and 0 transitions.

Iterating global reduction 2 with 48 rules applied. Total rules applied 188 place count 68 transition count 88

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 2 with 1 rules applied. Total rules applied 189 place count 67 transition count 87

Applied a total of 189 rules in 48 ms. Remains 67 /163 variables (removed 96) and now considering 87/183 (removed 96) transitions.

[2021-05-15 22:10:58] [INFO ] Flatten gal took : 10 ms

[2021-05-15 22:10:58] [INFO ] Flatten gal took : 9 ms

[2021-05-15 22:10:58] [INFO ] Input system was already deterministic with 87 transitions.

[2021-05-15 22:10:58] [INFO ] Flatten gal took : 9 ms

[2021-05-15 22:10:58] [INFO ] Flatten gal took : 8 ms

[2021-05-15 22:10:58] [INFO ] Time to serialize gal into /tmp/CTLFireability28436079933437963.gal : 2 ms

[2021-05-15 22:10:58] [INFO ] Time to serialize properties into /tmp/CTLFireability11901603570144946895.ctl : 0 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability28436079933437963.gal, -t, CGAL, -ctl, /tmp/CTLFireability11901603570144946895.ctl, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability28436079933437963.gal -t CGAL -ctl /tmp/CTLFireability11901603570144946895.ctl --gen-order FOLLOW

No direction supplied, using forward translation only.

Parsed 1 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,2.9736e+08,0.422273,15380,2,1964,5,32732,6,0,356,75771,0

Converting to forward existential form...Done !

original formula: AG(((!(AG(((((((((p162==1)||(p161==1))||(p145==1))||(p68==1))||(p116==1))||(((p95==1)&&(p101==1))&&(p109==1)))||(p132==1))||(p70==1)))) + (p152==1)) + (p47==1)))

=> equivalent forward existential formula: [(((FwdU(Init,TRUE) * !((p47==1))) * !((p152==1))) * !(E(TRUE U !(((((((((p162==1)||(p161==1))||(p145==1))||(p68==1))||(p116==1))||(((p95==1)&&(p101==1))&&(p109==1)))||(p132==1))||(p70==1))))))] = FALSE

Reverse transition relation is NOT exact ! Due to transitions t0, t1, t2, t3, t4, t5, t6, t7, t8, t9, t10, t11, t12, t13, t14, t15, t16, t17, t18, t19, t20, t21, t22, t23, t24, t25, t27, t29, t52, t53, t54, t55, t56, t57, t58, t59, t60, t61, t62, t63, t64, t65, t66, t67, t68, t69, t70, t71, t72, t73, t74, t75, t76, t77, t79, t80, t81, t82, t83, t84, t85, t86, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/25/62/87

(forward)formula 0,1,1.49942,36236,1,0,260,187611,196,98,2821,218407,202

FORMULA ShieldRVs-PT-004B-CTLFireability-11 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

[2021-05-15 22:10:59] [INFO ] Flatten gal took : 18 ms

[2021-05-15 22:10:59] [INFO ] Flatten gal took : 16 ms

[2021-05-15 22:10:59] [INFO ] Applying decomposition

[2021-05-15 22:10:59] [INFO ] Flatten gal took : 15 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/convert-linux64, -i, /tmp/graph2455195298580652023.txt, -o, /tmp/graph2455195298580652023.bin, -w, /tmp/graph2455195298580652023.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202104292328/bin/louvain-linux64, /tmp/graph2455195298580652023.bin, -l, -1, -v, -w, /tmp/graph2455195298580652023.weights, -q, 0, -e, 0.001], workingDir=null]

[2021-05-15 22:11:00] [INFO ] Decomposing Gal with order

[2021-05-15 22:11:00] [INFO ] Rewriting arrays to variables to allow decomposition.

[2021-05-15 22:11:00] [INFO ] Removed a total of 135 redundant transitions.

[2021-05-15 22:11:00] [INFO ] Flatten gal took : 73 ms

[2021-05-15 22:11:00] [INFO ] Fuse similar labels procedure discarded/fused a total of 0 labels/synchronizations in 6 ms.

[2021-05-15 22:11:00] [INFO ] Time to serialize gal into /tmp/CTLFireability17121958356382979780.gal : 8 ms

[2021-05-15 22:11:00] [INFO ] Time to serialize properties into /tmp/CTLFireability13021041656285285237.ctl : 11 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability17121958356382979780.gal, -t, CGAL, -ctl, /tmp/CTLFireability13021041656285285237.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability17121958356382979780.gal -t CGAL -ctl /tmp/CTLFireability13021041656285285237.ctl

No direction supplied, using forward translation only.

Parsed 12 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.61506e+12,3.33688,59884,2717,77,80755,429,413,254051,53,2012,0

Converting to forward existential form...Done !

original formula: (EF((((((((((((((i9.u0.p0==1)||(i5.u21.p83==1))||(i2.u11.p35==1))||(i8.u34.p118==1))||(i0.u12.p40==1))||(i7.u32.p104==1))||(i1.u3.p9==1))||(((i6.u27.p91==1)&&(i10.u40.p135==1))&&(i11.i1.u46.p160==1)))||(i7.u32.p111==1))||(((i0.u1.p6==1)&&(i0.u5.p15==1))&&(i2.u13.p43==1)))||(i0.u5.p15==1))&&((((i5.u22.p80==1)||(i3.i1.u16.p53==1))||(((i7.u31.p107==1)&&(i8.u35.p121==1))&&(i11.i0.u43.p144==1)))||(i5.u22.p77==1)))&&((((i0.u1.p6==1)&&(i0.u5.p15==1))&&(i0.u12.p42==1))||(i7.u31.p108==1)))) * ((AF(AX(((((((((i8.u35.p114==1)||(i5.u22.p81==1))||(i0.u4.p20==1))||(i11.i0.u43.p148==1))||(i10.u37.p126==1))||(i11.i0.u44.p143==1))||(i3.i0.u18.p60==1))||(i0.u5.p15==1)))) + !(AX(AG(((((((((i3.i0.u15.p48==1)||((i0.u1.p4==1)&&(i1.u9.p27==1)))||(i4.u19.p68==1))||(i9.u24.p86==1))||(((i3.i1.u16.p52==1)&&(i6.u28.p96==1))&&(i8.u34.p120==1)))||(i3.i0.u18.p61==1))||(i7.u31.p108==1))||(i6.u27.p94==1)))))) + !(A(((((i0.u6.p18==1)&&(i1.u7.p23==1))&&(i1.u10.p32==1))||(((i6.u27.p91==1)&&(i10.u39.p132==1))&&(i11.i1.u46.p160==1))) U (!(AF((((((((((i4.u20.p65==1)||(i7.u30.p112==1))||(((i3.i1.u16.p56==1)&&(i3.i0.u18.p62==1))&&(i4.u19.p70==1)))||(i3.i1.u16.p53==1))||(i1.u7.p21==1))||(((i10.u39.p134==1)&&(i10.u41.p140==1))&&(i11.i0.u44.p149==1)))||(i2.u2.p8==1))||(i0.u12.p40==1))||(i1.u9.p30==1)))) + ((((((((((i0.u4.p20==0)&&(i10.u41.p138==0))&&(((i7.u32.p110==0)||(i8.u35.p121==0))||(i11.i0.u43.p144==0)))&&(i5.u21.p75==0))&&(i1.u3.p10==0))&&(i3.i1.u17.p58==0))&&(((i6.u27.p91==0)||(i10.u39.p132==0))||(i11.i1.u46.p160==0)))&&(i0.u12.p41==0))&&(i6.u25.p88==0))&&(i7.u31.p107==0)))))))

=> equivalent forward existential formula: ([(Init * !(E(TRUE U (((((((((((((i9.u0.p0==1)||(i5.u21.p83==1))||(i2.u11.p35==1))||(i8.u34.p118==1))||(i0.u12.p40==1))||(i7.u32.p104==1))||(i1.u3.p9==1))||(((i6.u27.p91==1)&&(i10.u40.p135==1))&&(i11.i1.u46.p160==1)))||(i7.u32.p111==1))||(((i0.u1.p6==1)&&(i0.u5.p15==1))&&(i2.u13.p43==1)))||(i0.u5.p15==1))&&((((i5.u22.p80==1)||(i3.i1.u16.p53==1))||(((i7.u31.p107==1)&&(i8.u35.p121==1))&&(i11.i0.u43.p144==1)))||(i5.u22.p77==1)))&&((((i0.u1.p6==1)&&(i0.u5.p15==1))&&(i0.u12.p42==1))||(i7.u31.p108==1))))))] = FALSE * [FwdG(((Init * !(!(!((E(!((!(!(EG(!((((((((((i4.u20.p65==1)||(i7.u30.p112==1))||(((i3.i1.u16.p56==1)&&(i3.i0.u18.p62==1))&&(i4.u19.p70==1)))||(i3.i1.u16.p53==1))||(i1.u7.p21==1))||(((i10.u39.p134==1)&&(i10.u41.p140==1))&&(i11.i0.u44.p149==1)))||(i2.u2.p8==1))||(i0.u12.p40==1))||(i1.u9.p30==1)))))) + ((((((((((i0.u4.p20==0)&&(i10.u41.p138==0))&&(((i7.u32.p110==0)||(i8.u35.p121==0))||(i11.i0.u43.p144==0)))&&(i5.u21.p75==0))&&(i1.u3.p10==0))&&(i3.i1.u17.p58==0))&&(((i6.u27.p91==0)||(i10.u39.p132==0))||(i11.i1.u46.p160==0)))&&(i0.u12.p41==0))&&(i6.u25.p88==0))&&(i7.u31.p107==0)))) U (!(((((i0.u6.p18==1)&&(i1.u7.p23==1))&&(i1.u10.p32==1))||(((i6.u27.p91==1)&&(i10.u39.p132==1))&&(i11.i1.u46.p160==1)))) * !((!(!(EG(!((((((((((i4.u20.p65==1)||(i7.u30.p112==1))||(((i3.i1.u16.p56==1)&&(i3.i0.u18.p62==1))&&(i4.u19.p70==1)))||(i3.i1.u16.p53==1))||(i1.u7.p21==1))||(((i10.u39.p134==1)&&(i10.u41.p140==1))&&(i11.i0.u44.p149==1)))||(i2.u2.p8==1))||(i0.u12.p40==1))||(i1.u9.p30==1)))))) + ((((((((((i0.u4.p20==0)&&(i10.u41.p138==0))&&(((i7.u32.p110==0)||(i8.u35.p121==0))||(i11.i0.u43.p144==0)))&&(i5.u21.p75==0))&&(i1.u3.p10==0))&&(i3.i1.u17.p58==0))&&(((i6.u27.p91==0)||(i10.u39.p132==0))||(i11.i1.u46.p160==0)))&&(i0.u12.p41==0))&&(i6.u25.p88==0))&&(i7.u31.p107==0)))))) + EG(!((!(!(EG(!((((((((((i4.u20.p65==1)||(i7.u30.p112==1))||(((i3.i1.u16.p56==1)&&(i3.i0.u18.p62==1))&&(i4.u19.p70==1)))||(i3.i1.u16.p53==1))||(i1.u7.p21==1))||(((i10.u39.p134==1)&&(i10.u41.p140==1))&&(i11.i0.u44.p149==1)))||(i2.u2.p8==1))||(i0.u12.p40==1))||(i1.u9.p30==1)))))) + ((((((((((i0.u4.p20==0)&&(i10.u41.p138==0))&&(((i7.u32.p110==0)||(i8.u35.p121==0))||(i11.i0.u43.p144==0)))&&(i5.u21.p75==0))&&(i1.u3.p10==0))&&(i3.i1.u17.p58==0))&&(((i6.u27.p91==0)||(i10.u39.p132==0))||(i11.i1.u46.p160==0)))&&(i0.u12.p41==0))&&(i6.u25.p88==0))&&(i7.u31.p107==0)))))))))) * !(!(!(EX(!(!(E(TRUE U !(((((((((i3.i0.u15.p48==1)||((i0.u1.p4==1)&&(i1.u9.p27==1)))||(i4.u19.p68==1))||(i9.u24.p86==1))||(((i3.i1.u16.p52==1)&&(i6.u28.p96==1))&&(i8.u34.p120==1)))||(i3.i0.u18.p61==1))||(i7.u31.p108==1))||(i6.u27.p94==1))))))))))),!(!(EX(!(((((((((i8.u35.p114==1)||(i5.u22.p81==1))||(i0.u4.p20==1))||(i11.i0.u43.p148==1))||(i10.u37.p126==1))||(i11.i0.u44.p143==1))||(i3.i0.u18.p60==1))||(i0.u5.p15==1)))))))] = FALSE)

Reverse transition relation is NOT exact ! Due to transitions i0.t125, i0.u1.t128, i0.u5.t0, i0.u5.t1, i0.u5.t2, i0.u5.t3, i0.u6.t127, i0.u12.t8, i0.u12.t9, i0.u12.t10, i0.u12.t11, i1.t118, i1.u7.t122, i1.u7.t123, i1.u9.t4, i1.u9.t5, i1.u9.t6, i1.u9.t7, i1.u10.t120, i2.t112, i2.u13.t115, i3.i0.u18.t102, i3.i0.u18.t103, i3.i1.u16.t12, i3.i1.u16.t13, i3.i1.u16.t14, i3.i1.u16.t15, i3.i1.u17.t105, i3.i1.u17.t107, i4.u19.t16, i4.u19.t17, i4.u19.t18, i4.u19.t19, i4.u20.t98, i4.u20.t100, i5.t92, i5.u21.t95, i5.u22.t20, i5.u22.t21, i5.u22.t22, i5.u22.t23, i6.t85, i6.u27.t24, i6.u27.t25, i6.u27.t26, i6.u27.t27, i6.u28.t87, i6.u29.t82, i6.u29.t83, i7.t78, i7.u31.t28, i7.u31.t29, i7.u31.t30, i7.u31.t31, i7.u32.t80, i8.t72, i8.u34.t32, i8.u34.t33, i8.u34.t34, i8.u34.t35, i8.u35.t75, i10.t65, i10.u39.t36, i10.u39.t37, i10.u39.t38, i10.u39.t39, i10.u40.t67, i10.u41.t62, i10.u41.t63, i11.i0.t58, i11.i0.u43.t40, i11.i0.u43.t41, i11.i0.u43.t42, i11.i0.u43.t43, i11.i0.u44.t60, i11.i1.t52, i11.i1.u46.t55, i11.i1.u47.t44, i11.i1.u47.t45, i11.i1.u47.t46, i11.i1.u47.t47, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/102/81/183

ITS-tools command line returned an error code 139

[2021-05-15 22:15:16] [INFO ] Applying decomposition

[2021-05-15 22:15:16] [INFO ] Flatten gal took : 28 ms

[2021-05-15 22:15:16] [INFO ] Decomposing Gal with order

[2021-05-15 22:15:16] [INFO ] Rewriting arrays to variables to allow decomposition.

[2021-05-15 22:15:16] [INFO ] Removed a total of 81 redundant transitions.

[2021-05-15 22:15:16] [INFO ] Flatten gal took : 44 ms

[2021-05-15 22:15:16] [INFO ] Fuse similar labels procedure discarded/fused a total of 120 labels/synchronizations in 16 ms.

[2021-05-15 22:15:16] [INFO ] Time to serialize gal into /tmp/CTLFireability2169241767316410794.gal : 5 ms

[2021-05-15 22:15:16] [INFO ] Time to serialize properties into /tmp/CTLFireability10400979105761965207.ctl : 8 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability2169241767316410794.gal, -t, CGAL, -ctl, /tmp/CTLFireability10400979105761965207.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability2169241767316410794.gal -t CGAL -ctl /tmp/CTLFireability10400979105761965207.ctl

No direction supplied, using forward translation only.

Parsed 12 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.61506e+12,31.9756,745152,6868,345,1.00786e+06,1305,146,6.5568e+06,85,26077,0

Converting to forward existential form...Done !

original formula: (EF((((((((((((((u36.p0==1)||(i0.i0.i1.u18.p83==1))||(i0.i0.i0.i1.u11.p35==1))||(i0.i1.u25.p118==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i1.i0.u24.p104==1))||(i0.i0.i0.i1.i0.u42.p9==1))||(((i0.i1.i0.i0.u22.p91==1)&&(i1.i0.i0.u29.p135==1))&&(i1.u32.p160==1)))||(i0.i1.i0.u24.p111==1))||(((i0.i0.i0.u4.p6==1)&&(i0.i0.i0.i1.i0.i0.u8.p15==1))&&(i0.i0.i0.i1.u11.p43==1)))||(i0.i0.i0.i1.i0.i0.u8.p15==1))&&((((i0.i0.i1.u18.p80==1)||(i0.i0.i1.i0.i0.u15.p53==1))||(((i0.i1.i0.u24.p107==1)&&(i0.i1.u25.p121==1))&&(i1.i0.u31.p144==1)))||(i0.i0.i1.u18.p77==1)))&&((((i0.i0.i0.u4.p6==1)&&(i0.i0.i0.i1.i0.i0.u8.p15==1))&&(i0.i0.i0.i1.u11.p42==1))||(i0.i1.i0.u24.p108==1)))) * ((AF(AX(((((((((i0.i1.u25.p114==1)||(i0.i0.i1.u18.p81==1))||(i0.i0.i0.i1.i0.i0.u8.p20==1))||(i1.i0.u31.p148==1))||(i1.i0.u48.p126==1))||(i1.i0.u31.p143==1))||(i0.i0.i1.i0.i0.u16.p60==1))||(i0.i0.i0.i1.i0.i0.u8.p15==1)))) + !(AX(AG(((((((((i0.i0.i1.i0.u33.p48==1)||((i0.i0.i0.u4.p4==1)&&(i0.i0.i0.i1.i0.u10.p27==1)))||(i0.i0.i1.i0.u17.p68==1))||(i0.i1.u38.p86==1))||(((i0.i0.i1.i0.i0.u15.p52==1)&&(i0.i1.i0.i0.u22.p96==1))&&(i0.i1.u25.p120==1)))||(i0.i0.i1.i0.i0.u16.p61==1))||(i0.i1.i0.u24.p108==1))||(i0.i1.i0.i0.u22.p94==1)))))) + !(A(((((i0.i0.i0.i1.i0.i0.u8.p18==1)&&(i0.i0.i0.i1.i0.i0.u9.p23==1))&&(i0.i0.i0.i1.i0.u10.p32==1))||(((i0.i1.i0.i0.u22.p91==1)&&(i1.i0.i0.u29.p132==1))&&(i1.u32.p160==1))) U (!(AF((((((((((i0.i0.i1.i0.u17.p65==1)||(i0.i1.i0.u24.p112==1))||(((i0.i0.i1.i0.i0.u15.p56==1)&&(i0.i0.i1.i0.i0.u16.p62==1))&&(i0.i0.i1.i0.u17.p70==1)))||(i0.i0.i1.i0.i0.u15.p53==1))||(i0.i0.i0.i1.i0.i0.u9.p21==1))||(((i1.i0.i0.u29.p134==1)&&(i1.i0.i0.u30.p140==1))&&(i1.i0.u31.p149==1)))||(i0.i0.i0.i1.u41.p8==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i0.i0.i1.i0.u10.p30==1)))) + ((((((((((i0.i0.i0.i1.i0.i0.u8.p20==0)&&(i1.i0.i0.u30.p138==0))&&(((i0.i1.i0.u24.p110==0)||(i0.i1.u25.p121==0))||(i1.i0.u31.p144==0)))&&(i0.i0.i1.u18.p75==0))&&(i0.i0.i0.i1.i0.i0.u43.p10==0))&&(i0.i0.i1.i0.i0.u15.p58==0))&&(((i0.i1.i0.i0.u22.p91==0)||(i1.i0.i0.u29.p132==0))||(i1.u32.p160==0)))&&(i0.i0.i0.i1.u11.p41==0))&&(i0.i1.i0.i0.u45.p88==0))&&(i0.i1.i0.u24.p107==0)))))))

=> equivalent forward existential formula: ([(Init * !(E(TRUE U (((((((((((((u36.p0==1)||(i0.i0.i1.u18.p83==1))||(i0.i0.i0.i1.u11.p35==1))||(i0.i1.u25.p118==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i1.i0.u24.p104==1))||(i0.i0.i0.i1.i0.u42.p9==1))||(((i0.i1.i0.i0.u22.p91==1)&&(i1.i0.i0.u29.p135==1))&&(i1.u32.p160==1)))||(i0.i1.i0.u24.p111==1))||(((i0.i0.i0.u4.p6==1)&&(i0.i0.i0.i1.i0.i0.u8.p15==1))&&(i0.i0.i0.i1.u11.p43==1)))||(i0.i0.i0.i1.i0.i0.u8.p15==1))&&((((i0.i0.i1.u18.p80==1)||(i0.i0.i1.i0.i0.u15.p53==1))||(((i0.i1.i0.u24.p107==1)&&(i0.i1.u25.p121==1))&&(i1.i0.u31.p144==1)))||(i0.i0.i1.u18.p77==1)))&&((((i0.i0.i0.u4.p6==1)&&(i0.i0.i0.i1.i0.i0.u8.p15==1))&&(i0.i0.i0.i1.u11.p42==1))||(i0.i1.i0.u24.p108==1))))))] = FALSE * [FwdG(((Init * !(!(!((E(!((!(!(EG(!((((((((((i0.i0.i1.i0.u17.p65==1)||(i0.i1.i0.u24.p112==1))||(((i0.i0.i1.i0.i0.u15.p56==1)&&(i0.i0.i1.i0.i0.u16.p62==1))&&(i0.i0.i1.i0.u17.p70==1)))||(i0.i0.i1.i0.i0.u15.p53==1))||(i0.i0.i0.i1.i0.i0.u9.p21==1))||(((i1.i0.i0.u29.p134==1)&&(i1.i0.i0.u30.p140==1))&&(i1.i0.u31.p149==1)))||(i0.i0.i0.i1.u41.p8==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i0.i0.i1.i0.u10.p30==1)))))) + ((((((((((i0.i0.i0.i1.i0.i0.u8.p20==0)&&(i1.i0.i0.u30.p138==0))&&(((i0.i1.i0.u24.p110==0)||(i0.i1.u25.p121==0))||(i1.i0.u31.p144==0)))&&(i0.i0.i1.u18.p75==0))&&(i0.i0.i0.i1.i0.i0.u43.p10==0))&&(i0.i0.i1.i0.i0.u15.p58==0))&&(((i0.i1.i0.i0.u22.p91==0)||(i1.i0.i0.u29.p132==0))||(i1.u32.p160==0)))&&(i0.i0.i0.i1.u11.p41==0))&&(i0.i1.i0.i0.u45.p88==0))&&(i0.i1.i0.u24.p107==0)))) U (!(((((i0.i0.i0.i1.i0.i0.u8.p18==1)&&(i0.i0.i0.i1.i0.i0.u9.p23==1))&&(i0.i0.i0.i1.i0.u10.p32==1))||(((i0.i1.i0.i0.u22.p91==1)&&(i1.i0.i0.u29.p132==1))&&(i1.u32.p160==1)))) * !((!(!(EG(!((((((((((i0.i0.i1.i0.u17.p65==1)||(i0.i1.i0.u24.p112==1))||(((i0.i0.i1.i0.i0.u15.p56==1)&&(i0.i0.i1.i0.i0.u16.p62==1))&&(i0.i0.i1.i0.u17.p70==1)))||(i0.i0.i1.i0.i0.u15.p53==1))||(i0.i0.i0.i1.i0.i0.u9.p21==1))||(((i1.i0.i0.u29.p134==1)&&(i1.i0.i0.u30.p140==1))&&(i1.i0.u31.p149==1)))||(i0.i0.i0.i1.u41.p8==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i0.i0.i1.i0.u10.p30==1)))))) + ((((((((((i0.i0.i0.i1.i0.i0.u8.p20==0)&&(i1.i0.i0.u30.p138==0))&&(((i0.i1.i0.u24.p110==0)||(i0.i1.u25.p121==0))||(i1.i0.u31.p144==0)))&&(i0.i0.i1.u18.p75==0))&&(i0.i0.i0.i1.i0.i0.u43.p10==0))&&(i0.i0.i1.i0.i0.u15.p58==0))&&(((i0.i1.i0.i0.u22.p91==0)||(i1.i0.i0.u29.p132==0))||(i1.u32.p160==0)))&&(i0.i0.i0.i1.u11.p41==0))&&(i0.i1.i0.i0.u45.p88==0))&&(i0.i1.i0.u24.p107==0)))))) + EG(!((!(!(EG(!((((((((((i0.i0.i1.i0.u17.p65==1)||(i0.i1.i0.u24.p112==1))||(((i0.i0.i1.i0.i0.u15.p56==1)&&(i0.i0.i1.i0.i0.u16.p62==1))&&(i0.i0.i1.i0.u17.p70==1)))||(i0.i0.i1.i0.i0.u15.p53==1))||(i0.i0.i0.i1.i0.i0.u9.p21==1))||(((i1.i0.i0.u29.p134==1)&&(i1.i0.i0.u30.p140==1))&&(i1.i0.u31.p149==1)))||(i0.i0.i0.i1.u41.p8==1))||(i0.i0.i0.i1.u11.p40==1))||(i0.i0.i0.i1.i0.u10.p30==1)))))) + ((((((((((i0.i0.i0.i1.i0.i0.u8.p20==0)&&(i1.i0.i0.u30.p138==0))&&(((i0.i1.i0.u24.p110==0)||(i0.i1.u25.p121==0))||(i1.i0.u31.p144==0)))&&(i0.i0.i1.u18.p75==0))&&(i0.i0.i0.i1.i0.i0.u43.p10==0))&&(i0.i0.i1.i0.i0.u15.p58==0))&&(((i0.i1.i0.i0.u22.p91==0)||(i1.i0.i0.u29.p132==0))||(i1.u32.p160==0)))&&(i0.i0.i0.i1.u11.p41==0))&&(i0.i1.i0.i0.u45.p88==0))&&(i0.i1.i0.u24.p107==0)))))))))) * !(!(!(EX(!(!(E(TRUE U !(((((((((i0.i0.i1.i0.u33.p48==1)||((i0.i0.i0.u4.p4==1)&&(i0.i0.i0.i1.i0.u10.p27==1)))||(i0.i0.i1.i0.u17.p68==1))||(i0.i1.u38.p86==1))||(((i0.i0.i1.i0.i0.u15.p52==1)&&(i0.i1.i0.i0.u22.p96==1))&&(i0.i1.u25.p120==1)))||(i0.i0.i1.i0.i0.u16.p61==1))||(i0.i1.i0.u24.p108==1))||(i0.i1.i0.i0.u22.p94==1))))))))))),!(!(EX(!(((((((((i0.i1.u25.p114==1)||(i0.i0.i1.u18.p81==1))||(i0.i0.i0.i1.i0.i0.u8.p20==1))||(i1.i0.u31.p148==1))||(i1.i0.u48.p126==1))||(i1.i0.u31.p143==1))||(i0.i0.i1.i0.i0.u16.p60==1))||(i0.i0.i0.i1.i0.i0.u8.p15==1)))))))] = FALSE)

Reverse transition relation is NOT exact ! Due to transitions i0.i0.i0.u4.t128, i0.i0.i0.i1.u11.t8, i0.i0.i0.i1.u11.t9, i0.i0.i0.i1.u11.t10, i0.i0.i0.i1.u11.t11, i0.i0.i0.i1.u11.t112, i0.i0.i0.i1.u11.t115, i0.i0.i0.i1.i0.u10.t4, i0.i0.i0.i1.i0.u10.t5, i0.i0.i0.i1.i0.u10.t6, i0.i0.i0.i1.i0.u10.t7, i0.i0.i0.i1.i0.u10.t118, i0.i0.i0.i1.i0.u10.t120, i0.i0.i0.i1.i0.i0.u8.t0, i0.i0.i0.i1.i0.i0.u8.t1, i0.i0.i0.i1.i0.i0.u8.t2, i0.i0.i0.i1.i0.i0.u8.t3, i0.i0.i0.i1.i0.i0.u8.t125, i0.i0.i0.i1.i0.i0.u8.t127, i0.i0.i0.i1.i0.i0.u9.t122, i0.i0.i0.i1.i0.i0.u9.t123, i0.i0.i1.u18.t20, i0.i0.i1.u18.t21, i0.i0.i1.u18.t22, i0.i0.i1.u18.t23, i0.i0.i1.u18.t92, i0.i0.i1.u18.t95, i0.i0.i1.i0.u17.t16, i0.i0.i1.i0.u17.t17, i0.i0.i1.i0.u17.t18, i0.i0.i1.i0.u17.t19, i0.i0.i1.i0.u17.t98, i0.i0.i1.i0.u17.t100, i0.i0.i1.i0.i0.u15.t12, i0.i0.i1.i0.i0.u15.t13, i0.i0.i1.i0.i0.u15.t14, i0.i0.i1.i0.i0.u15.t15, i0.i0.i1.i0.i0.u15.t105, i0.i0.i1.i0.i0.u15.t107, i0.i0.i1.i0.i0.u16.t102, i0.i0.i1.i0.i0.u16.t103, i0.i1.u25.t32, i0.i1.u25.t33, i0.i1.u25.t34, i0.i1.u25.t35, i0.i1.u25.t72, i0.i1.u25.t75, i0.i1.i0.u24.t28, i0.i1.i0.u24.t29, i0.i1.i0.u24.t30, i0.i1.i0.u24.t31, i0.i1.i0.u24.t78, i0.i1.i0.u24.t80, i0.i1.i0.i0.u22.t24, i0.i1.i0.i0.u22.t25, i0.i1.i0.i0.u22.t26, i0.i1.i0.i0.u22.t27, i0.i1.i0.i0.u22.t85, i0.i1.i0.i0.u22.t87, i0.i1.i0.i0.u23.t82, i0.i1.i0.i0.u23.t83, i1.u32.t44, i1.u32.t45, i1.u32.t46, i1.u32.t47, i1.u32.t52, i1.u32.t55, i1.i0.u31.t40, i1.i0.u31.t41, i1.i0.u31.t42, i1.i0.u31.t43, i1.i0.u31.t58, i1.i0.u31.t60, i1.i0.i0.u29.t36, i1.i0.i0.u29.t37, i1.i0.i0.u29.t38, i1.i0.i0.u29.t39, i1.i0.i0.u29.t65, i1.i0.i0.u29.t67, i1.i0.i0.u30.t62, i1.i0.i0.u30.t63, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/66/81/147

Detected timeout of ITS tools.

[2021-05-15 22:35:21] [INFO ] Flatten gal took : 24 ms

[2021-05-15 22:35:21] [INFO ] Input system was already deterministic with 183 transitions.

[2021-05-15 22:35:21] [INFO ] Transformed 163 places.

[2021-05-15 22:35:21] [INFO ] Transformed 183 transitions.

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit/bin//..//greatspn//bin/pinvar, /home/mcc/execution/gspn], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit/bin//..//greatspn//bin/RGMEDD2, /home/mcc/execution/gspn, -META, -varord-only], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Using order generated by GreatSPN with heuristic : META

[2021-05-15 22:35:21] [INFO ] Time to serialize gal into /tmp/CTLFireability11967799795505405024.gal : 3 ms

[2021-05-15 22:35:21] [INFO ] Time to serialize properties into /tmp/CTLFireability10527674527763108819.ctl : 4 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/CTLFireability11967799795505405024.gal, -t, CGAL, -ctl, /tmp/CTLFireability10527674527763108819.ctl, --load-order, /home/mcc/execution/model.ord, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /tmp/CTLFireability11967799795505405024.gal -t CGAL -ctl /tmp/CTLFireability10527674527763108819.ctl --load-order /home/mcc/execution/model.ord --gen-order FOLLOW

Successfully loaded order from file /home/mcc/execution/model.ord

No direction supplied, using forward translation only.

Parsed 12 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.61506e+12,124.714,2051084,2,404414,5,6.07581e+06,6,0,837,1.33926e+07,0

Converting to forward existential form...Done !

original formula: (EF((((((((((((((p0==1)||(p83==1))||(p35==1))||(p118==1))||(p40==1))||(p104==1))||(p9==1))||(((p91==1)&&(p135==1))&&(p160==1)))||(p111==1))||(((p6==1)&&(p15==1))&&(p43==1)))||(p15==1))&&((((p80==1)||(p53==1))||(((p107==1)&&(p121==1))&&(p144==1)))||(p77==1)))&&((((p6==1)&&(p15==1))&&(p42==1))||(p108==1)))) * ((AF(AX(((((((((p114==1)||(p81==1))||(p20==1))||(p148==1))||(p126==1))||(p143==1))||(p60==1))||(p15==1)))) + !(AX(AG(((((((((p48==1)||((p4==1)&&(p27==1)))||(p68==1))||(p86==1))||(((p52==1)&&(p96==1))&&(p120==1)))||(p61==1))||(p108==1))||(p94==1)))))) + !(A(((((p18==1)&&(p23==1))&&(p32==1))||(((p91==1)&&(p132==1))&&(p160==1))) U (!(AF((((((((((p65==1)||(p112==1))||(((p56==1)&&(p62==1))&&(p70==1)))||(p53==1))||(p21==1))||(((p134==1)&&(p140==1))&&(p149==1)))||(p8==1))||(p40==1))||(p30==1)))) + ((((((((((p20==0)&&(p138==0))&&(((p110==0)||(p121==0))||(p144==0)))&&(p75==0))&&(p10==0))&&(p58==0))&&(((p91==0)||(p132==0))||(p160==0)))&&(p41==0))&&(p88==0))&&(p107==0)))))))

=> equivalent forward existential formula: ([(Init * !(E(TRUE U (((((((((((((p0==1)||(p83==1))||(p35==1))||(p118==1))||(p40==1))||(p104==1))||(p9==1))||(((p91==1)&&(p135==1))&&(p160==1)))||(p111==1))||(((p6==1)&&(p15==1))&&(p43==1)))||(p15==1))&&((((p80==1)||(p53==1))||(((p107==1)&&(p121==1))&&(p144==1)))||(p77==1)))&&((((p6==1)&&(p15==1))&&(p42==1))||(p108==1))))))] = FALSE * [FwdG(((Init * !(!(!((E(!((!(!(EG(!((((((((((p65==1)||(p112==1))||(((p56==1)&&(p62==1))&&(p70==1)))||(p53==1))||(p21==1))||(((p134==1)&&(p140==1))&&(p149==1)))||(p8==1))||(p40==1))||(p30==1)))))) + ((((((((((p20==0)&&(p138==0))&&(((p110==0)||(p121==0))||(p144==0)))&&(p75==0))&&(p10==0))&&(p58==0))&&(((p91==0)||(p132==0))||(p160==0)))&&(p41==0))&&(p88==0))&&(p107==0)))) U (!(((((p18==1)&&(p23==1))&&(p32==1))||(((p91==1)&&(p132==1))&&(p160==1)))) * !((!(!(EG(!((((((((((p65==1)||(p112==1))||(((p56==1)&&(p62==1))&&(p70==1)))||(p53==1))||(p21==1))||(((p134==1)&&(p140==1))&&(p149==1)))||(p8==1))||(p40==1))||(p30==1)))))) + ((((((((((p20==0)&&(p138==0))&&(((p110==0)||(p121==0))||(p144==0)))&&(p75==0))&&(p10==0))&&(p58==0))&&(((p91==0)||(p132==0))||(p160==0)))&&(p41==0))&&(p88==0))&&(p107==0)))))) + EG(!((!(!(EG(!((((((((((p65==1)||(p112==1))||(((p56==1)&&(p62==1))&&(p70==1)))||(p53==1))||(p21==1))||(((p134==1)&&(p140==1))&&(p149==1)))||(p8==1))||(p40==1))||(p30==1)))))) + ((((((((((p20==0)&&(p138==0))&&(((p110==0)||(p121==0))||(p144==0)))&&(p75==0))&&(p10==0))&&(p58==0))&&(((p91==0)||(p132==0))||(p160==0)))&&(p41==0))&&(p88==0))&&(p107==0)))))))))) * !(!(!(EX(!(!(E(TRUE U !(((((((((p48==1)||((p4==1)&&(p27==1)))||(p68==1))||(p86==1))||(((p52==1)&&(p96==1))&&(p120==1)))||(p61==1))||(p108==1))||(p94==1))))))))))),!(!(EX(!(((((((((p114==1)||(p81==1))||(p20==1))||(p148==1))||(p126==1))||(p143==1))||(p60==1))||(p15==1)))))))] = FALSE)

Reverse transition relation is NOT exact ! Due to transitions t0, t1, t2, t3, t4, t5, t6, t7, t8, t9, t10, t11, t12, t13, t14, t15, t16, t17, t18, t19, t20, t21, t22, t23, t24, t25, t26, t27, t28, t29, t30, t31, t32, t33, t34, t35, t36, t37, t38, t39, t40, t41, t42, t43, t44, t45, t46, t47, t52, t55, t58, t60, t62, t63, t65, t67, t72, t75, t78, t80, t82, t83, t85, t87, t92, t95, t98, t100, t102, t103, t105, t107, t112, t115, t118, t120, t122, t123, t125, t127, t128, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/102/81/183

Detected timeout of ITS tools.

BK_STOP 1621119326977

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ CTLFireability = StateSpace ]]

+ /home/mcc/BenchKit/bin//..//runeclipse.sh /home/mcc/execution CTLFireability -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

++ cut -d . -f 9

++ ls /home/mcc/BenchKit/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202104292328.jar

+ VERSION=0

+ echo 'Running Version 0'

+ /home/mcc/BenchKit/bin//..//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination CTLFireability -spotpath /home/mcc/BenchKit/bin//..//ltlfilt -z3path /home/mcc/BenchKit/bin//..//z3/bin/z3 -yices2path /home/mcc/BenchKit/bin//..//yices/bin/yices -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ShieldRVs-PT-004B"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is ShieldRVs-PT-004B, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r235-smll-162106564400058"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ShieldRVs-PT-004B.tgz

mv ShieldRVs-PT-004B execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;