About the Execution of 2020-gold for LamportFastMutEx-PT-6

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 3200.619 | 289496.00 | 268958.00 | 6523.10 | 6 5 1 6 30 6 6 30 1 1 0 1 1 1 1 1 | normal |

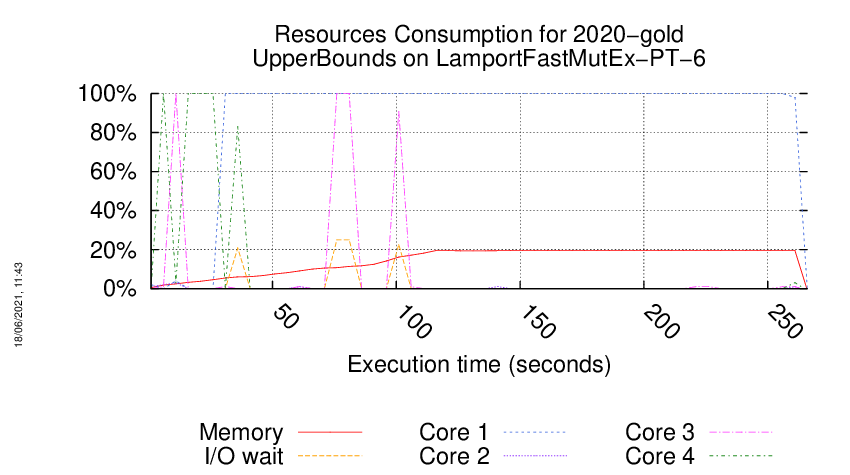

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2021-input.r131-tall-162075426300085.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2021-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

.............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool gold2020

Input is LamportFastMutEx-PT-6, examination is UpperBounds

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r131-tall-162075426300085

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 1.6M

-rw-r--r-- 1 mcc users 58K May 5 16:58 CTLCardinality.txt

-rw-r--r-- 1 mcc users 312K May 10 09:43 CTLCardinality.xml

-rw-r--r-- 1 mcc users 127K May 5 16:58 CTLFireability.txt

-rw-r--r-- 1 mcc users 635K May 10 09:43 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 6 14:48 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 12K Apr 26 07:42 LTLCardinality.txt

-rw-r--r-- 1 mcc users 52K Apr 26 07:42 LTLCardinality.xml

-rw-r--r-- 1 mcc users 12K Apr 26 07:42 LTLFireability.txt

-rw-r--r-- 1 mcc users 52K Apr 26 07:42 LTLFireability.xml

-rw-r--r-- 1 mcc users 6.1K Mar 27 06:04 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 25K Mar 27 06:04 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 16K Mar 25 07:13 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 70K Mar 25 07:13 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 3.3K Mar 22 09:15 UpperBounds.txt

-rw-r--r-- 1 mcc users 8.2K Mar 22 09:15 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 5 16:51 equiv_col

-rw-r--r-- 1 mcc users 2 May 5 16:51 instance

-rw-r--r-- 1 mcc users 6 May 5 16:51 iscolored

-rw-r--r-- 1 mcc users 208K May 5 16:51 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of positive values

NUM_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-00

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-01

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-02

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-03

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-04

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-05

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-06

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-07

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-08

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-09

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-10

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-11

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-12

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-13

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-14

FORMULA_NAME LamportFastMutEx-PT-6-UpperBounds-15

=== Now, execution of the tool begins

BK_START 1620908168050

[2021-05-13 12:16:09] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, UpperBounds, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2021-05-13 12:16:09] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2021-05-13 12:16:09] [INFO ] Load time of PNML (sax parser for PT used): 76 ms

[2021-05-13 12:16:09] [INFO ] Transformed 217 places.

[2021-05-13 12:16:09] [INFO ] Transformed 420 transitions.

[2021-05-13 12:16:09] [INFO ] Found NUPN structural information;

[2021-05-13 12:16:09] [INFO ] Completing missing partition info from NUPN : creating a component with [P_start_1_0, P_start_1_1, P_start_1_2, P_start_1_3, P_start_1_4, P_start_1_5, P_start_1_6, P_b_0_false, P_b_0_true, P_b_1_false, P_b_1_true, P_b_2_false, P_b_2_true, P_b_3_false, P_b_3_true, P_b_4_false, P_b_4_true, P_b_5_false, P_b_5_true, P_b_6_false, P_b_6_true, P_setx_3_0, P_setx_3_1, P_setx_3_2, P_setx_3_3, P_setx_3_4, P_setx_3_5, P_setx_3_6, P_setbi_5_0, P_setbi_5_1, P_setbi_5_2, P_setbi_5_3, P_setbi_5_4, P_setbi_5_5, P_setbi_5_6, P_ify0_4_0, P_ify0_4_1, P_ify0_4_2, P_ify0_4_3, P_ify0_4_4, P_ify0_4_5, P_ify0_4_6, P_sety_9_0, P_sety_9_1, P_sety_9_2, P_sety_9_3, P_sety_9_4, P_sety_9_5, P_sety_9_6, P_ifxi_10_0, P_ifxi_10_1, P_ifxi_10_2, P_ifxi_10_3, P_ifxi_10_4, P_ifxi_10_5, P_ifxi_10_6, P_setbi_11_0, P_setbi_11_1, P_setbi_11_2, P_setbi_11_3, P_setbi_11_4, P_setbi_11_5, P_setbi_11_6, P_fordo_12_0, P_fordo_12_1, P_fordo_12_2, P_fordo_12_3, P_fordo_12_4, P_fordo_12_5, P_fordo_12_6, P_wait_0_0, P_wait_0_1, P_wait_0_2, P_wait_0_3, P_wait_0_4, P_wait_0_5, P_wait_0_6, P_wait_1_0, P_wait_1_1, P_wait_1_2, P_wait_1_3, P_wait_1_4, P_wait_1_5, P_wait_1_6, P_wait_2_0, P_wait_2_1, P_wait_2_2, P_wait_2_3, P_wait_2_4, P_wait_2_5, P_wait_2_6, P_wait_3_0, P_wait_3_1, P_wait_3_2, P_wait_3_3, P_wait_3_4, P_wait_3_5, P_wait_3_6, P_wait_4_0, P_wait_4_1, P_wait_4_2, P_wait_4_3, P_wait_4_4, P_wait_4_5, P_wait_4_6, P_wait_5_0, P_wait_5_1, P_wait_5_2, P_wait_5_3, P_wait_5_4, P_wait_5_5, P_wait_5_6, P_wait_6_0, P_wait_6_1, P_wait_6_2, P_wait_6_3, P_wait_6_4, P_wait_6_5, P_wait_6_6, P_await_13_0, P_await_13_1, P_await_13_2, P_await_13_3, P_await_13_4, P_await_13_5, P_await_13_6, P_done_0_0, P_done_0_1, P_done_0_2, P_done_0_3, P_done_0_4, P_done_0_5, P_done_0_6, P_done_1_0, P_done_1_1, P_done_1_2, P_done_1_3, P_done_1_4, P_done_1_5, P_done_1_6, P_done_2_0, P_done_2_1, P_done_2_2, P_done_2_3, P_done_2_4, P_done_2_5, P_done_2_6, P_done_3_0, P_done_3_1, P_done_3_2, P_done_3_3, P_done_3_4, P_done_3_5, P_done_3_6, P_done_4_0, P_done_4_1, P_done_4_2, P_done_4_3, P_done_4_4, P_done_4_5, P_done_4_6, P_done_5_0, P_done_5_1, P_done_5_2, P_done_5_3, P_done_5_4, P_done_5_5, P_done_5_6, P_done_6_0, P_done_6_1, P_done_6_2, P_done_6_3, P_done_6_4, P_done_6_5, P_done_6_6, P_ifyi_15_0, P_ifyi_15_1, P_ifyi_15_2, P_ifyi_15_3, P_ifyi_15_4, P_ifyi_15_5, P_ifyi_15_6, P_awaity_0, P_awaity_1, P_awaity_2, P_awaity_3, P_awaity_4, P_awaity_5, P_awaity_6, P_CS_21_0, P_CS_21_1, P_CS_21_2, P_CS_21_3, P_CS_21_4, P_CS_21_5, P_CS_21_6, P_setbi_24_0, P_setbi_24_1, P_setbi_24_2, P_setbi_24_3, P_setbi_24_4, P_setbi_24_5, P_setbi_24_6]

[2021-05-13 12:16:09] [INFO ] Parsed PT model containing 217 places and 420 transitions in 120 ms.

Deduced a syphon composed of 41 places in 2 ms

Reduce places removed 41 places and 66 transitions.

Parsed 16 properties from file /home/mcc/execution/UpperBounds.xml in 19 ms.

Finished random walk after 0 steps, including 0 resets, run visited all 0 properties in 1 ms. (steps per millisecond=0 )

[2021-05-13 12:16:09] [INFO ] Flatten gal took : 77 ms

[2021-05-13 12:16:10] [INFO ] Applying decomposition

[2021-05-13 12:16:10] [INFO ] Flatten gal took : 27 ms

[2021-05-13 12:16:10] [INFO ] Time to serialize gal into /home/mcc/execution/UpperBounds.pnml.gal : 15 ms

[2021-05-13 12:16:10] [INFO ] Time to serialize properties into /home/mcc/execution/UpperBounds.prop : 0 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/UpperBounds.pnml.gal, -t, CGAL, -reachable-file, UpperBounds.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/UpperBounds.pnml.gal -t CGAL -reachable-file UpperBounds.prop --nowitness --gen-order FOLLOW

Loading property file UpperBounds.prop.

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-00 with value :P_setbi_24_1+P_setbi_24_2+P_setbi_24_3+P_setbi_24_4+P_setbi_24_5+P_setbi_24_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-01 with value :P_awaity_1+P_awaity_2+P_awaity_3+P_awaity_4+P_awaity_5+P_awaity_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-02 with value :P_CS_21_1+P_CS_21_2+P_CS_21_3+P_CS_21_4+P_CS_21_5+P_CS_21_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-03 with value :P_start_1_1+P_start_1_2+P_start_1_3+P_start_1_4+P_start_1_5+P_start_1_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-04 with value :P_wait_1_1+P_wait_1_2+P_wait_1_3+P_wait_1_4+P_wait_1_5+P_wait_1_6+P_wait_2_1+P_wait_2_2+P_wait_2_3+P_wait_2_4+P_wait_2_5+P_wait_2_6+P_wait_3_1+P_wait_3_2+P_wait_3_3+P_wait_3_4+P_wait_3_5+P_wait_3_6+P_wait_4_1+P_wait_4_2+P_wait_4_3+P_wait_4_4+P_wait_4_5+P_wait_4_6+P_wait_5_1+P_wait_5_2+P_wait_5_3+P_wait_5_4+P_wait_5_5+P_wait_5_6+P_wait_6_1+P_wait_6_2+P_wait_6_3+P_wait_6_4+P_wait_6_5+P_wait_6_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-05 with value :P_start_1_1+P_start_1_2+P_start_1_3+P_start_1_4+P_start_1_5+P_start_1_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-06 with value :P_ifxi_10_1+P_ifxi_10_2+P_ifxi_10_3+P_ifxi_10_4+P_ifxi_10_5+P_ifxi_10_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-07 with value :P_wait_1_1+P_wait_1_2+P_wait_1_3+P_wait_1_4+P_wait_1_5+P_wait_1_6+P_wait_2_1+P_wait_2_2+P_wait_2_3+P_wait_2_4+P_wait_2_5+P_wait_2_6+P_wait_3_1+P_wait_3_2+P_wait_3_3+P_wait_3_4+P_wait_3_5+P_wait_3_6+P_wait_4_1+P_wait_4_2+P_wait_4_3+P_wait_4_4+P_wait_4_5+P_wait_4_6+P_wait_5_1+P_wait_5_2+P_wait_5_3+P_wait_5_4+P_wait_5_5+P_wait_5_6+P_wait_6_1+P_wait_6_2+P_wait_6_3+P_wait_6_4+P_wait_6_5+P_wait_6_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-08 with value :P_b_3_true

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-09 with value :P_ify0_4_2

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-10 with value :

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-11 with value :P_wait_3_3

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-12 with value :P_await_13_1

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-13 with value :P_ify0_4_2

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-14 with value :P_ifxi_10_6

Read [bounds] property : LamportFastMutEx-PT-6-UpperBounds-15 with value :P_setbi_24_3

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

petri\_inst\_inst,5.47232e+11,278.773,3008168,2,437034,5,8.32865e+06,6,0,1060,1.06847e+07,0

Total reachable state count : 547231759144

Verifying 16 reachability properties.

Min sum of variable value : 0

Maximum sum along a path : 6

Bounds property LamportFastMutEx-PT-6-UpperBounds-00 :0 <= P_setbi_24_1+P_setbi_24_2+P_setbi_24_3+P_setbi_24_4+P_setbi_24_5+P_setbi_24_6 <= 6

FORMULA LamportFastMutEx-PT-6-UpperBounds-00 6 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-00,0,279.328,3008168,1,0,7,8.32865e+06,9,1,1494,1.06847e+07,4

Min sum of variable value : 0

Maximum sum along a path : 5

Bounds property LamportFastMutEx-PT-6-UpperBounds-01 :0 <= P_awaity_1+P_awaity_2+P_awaity_3+P_awaity_4+P_awaity_5+P_awaity_6 <= 5

FORMULA LamportFastMutEx-PT-6-UpperBounds-01 5 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-01,0,279.869,3008168,1,0,8,8.32865e+06,10,1,1760,1.06847e+07,5

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-02 :0 <= P_CS_21_1+P_CS_21_2+P_CS_21_3+P_CS_21_4+P_CS_21_5+P_CS_21_6 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-02 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-02,0,280.392,3008168,1,0,9,8.32865e+06,11,1,2004,1.06847e+07,6

Min sum of variable value : 0

Maximum sum along a path : 6

Bounds property LamportFastMutEx-PT-6-UpperBounds-03 :0 <= P_start_1_1+P_start_1_2+P_start_1_3+P_start_1_4+P_start_1_5+P_start_1_6 <= 6

FORMULA LamportFastMutEx-PT-6-UpperBounds-03 6 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-03,0,280.925,3008168,1,0,10,8.32865e+06,12,1,2288,1.06847e+07,7

Min sum of variable value : 0

Maximum sum along a path : 30

Bounds property LamportFastMutEx-PT-6-UpperBounds-04 :0 <= P_wait_1_1+P_wait_1_2+P_wait_1_3+P_wait_1_4+P_wait_1_5+P_wait_1_6+P_wait_2_1+P_wait_2_2+P_wait_2_3+P_wait_2_4+P_wait_2_5+P_wait_2_6+P_wait_3_1+P_wait_3_2+P_wait_3_3+P_wait_3_4+P_wait_3_5+P_wait_3_6+P_wait_4_1+P_wait_4_2+P_wait_4_3+P_wait_4_4+P_wait_4_5+P_wait_4_6+P_wait_5_1+P_wait_5_2+P_wait_5_3+P_wait_5_4+P_wait_5_5+P_wait_5_6+P_wait_6_1+P_wait_6_2+P_wait_6_3+P_wait_6_4+P_wait_6_5+P_wait_6_6 <= 30

FORMULA LamportFastMutEx-PT-6-UpperBounds-04 30 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-04,0,281.594,3008168,1,0,11,8.32865e+06,13,1,2677,1.06847e+07,8

Min sum of variable value : 0

Maximum sum along a path : 6

Bounds property LamportFastMutEx-PT-6-UpperBounds-05 :0 <= P_start_1_1+P_start_1_2+P_start_1_3+P_start_1_4+P_start_1_5+P_start_1_6 <= 6

FORMULA LamportFastMutEx-PT-6-UpperBounds-05 6 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-05,0,281.595,3008168,1,0,11,8.32865e+06,13,1,2677,1.06847e+07,8

Min sum of variable value : 0

Maximum sum along a path : 6

Bounds property LamportFastMutEx-PT-6-UpperBounds-06 :0 <= P_ifxi_10_1+P_ifxi_10_2+P_ifxi_10_3+P_ifxi_10_4+P_ifxi_10_5+P_ifxi_10_6 <= 6

FORMULA LamportFastMutEx-PT-6-UpperBounds-06 6 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-06,0,282.121,3008168,1,0,12,8.32865e+06,14,1,2899,1.06847e+07,9

Min sum of variable value : 0

Maximum sum along a path : 30

Bounds property LamportFastMutEx-PT-6-UpperBounds-07 :0 <= P_wait_1_1+P_wait_1_2+P_wait_1_3+P_wait_1_4+P_wait_1_5+P_wait_1_6+P_wait_2_1+P_wait_2_2+P_wait_2_3+P_wait_2_4+P_wait_2_5+P_wait_2_6+P_wait_3_1+P_wait_3_2+P_wait_3_3+P_wait_3_4+P_wait_3_5+P_wait_3_6+P_wait_4_1+P_wait_4_2+P_wait_4_3+P_wait_4_4+P_wait_4_5+P_wait_4_6+P_wait_5_1+P_wait_5_2+P_wait_5_3+P_wait_5_4+P_wait_5_5+P_wait_5_6+P_wait_6_1+P_wait_6_2+P_wait_6_3+P_wait_6_4+P_wait_6_5+P_wait_6_6 <= 30

FORMULA LamportFastMutEx-PT-6-UpperBounds-07 30 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-07,0,282.122,3008168,1,0,12,8.32865e+06,14,1,2899,1.06847e+07,9

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-08 :0 <= P_b_3_true <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-08 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-08,0,282.67,3008168,1,0,13,8.32865e+06,15,1,3136,1.06847e+07,10

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-09 :0 <= P_ify0_4_2 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-09 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-09,0,283.135,3008168,1,0,14,8.32865e+06,16,1,3337,1.06847e+07,11

Min sum of variable value : 0

Maximum sum along a path : 0

Bounds property LamportFastMutEx-PT-6-UpperBounds-10 :0 <= <= 0

FORMULA LamportFastMutEx-PT-6-UpperBounds-10 0 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-10,0,283.135,3008168,1,0,14,8.32865e+06,17,1,3337,1.06847e+07,11

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-11 :0 <= P_wait_3_3 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-11 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-11,0,283.682,3008168,1,0,15,8.32865e+06,18,1,3626,1.06847e+07,12

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-12 :0 <= P_await_13_1 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-12 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-12,0,284.229,3008168,1,0,16,8.32865e+06,19,1,3955,1.06847e+07,13

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-13 :0 <= P_ify0_4_2 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-13 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-13,0,284.23,3008168,1,0,16,8.32865e+06,19,1,3955,1.06847e+07,13

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-14 :0 <= P_ifxi_10_6 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-14 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-14,0,284.355,3008168,1,0,17,8.32865e+06,20,1,4098,1.06847e+07,14

Min sum of variable value : 0

Maximum sum along a path : 1

Bounds property LamportFastMutEx-PT-6-UpperBounds-15 :0 <= P_setbi_24_3 <= 1

FORMULA LamportFastMutEx-PT-6-UpperBounds-15 1 TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-UpperBounds-15,0,284.908,3008168,1,0,18,8.32865e+06,21,1,4331,1.06847e+07,15

BK_STOP 1620908457546

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ UpperBounds = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution UpperBounds -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination UpperBounds -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="LamportFastMutEx-PT-6"

export BK_EXAMINATION="UpperBounds"

export BK_TOOL="gold2020"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool gold2020"

echo " Input is LamportFastMutEx-PT-6, examination is UpperBounds"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r131-tall-162075426300085"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/LamportFastMutEx-PT-6.tgz

mv LamportFastMutEx-PT-6 execution

cd execution

if [ "UpperBounds" = "ReachabilityDeadlock" ] || [ "UpperBounds" = "UpperBounds" ] || [ "UpperBounds" = "QuasiLiveness" ] || [ "UpperBounds" = "StableMarking" ] || [ "UpperBounds" = "Liveness" ] || [ "UpperBounds" = "OneSafe" ] || [ "UpperBounds" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "UpperBounds" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "UpperBounds" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "UpperBounds.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property UpperBounds.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "UpperBounds.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "UpperBounds" = "ReachabilityDeadlock" ] || [ "UpperBounds" = "QuasiLiveness" ] || [ "UpperBounds" = "StableMarking" ] || [ "UpperBounds" = "Liveness" ] || [ "UpperBounds" = "OneSafe" ] ; then

echo "FORMULA_NAME UpperBounds"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;