About the Execution of GreatSPN for FamilyReunion-COL-L00050M0005C002P002G001

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 13642.516 | 326212.00 | 1046588.00 | 411.80 | [undef] | Cannot compute |

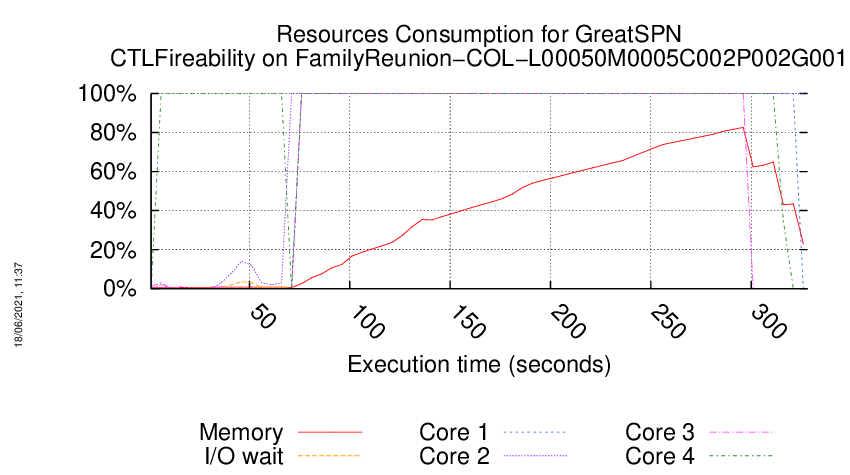

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2021-input.r079-tall-162048870000858.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2021-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

...................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool gspn

Input is FamilyReunion-COL-L00050M0005C002P002G001, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r079-tall-162048870000858

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 476K

-rw-r--r-- 1 mcc users 12K May 5 16:58 CTLCardinality.txt

-rw-r--r-- 1 mcc users 122K May 10 09:43 CTLCardinality.xml

-rw-r--r-- 1 mcc users 11K May 5 16:58 CTLFireability.txt

-rw-r--r-- 1 mcc users 53K May 10 09:43 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 6 14:48 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 7.0K May 6 14:48 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.4K Mar 28 16:09 LTLCardinality.txt

-rw-r--r-- 1 mcc users 23K Mar 28 16:09 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K Mar 28 16:09 LTLFireability.txt

-rw-r--r-- 1 mcc users 16K Mar 28 16:09 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.7K Mar 23 10:46 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 18K Mar 23 10:46 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 3.9K Mar 22 18:50 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K Mar 22 18:50 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.0K Mar 22 09:11 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.0K Mar 22 09:11 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 5 16:51 equiv_pt

-rw-r--r-- 1 mcc users 24 May 5 16:51 instance

-rw-r--r-- 1 mcc users 5 May 5 16:51 iscolored

-rw-r--r-- 1 mcc users 137K May 5 16:51 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-00

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-01

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-02

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-03

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-04

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-05

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-06

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-07

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-08

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-09

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-10

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-11

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-12

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-13

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-14

FORMULA_NAME FamilyReunion-COL-L00050M0005C002P002G001-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1620882105802

----------------------------------------------------------------------

GreatSPN-meddly tool, MCC 2021

----------------------------------------------------------------------

Running FamilyReunion-COL-L00050M0005C002P002G001

IS_COLORED=1

IS_NUPN=

LOADING model.pnml ...

MODEL CLASS: SYMMETRIC NET

PLACES: 104

TRANSITIONS: 66

CONSTANTS: 0

TEMPLATE VARS: 0

COLOR CLASSES: 11

COLOR VARS: 6

ARCS: 198

LOADING TIME: 0.431

UNFOLDING COLORS...

MODEL CLASS: P/T NET

PLACES: 12245

TRANSITIONS: 10560

CONSTANTS: 0

TEMPLATE VARS: 0

ARCS: 32238

UNFOLDING TIME: 0.687

SAVING AS /home/mcc/execution/model.(net/def) ...

SAVING TIME: 0.357

SAVING NAME MAP FILE /home/mcc/execution/model.id2name ...

SAVING UNFOLDING MAP FILE /home/mcc/execution/model.unfmap ...

TOTAL TIME: 1.703

OK.

----------------------------------------------------------------------

GreatSPN/Meddly.

Copyright (C) 1987-2020, University of Torino, Italy.

Based on MEDDLY version 0.16.0

Copyright (C) 2009, Iowa State University Research Foundation, Inc.

website: http://meddly.sourceforge.net

Process ID: 574

MODEL NAME: /home/mcc/execution/model

12245 places, 10560 transitions.

No place bound informations found.

No place bound informations found.

No place bound informations found.

No place bound informations found.

Creating all event NSFs..

Creating all event NSFs..

Creating all event NSFs..

Creating all event NSFs..

Split: SplitSubtract

Start RS construction.

Split: SplitSubtract

Start RS construction.

Split: SplitSubtract

Start RS construction.

Split: SplitSubtract

Start RS construction.

CANNOT_COMPUTE

EXITCODE: 87

----------------------------------------------------------------------

BK_STOP 1620882432014

--------------------

content from stderr:

May 13, 2021 5:02:57 AM com.sun.xml.bind.v2.runtime.reflect.opt.AccessorInjector

INFO: The optimized code generation is disabled

MEDDLY ERROR: Insufficient memory

MEDDLY ERROR: Insufficient memory

MEDDLY ERROR: Insufficient memory

MEDDLY ERROR: Insufficient memory

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FamilyReunion-COL-L00050M0005C002P002G001"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="gspn"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool gspn"

echo " Input is FamilyReunion-COL-L00050M0005C002P002G001, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r079-tall-162048870000858"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/FamilyReunion-COL-L00050M0005C002P002G001.tgz

mv FamilyReunion-COL-L00050M0005C002P002G001 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;