About the Execution of ITS-Tools for DLCflexbar-PT-6a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 630.239 | 18824.00 | 28514.00 | 75.10 | FFFTFFFFTTFFTFTF | normal |

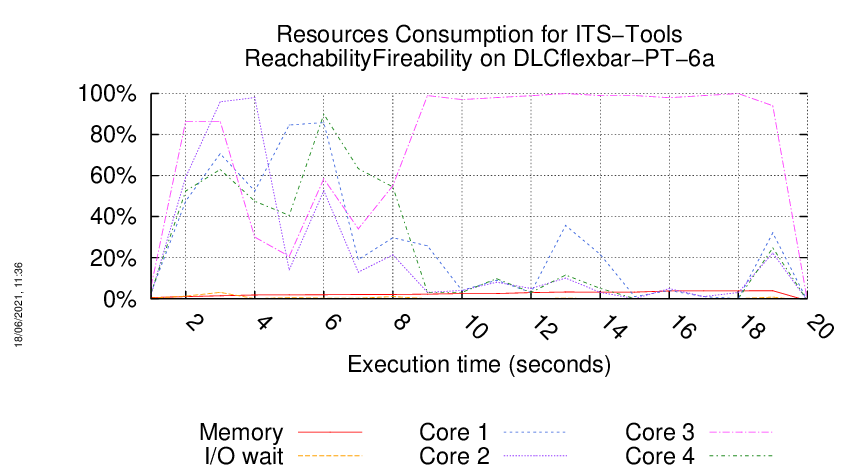

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2021-input.r064-tall-162038396900231.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2021-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

.................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is DLCflexbar-PT-6a, examination is ReachabilityFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r064-tall-162038396900231

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 4.6M

-rw-r--r-- 1 mcc users 11K May 5 16:58 CTLCardinality.txt

-rw-r--r-- 1 mcc users 94K May 5 16:58 CTLCardinality.xml

-rw-r--r-- 1 mcc users 9.9K May 5 16:58 CTLFireability.txt

-rw-r--r-- 1 mcc users 81K May 5 16:58 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.2K May 6 14:48 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K May 6 14:48 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.5K Mar 28 15:57 LTLCardinality.txt

-rw-r--r-- 1 mcc users 28K Mar 28 15:57 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K Mar 28 15:57 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Mar 28 15:57 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.5K Mar 23 04:11 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 18K Mar 23 04:11 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.8K Mar 22 14:05 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K Mar 22 14:04 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Mar 22 09:10 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Mar 22 09:10 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 5 16:51 equiv_col

-rw-r--r-- 1 mcc users 3 May 5 16:51 instance

-rw-r--r-- 1 mcc users 6 May 5 16:51 iscolored

-rw-r--r-- 1 mcc users 4.2M May 5 16:51 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-00

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-01

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-02

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-03

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-04

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-05

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-06

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-07

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-08

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-09

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-10

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-11

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-12

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-13

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-14

FORMULA_NAME DLCflexbar-PT-6a-ReachabilityFireability-15

=== Now, execution of the tool begins

BK_START 1620495406057

Running Version 0

[2021-05-08 17:36:47] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityFireability, -spotpath, /home/mcc/BenchKit/bin//..//ltlfilt, -z3path, /home/mcc/BenchKit/bin//..//z3/bin/z3, -yices2path, /home/mcc/BenchKit/bin//..//yices/bin/yices, -its, -ltsmin, -greatspnpath, /home/mcc/BenchKit/bin//..//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2021-05-08 17:36:47] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2021-05-08 17:36:48] [INFO ] Load time of PNML (sax parser for PT used): 407 ms

[2021-05-08 17:36:48] [INFO ] Transformed 2069 places.

[2021-05-08 17:36:48] [INFO ] Transformed 16077 transitions.

[2021-05-08 17:36:48] [INFO ] Found NUPN structural information;

[2021-05-08 17:36:48] [INFO ] Parsed PT model containing 2069 places and 16077 transitions in 505 ms.

Parsed 16 properties from file /home/mcc/execution/ReachabilityFireability.xml in 13 ms.

Working with output stream class java.io.PrintStream

Ensure Unique test removed 1760 transitions

Reduce redundant transitions removed 1760 transitions.

Incomplete random walk after 10000 steps, including 2 resets, run finished after 500 ms. (steps per millisecond=20 ) properties (out of 16) seen :12

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-13 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-12 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-11 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-10 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-09 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-08 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-05 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-04 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-03 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-02 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-01 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-00 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 256 ms. (steps per millisecond=39 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 253 ms. (steps per millisecond=39 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 251 ms. (steps per millisecond=39 ) properties (out of 4) seen :0

Incomplete Best-First random walk after 10001 steps, including 2 resets, run finished after 257 ms. (steps per millisecond=38 ) properties (out of 4) seen :0

Running SMT prover for 4 properties.

[2021-05-08 17:36:49] [INFO ] Flow matrix only has 970 transitions (discarded 13347 similar events)

// Phase 1: matrix 970 rows 2069 cols

[2021-05-08 17:36:49] [INFO ] Computed 1492 place invariants in 23 ms

[2021-05-08 17:36:50] [INFO ] SMT Verify possible in real domain returnedunsat :0 sat :0 real:4

[2021-05-08 17:36:51] [INFO ] [Nat]Absence check using 1492 positive place invariants in 400 ms returned sat

[2021-05-08 17:36:51] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2021-05-08 17:36:52] [INFO ] [Nat]Absence check using state equation in 829 ms returned unsat :1 sat :3

[2021-05-08 17:36:52] [INFO ] State equation strengthened by 225 read => feed constraints.

[2021-05-08 17:36:52] [INFO ] [Nat]Added 225 Read/Feed constraints in 66 ms returned sat

Attempting to minimize the solution found.

Minimization took 208 ms.

[2021-05-08 17:36:52] [INFO ] SMT Verify possible in nat domain returned unsat :1 sat :3

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-06 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Fused 4 Parikh solutions to 2 different solutions.

Incomplete Parikh walk after 60300 steps, including 967 resets, run finished after 5447 ms. (steps per millisecond=11 ) properties (out of 3) seen :2 could not realise parikh vector

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-14 TRUE TECHNIQUES TOPOLOGICAL PARIKH_WALK

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-07 FALSE TECHNIQUES TOPOLOGICAL PARIKH_WALK

Incomplete Parikh walk after 60100 steps, including 966 resets, run finished after 5204 ms. (steps per millisecond=11 ) properties (out of 1) seen :0 could not realise parikh vector

Support contains 11 out of 2069 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 2069/2069 places, 14317/14317 transitions.

Graph (trivial) has 857 edges and 2069 vertex of which 194 / 2069 are part of one of the 90 SCC in 53 ms

Free SCC test removed 104 places

Drop transitions removed 8592 transitions

Reduce isomorphic transitions removed 8592 transitions.

Graph (complete) has 7334 edges and 1965 vertex of which 418 are kept as prefixes of interest. Removing 1547 places using SCC suffix rule.11 ms

Discarding 1547 places :

Also discarding 4091 output transitions

Drop transitions removed 4091 transitions

Drop transitions removed 457 transitions

Reduce isomorphic transitions removed 457 transitions.

Drop transitions removed 2 transitions

Trivial Post-agglo rules discarded 2 transitions

Performed 2 trivial Post agglomeration. Transition count delta: 2

Iterating post reduction 0 with 459 rules applied. Total rules applied 461 place count 418 transition count 1175

Reduce places removed 2 places and 0 transitions.

Performed 3 Post agglomeration using F-continuation condition.Transition count delta: 3

Iterating post reduction 1 with 5 rules applied. Total rules applied 466 place count 416 transition count 1172

Reduce places removed 3 places and 0 transitions.

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 2 with 4 rules applied. Total rules applied 470 place count 413 transition count 1171

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 1 Pre rules applied. Total rules applied 470 place count 413 transition count 1170

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 3 with 2 rules applied. Total rules applied 472 place count 412 transition count 1170

Discarding 368 places :

Symmetric choice reduction at 3 with 368 rule applications. Total rules 840 place count 44 transition count 104

Iterating global reduction 3 with 368 rules applied. Total rules applied 1208 place count 44 transition count 104

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Iterating post reduction 3 with 1 rules applied. Total rules applied 1209 place count 44 transition count 103

Performed 5 Post agglomeration using F-continuation condition.Transition count delta: 5

Deduced a syphon composed of 5 places in 0 ms

Reduce places removed 5 places and 0 transitions.

Iterating global reduction 4 with 10 rules applied. Total rules applied 1219 place count 39 transition count 98

Drop transitions removed 25 transitions

Ensure Unique test removed 4 transitions

Reduce isomorphic transitions removed 29 transitions.

Graph (complete) has 88 edges and 39 vertex of which 38 are kept as prefixes of interest. Removing 1 places using SCC suffix rule.0 ms

Discarding 1 places :

Also discarding 0 output transitions

Iterating post reduction 4 with 30 rules applied. Total rules applied 1249 place count 38 transition count 69

Discarding 1 places :

Symmetric choice reduction at 5 with 1 rule applications. Total rules 1250 place count 37 transition count 66

Iterating global reduction 5 with 1 rules applied. Total rules applied 1251 place count 37 transition count 66

Drop transitions removed 12 transitions

Redundant transition composition rules discarded 12 transitions

Iterating global reduction 5 with 12 rules applied. Total rules applied 1263 place count 37 transition count 54

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 5 with 2 rules applied. Total rules applied 1265 place count 35 transition count 54

Discarding 3 places :

Symmetric choice reduction at 6 with 3 rule applications. Total rules 1268 place count 32 transition count 46

Iterating global reduction 6 with 3 rules applied. Total rules applied 1271 place count 32 transition count 46

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: -3

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 6 with 2 rules applied. Total rules applied 1273 place count 31 transition count 49

Drop transitions removed 4 transitions

Reduce isomorphic transitions removed 4 transitions.

Iterating post reduction 6 with 4 rules applied. Total rules applied 1277 place count 31 transition count 45

Free-agglomeration rule applied 3 times with reduction of 4 identical transitions.

Iterating global reduction 7 with 3 rules applied. Total rules applied 1280 place count 31 transition count 38

Reduce places removed 3 places and 0 transitions.

Drop transitions removed 4 transitions

Reduce isomorphic transitions removed 4 transitions.

Iterating post reduction 7 with 7 rules applied. Total rules applied 1287 place count 28 transition count 34

Drop transitions removed 4 transitions

Redundant transition composition rules discarded 4 transitions

Iterating global reduction 8 with 4 rules applied. Total rules applied 1291 place count 28 transition count 30

Applied a total of 1291 rules in 204 ms. Remains 28 /2069 variables (removed 2041) and now considering 30/14317 (removed 14287) transitions.

Finished structural reductions, in 1 iterations. Remains : 28/2069 places, 30/14317 transitions.

[2021-05-08 17:37:03] [INFO ] Flatten gal took : 24 ms

[2021-05-08 17:37:03] [INFO ] Flatten gal took : 5 ms

[2021-05-08 17:37:03] [INFO ] Time to serialize gal into /tmp/ReachabilityCardinality15551131694561468328.gal : 4 ms

[2021-05-08 17:37:03] [INFO ] Time to serialize properties into /tmp/ReachabilityCardinality2131705561154519964.prop : 1 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /tmp/ReachabilityCardinality15551131694561468328.gal, -t, CGAL, -reachable-file, /tmp/ReachabilityCardinality2131705561154519964.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202104292328/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /tmp/ReachabilityCardinality15551131694561468328.gal -t CGAL -reachable-file /tmp/ReachabilityCardinality2131705561154519964.prop --nowitness --gen-order FOLLOW

Loading property file /tmp/ReachabilityCardinality2131705561154519964.prop.

SDD proceeding with computation,1 properties remain. new max is 4

SDD size :1 after 3

SDD proceeding with computation,1 properties remain. new max is 8

SDD size :3 after 7

SDD proceeding with computation,1 properties remain. new max is 16

SDD size :7 after 49

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

petri\_inst\_inst,193,0.01117,3800,2,82,8,412,7,0,133,249,0

Total reachable state count : 193

Verifying 1 reachability properties.

Invariant property DLCflexbar-PT-6a-ReachabilityFireability-15 does not hold.

FORMULA DLCflexbar-PT-6a-ReachabilityFireability-15 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL COLLATERAL_PROCESSING

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

DLCflexbar-PT-6a-ReachabilityFireability-15,2,0.01208,4156,2,32,8,412,7,0,148,249,0

All properties solved without resorting to model-checking.

BK_STOP 1620495424881

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/bin//../

+ BINDIR=/home/mcc/BenchKit/bin//../

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityFireability = StateSpace ]]

+ /home/mcc/BenchKit/bin//..//runeclipse.sh /home/mcc/execution ReachabilityFireability -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

++ cut -d . -f 9

++ ls /home/mcc/BenchKit/bin//..//itstools/plugins/fr.lip6.move.gal.application.pnmcc_1.0.0.202104292328.jar

+ VERSION=0

+ echo 'Running Version 0'

+ /home/mcc/BenchKit/bin//..//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityFireability -spotpath /home/mcc/BenchKit/bin//..//ltlfilt -z3path /home/mcc/BenchKit/bin//..//z3/bin/z3 -yices2path /home/mcc/BenchKit/bin//..//yices/bin/yices -its -ltsmin -greatspnpath /home/mcc/BenchKit/bin//..//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCflexbar-PT-6a"

export BK_EXAMINATION="ReachabilityFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

export BK_BIN_PATH="/home/mcc/BenchKit/bin/"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is DLCflexbar-PT-6a, examination is ReachabilityFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r064-tall-162038396900231"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DLCflexbar-PT-6a.tgz

mv DLCflexbar-PT-6a execution

cd execution

if [ "ReachabilityFireability" = "ReachabilityDeadlock" ] || [ "ReachabilityFireability" = "UpperBounds" ] || [ "ReachabilityFireability" = "QuasiLiveness" ] || [ "ReachabilityFireability" = "StableMarking" ] || [ "ReachabilityFireability" = "Liveness" ] || [ "ReachabilityFireability" = "OneSafe" ] || [ "ReachabilityFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityFireability" = "ReachabilityDeadlock" ] || [ "ReachabilityFireability" = "QuasiLiveness" ] || [ "ReachabilityFireability" = "StableMarking" ] || [ "ReachabilityFireability" = "Liveness" ] || [ "ReachabilityFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;