About the Execution of ITS-Tools for ShieldIIPt-PT-010B

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15741.180 | 1800000.00 | 1893099.00 | 2359.20 | [undef] | Time out reached |

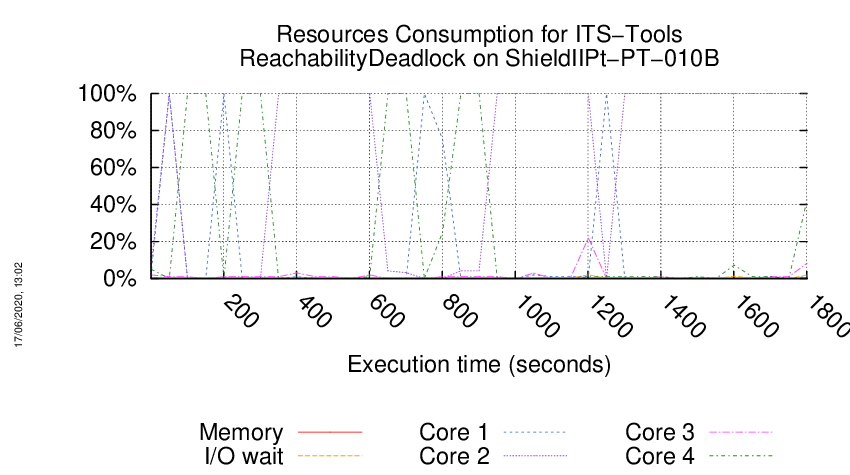

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2020-input.r217-tajo-159033489600191.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2020-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

.......................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is ShieldIIPt-PT-010B, examination is ReachabilityDeadlock

Time confinement is 1800 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r217-tajo-159033489600191

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 336K

-rw-r--r-- 1 mcc users 3.5K May 14 01:01 CTLCardinality.txt

-rw-r--r-- 1 mcc users 20K May 14 01:01 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.6K May 13 18:18 CTLFireability.txt

-rw-r--r-- 1 mcc users 18K May 13 18:18 CTLFireability.xml

-rw-r--r-- 1 mcc users 3.5K May 14 10:02 LTLCardinality.txt

-rw-r--r-- 1 mcc users 26K May 14 10:02 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9K May 14 10:02 LTLFireability.txt

-rw-r--r-- 1 mcc users 16K May 14 10:02 LTLFireability.xml

-rw-r--r-- 1 mcc users 1 May 12 20:42 NewModel

-rw-r--r-- 1 mcc users 3.3K May 13 13:28 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 16K May 13 13:28 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.9K May 13 08:03 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 18K May 13 08:03 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 13 16:53 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 13 16:53 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 12 20:42 equiv_col

-rw-r--r-- 1 mcc users 5 May 12 20:42 instance

-rw-r--r-- 1 mcc users 6 May 12 20:42 iscolored

-rw-r--r-- 1 mcc users 167K May 12 20:42 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

FORMULA_NAME ReachabilityDeadlock

=== Now, execution of the tool begins

BK_START 1590827610847

[2020-05-30 08:33:32] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityDeadlock, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 1800]

[2020-05-30 08:33:32] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-05-30 08:33:33] [INFO ] Load time of PNML (sax parser for PT used): 81 ms

[2020-05-30 08:33:33] [INFO ] Transformed 703 places.

[2020-05-30 08:33:33] [INFO ] Transformed 653 transitions.

[2020-05-30 08:33:33] [INFO ] Found NUPN structural information;

[2020-05-30 08:33:33] [INFO ] Parsed PT model containing 703 places and 653 transitions in 134 ms.

Parsed 1 properties from file /home/mcc/execution/ReachabilityDeadlock.xml in 20 ms.

Working with output stream class java.io.PrintStream

Built sparse matrix representations for Structural reductions in 4 ms.21355KB memory used

Starting structural reductions, iteration 0 : 703/703 places, 653/653 transitions.

Performed 172 Post agglomeration using F-continuation condition.Transition count delta: 172

Iterating post reduction 0 with 172 rules applied. Total rules applied 172 place count 703 transition count 481

Reduce places removed 172 places and 0 transitions.

Ensure Unique test removed 1 transitions

Reduce isomorphic transitions removed 1 transitions.

Performed 1 Post agglomeration using F-continuation condition.Transition count delta: 1

Iterating post reduction 1 with 174 rules applied. Total rules applied 346 place count 531 transition count 479

Reduce places removed 1 places and 0 transitions.

Iterating post reduction 2 with 1 rules applied. Total rules applied 347 place count 530 transition count 479

Performed 41 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 41 Pre rules applied. Total rules applied 347 place count 530 transition count 438

Deduced a syphon composed of 41 places in 2 ms

Reduce places removed 41 places and 0 transitions.

Iterating global reduction 3 with 82 rules applied. Total rules applied 429 place count 489 transition count 438

Symmetric choice reduction at 3 with 70 rule applications. Total rules 499 place count 489 transition count 438

Deduced a syphon composed of 70 places in 2 ms

Reduce places removed 70 places and 70 transitions.

Iterating global reduction 3 with 140 rules applied. Total rules applied 639 place count 419 transition count 368

Performed 30 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 3 with 30 Pre rules applied. Total rules applied 639 place count 419 transition count 338

Deduced a syphon composed of 30 places in 0 ms

Reduce places removed 30 places and 0 transitions.

Iterating global reduction 3 with 60 rules applied. Total rules applied 699 place count 389 transition count 338

Performed 169 Post agglomeration using F-continuation condition.Transition count delta: 169

Deduced a syphon composed of 169 places in 0 ms

Reduce places removed 169 places and 0 transitions.

Iterating global reduction 3 with 338 rules applied. Total rules applied 1037 place count 220 transition count 169

Performed 29 Post agglomeration using F-continuation condition.Transition count delta: -19

Deduced a syphon composed of 29 places in 1 ms

Reduce places removed 29 places and 0 transitions.

Iterating global reduction 3 with 58 rules applied. Total rules applied 1095 place count 191 transition count 188

Reduce places removed 1 places and 1 transitions.

Iterating global reduction 3 with 1 rules applied. Total rules applied 1096 place count 190 transition count 187

Reduce places removed 2 places and 0 transitions.

Iterating post reduction 3 with 2 rules applied. Total rules applied 1098 place count 188 transition count 187

Performed 1 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 4 with 1 Pre rules applied. Total rules applied 1098 place count 188 transition count 186

Deduced a syphon composed of 1 places in 0 ms

Reduce places removed 1 places and 0 transitions.

Iterating global reduction 4 with 2 rules applied. Total rules applied 1100 place count 187 transition count 186

Applied a total of 1100 rules in 190 ms. Remains 187 /703 variables (removed 516) and now considering 186/653 (removed 467) transitions.

Finished structural reductions, in 1 iterations. Remains : 187/703 places, 186/653 transitions.

Random walk for 1250000 steps, including 0 resets, run took 2855 ms (no deadlock found). (steps per millisecond=437 )

Random directed walk for 1250004 steps, including 0 resets, run took 2157 ms (no deadlock found). (steps per millisecond=579 )

// Phase 1: matrix 186 rows 187 cols

[2020-05-30 08:33:38] [INFO ] Computed 89 place invariants in 6 ms

[2020-05-30 08:33:38] [INFO ] [Real]Absence check using 89 positive place invariants in 71 ms returned sat

[2020-05-30 08:33:38] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-30 08:33:38] [INFO ] [Real]Absence check using state equation in 199 ms returned sat

[2020-05-30 08:33:38] [INFO ] Solution in real domain found non-integer solution.

[2020-05-30 08:33:38] [INFO ] [Nat]Absence check using 89 positive place invariants in 25 ms returned sat

[2020-05-30 08:33:38] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-30 08:33:39] [INFO ] [Nat]Absence check using state equation in 133 ms returned sat

[2020-05-30 08:33:39] [INFO ] Computed and/alt/rep : 182/278/182 causal constraints in 20 ms.

[2020-05-30 08:33:39] [INFO ] Added : 156 causal constraints over 32 iterations in 428 ms. Result :sat

Attempting to minimize the solution found.

Minimization took 11 ms.

Parikh directed walk for 56500 steps, including 137 resets, run took 198 ms. (steps per millisecond=285 )

Random directed walk for 500001 steps, including 0 resets, run took 927 ms (no deadlock found). (steps per millisecond=539 )

Random walk for 500000 steps, including 0 resets, run took 1222 ms (no deadlock found). (steps per millisecond=409 )

Random directed walk for 500003 steps, including 0 resets, run took 993 ms (no deadlock found). (steps per millisecond=503 )

Random walk for 500000 steps, including 0 resets, run took 1076 ms (no deadlock found). (steps per millisecond=464 )

[2020-05-30 08:33:44] [INFO ] Flatten gal took : 100 ms

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

[2020-05-30 08:33:44] [INFO ] Applying decomposition

[2020-05-30 08:33:44] [INFO ] Flatten gal took : 47 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/convert-linux64, -i, /tmp/graph3079662102279596367.txt, -o, /tmp/graph3079662102279596367.bin, -w, /tmp/graph3079662102279596367.weights], workingDir=null]

[2020-05-30 08:33:44] [INFO ] Input system was already deterministic with 653 transitions.

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/louvain-linux64, /tmp/graph3079662102279596367.bin, -l, -1, -v, -w, /tmp/graph3079662102279596367.weights, -q, 0, -e, 0.001], workingDir=null]

[2020-05-30 08:33:44] [INFO ] Decomposing Gal with order

[2020-05-30 08:33:44] [INFO ] Rewriting arrays to variables to allow decomposition.

[2020-05-30 08:33:45] [INFO ] Removed a total of 60 redundant transitions.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 653 rows 703 cols

[2020-05-30 08:33:45] [INFO ] Computed 91 place invariants in 11 ms

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p225 + p226 + p238 + p239 + p240 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p658 + p659 + p660 + p661 + p662 + p663 + p664 + p665 + p666 + p667 + p668 + p669 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p156 + p157 + p169 + p170 + p171 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p225 + p226 + p227 + p231 + p232 + p233 + p236 + p237 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p501 + p502 + p503 + p504 + p505 + p506 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p71 + p72 + p73 + p74 + p75 + p76 + p77 + p78 + p79 + p80 + p81 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p156 + p157 + p158 + p162 + p163 + p164 + p165 + p166 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p59 + p60 + p61 + p62 + p63 + p64 + p65 + p66 + p67 + p68 + p69 + p70 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p294 + p295 + p307 + p308 + p309 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p501 + p502 + p514 + p515 + p516 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p485 + p486 + p487 + p488 + p489 + p490 + p491 + p492 + p493 + p494 + p495 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p294 + p295 + p296 + p300 + p301 + p302 + p305 + p306 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p18 + p19 + p20 + p24 + p25 + p26 + p27 + p28 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p209 + p210 + p211 + p212 + p213 + p214 + p215 + p216 + p217 + p218 + p219 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p225 + p241 + p242 + p243 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p156 + p172 + p173 + p174 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p106 + p107 + p108 + p109 + p110 + p111 + p112 + p113 + p114 + p115 + p116 + p117 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p278 + p279 + p280 + p281 + p282 + p283 + p284 + p285 + p286 + p287 + p288 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p363 + p364 + p365 + p369 + p370 + p371 + p374 + p375 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p87 + p103 + p104 + p105 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p175 + p176 + p177 + p178 + p179 + p180 + p181 + p182 + p183 + p184 + p185 + p186 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p18 + p19 + p31 + p32 + p33 = 1

inv : p0 + p1 + p2 + p496 + p497 + p554 + p555 + p556 + p557 + p558 + p559 + p560 + p561 + p562 + p563 + p564 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p432 + p433 + p434 + p438 + p439 + p440 + p443 + p444 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p87 + p88 + p100 + p101 + p102 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p394 + p395 + p396 + p397 + p398 + p399 + p400 + p401 + p402 + p403 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p156 + p157 + p158 + p162 + p163 + p164 + p167 + p168 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p294 + p295 + p296 + p300 + p301 + p302 + p303 + p304 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p382 + p383 + p384 + p385 + p386 + p387 + p388 + p389 + p390 + p391 + p392 + p393 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p128 + p129 + p130 + p131 + p132 + p133 + p134 + p135 + p136 + p137 + p138 + p139 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p570 + p571 + p572 + p576 + p577 + p578 + p579 + p580 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p432 + p433 + p434 + p438 + p439 + p440 + p441 + p442 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p294 + p310 + p311 + p312 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p363 + p364 + p365 + p369 + p370 + p371 + p372 + p373 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p187 + p188 + p189 + p190 + p191 + p192 + p193 + p194 + p195 + p196 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p294 + p295 + p296 + p297 + p298 + p299 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p601 + p602 + p603 + p604 + p605 + p606 + p607 + p608 + p609 + p610 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p520 + p521 + p522 + p523 + p524 + p525 + p526 + p527 + p528 + p529 + p530 + p531 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p432 + p448 + p449 + p450 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p639 + p640 + p641 + p642 + p643 + p644 = 1

inv : p0 + p634 + p635 + p636 + p680 + p681 + p682 + p683 + p684 + p685 + p686 + p687 + p688 + p689 + p690 + p691 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p18 + p19 + p20 + p24 + p25 + p26 + p29 + p30 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p570 + p571 + p572 + p573 + p574 + p575 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p501 + p502 + p503 + p507 + p508 + p509 + p512 + p513 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p266 + p267 + p268 + p269 + p270 + p271 + p272 + p273 + p274 + p275 + p276 + p277 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p463 + p464 + p465 + p466 + p467 + p468 + p469 + p470 + p471 + p472 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p225 + p226 + p227 + p228 + p229 + p230 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p244 + p245 + p246 + p247 + p248 + p249 + p250 + p251 + p252 + p253 + p254 + p255 = 1

inv : p0 + p1 + p565 + p566 + p567 + p611 + p612 + p613 + p614 + p615 + p616 + p617 + p618 + p619 + p620 + p621 + p622 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p532 + p533 + p534 + p535 + p536 + p537 + p538 + p539 + p540 + p541 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p639 + p655 + p656 + p657 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p154 + p155 + p156 + p157 + p158 + p159 + p160 + p161 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p639 + p640 + p652 + p653 + p654 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p639 + p640 + p641 + p645 + p646 + p647 + p650 + p651 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p325 + p326 + p327 + p328 + p329 + p330 + p331 + p332 + p333 + p334 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p363 + p379 + p380 + p381 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p501 + p502 + p503 + p507 + p508 + p509 + p510 + p511 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p363 + p364 + p376 + p377 + p378 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p570 + p571 + p583 + p584 + p585 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p18 + p34 + p35 + p36 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p451 + p452 + p453 + p454 + p455 + p456 + p457 + p458 + p459 + p460 + p461 + p462 = 1

inv : p0 + p634 + p635 + p692 + p693 + p694 + p695 + p696 + p697 + p698 + p699 + p700 + p701 + p702 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p335 + p336 + p337 + p338 + p339 + p340 + p341 + p342 + p343 + p344 + p345 + p346 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p291 + p292 + p293 + p313 + p314 + p315 + p316 + p317 + p318 + p319 + p320 + p321 + p322 + p323 + p324 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p404 + p405 + p406 + p407 + p408 + p409 + p410 + p411 + p412 + p413 + p414 + p415 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p140 + p141 + p142 + p143 + p144 + p145 + p146 + p147 + p148 + p149 + p150 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p432 + p433 + p434 + p435 + p436 + p437 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p570 + p571 + p572 + p576 + p577 + p578 + p581 + p582 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p430 + p431 + p432 + p433 + p445 + p446 + p447 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p87 + p88 + p89 + p90 + p91 + p92 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p118 + p119 + p120 + p121 + p122 + p123 + p124 + p125 + p126 + p127 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p570 + p586 + p587 + p588 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p542 + p543 + p544 + p545 + p546 + p547 + p548 + p549 + p550 + p551 + p552 + p553 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p18 + p19 + p20 + p21 + p22 + p23 = 1

inv : p0 + p1 + p2 + p3 + p427 + p428 + p429 + p473 + p474 + p475 + p476 + p477 + p478 + p479 + p480 + p481 + p482 + p483 + p484 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p87 + p88 + p89 + p93 + p94 + p95 + p98 + p99 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p360 + p361 + p362 + p363 + p364 + p365 + p366 + p367 + p368 = 1

inv : p0 + p1 + p565 + p566 + p567 + p568 + p569 + p589 + p590 + p591 + p592 + p593 + p594 + p595 + p596 + p597 + p598 + p599 + p600 = 1

inv : p0 + p634 + p635 + p636 + p637 + p670 + p671 + p672 + p673 + p674 + p675 + p676 + p677 + p678 + p679 = 1

inv : p0 + p1 + p2 + p3 + p4 + p358 + p359 + p416 + p417 + p418 + p419 + p420 + p421 + p422 + p423 + p424 + p425 + p426 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p17 + p37 + p38 + p39 + p40 + p41 + p42 + p43 + p44 + p45 + p46 + p47 + p48 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p289 + p290 + p347 + p348 + p349 + p350 + p351 + p352 + p353 + p354 + p355 + p356 + p357 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p10 + p11 + p12 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p224 + p225 + p226 + p227 + p231 + p232 + p233 + p234 + p235 = 1

inv : p0 + p1 + p565 + p566 + p623 + p624 + p625 + p626 + p627 + p628 + p629 + p630 + p631 + p632 + p633 = 1

inv : p0 + p1 + p2 + p496 + p497 + p498 + p499 + p500 + p501 + p517 + p518 + p519 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p151 + p152 + p153 + p197 + p198 + p199 + p200 + p201 + p202 + p203 + p204 + p205 + p206 + p207 + p208 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p82 + p83 + p84 + p85 + p86 + p87 + p88 + p89 + p93 + p94 + p95 + p96 + p97 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p13 + p14 + p15 + p16 + p49 + p50 + p51 + p52 + p53 + p54 + p55 + p56 + p57 + p58 = 1

inv : p0 + p634 + p635 + p636 + p637 + p638 + p639 + p640 + p641 + p645 + p646 + p647 + p648 + p649 = 1

inv : p0 + p1 + p2 + p3 + p4 + p5 + p6 + p220 + p221 + p222 + p223 + p256 + p257 + p258 + p259 + p260 + p261 + p262 + p263 + p264 + p265 = 1

Total of 91 invariants.

[2020-05-30 08:33:45] [INFO ] Computed 91 place invariants in 14 ms

[2020-05-30 08:33:45] [INFO ] Flatten gal took : 237 ms

[2020-05-30 08:33:45] [INFO ] Fuse similar labels procedure discarded/fused a total of 0 labels/synchronizations in 12 ms.

[2020-05-30 08:33:45] [INFO ] Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 17 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK

No direction supplied, using forward translation only.

built 43 ordering constraints for composite.

built 23 ordering constraints for composite.

built 27 ordering constraints for composite.

built 10 ordering constraints for composite.

built 16 ordering constraints for composite.

built 8 ordering constraints for composite.

built 7 ordering constraints for composite.

built 6 ordering constraints for composite.

built 19 ordering constraints for composite.

built 7 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 29 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 12 ordering constraints for composite.

built 6 ordering constraints for composite.

built 22 ordering constraints for composite.

built 5 ordering constraints for composite.

built 12 ordering constraints for composite.

built 7 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 15 ordering constraints for composite.

built 27 ordering constraints for composite.

built 10 ordering constraints for composite.

built 12 ordering constraints for composite.

built 18 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 12 ordering constraints for composite.

built 8 ordering constraints for composite.

built 7 ordering constraints for composite.

built 6 ordering constraints for composite.

built 10 ordering constraints for composite.

built 27 ordering constraints for composite.

built 10 ordering constraints for composite.

built 17 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 8 ordering constraints for composite.

built 7 ordering constraints for composite.

built 6 ordering constraints for composite.

built 18 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 33 ordering constraints for composite.

built 10 ordering constraints for composite.

built 10 ordering constraints for composite.

built 28 ordering constraints for composite.

built 10 ordering constraints for composite.

built 9 ordering constraints for composite.

[2020-05-30 08:33:45] [INFO ] Proved 703 variables to be positive in 842 ms

[2020-05-30 08:33:45] [INFO ] Computing symmetric may disable matrix : 653 transitions.

[2020-05-30 08:33:45] [INFO ] Computation of disable matrix completed :0/653 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-30 08:33:45] [INFO ] Computation of Complete disable matrix. took 42 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-30 08:33:45] [INFO ] Computing symmetric may enable matrix : 653 transitions.

[2020-05-30 08:33:46] [INFO ] Computation of Complete enable matrix. took 36 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-30 08:33:46] [INFO ] Computing symmetric co enabling matrix : 653 transitions.

[2020-05-30 08:33:49] [INFO ] Computation of co-enabling matrix(120/653) took 3405 ms. Total solver calls (SAT/UNSAT): 3121(8/3113)

[2020-05-30 08:33:52] [INFO ] Computation of co-enabling matrix(155/653) took 6473 ms. Total solver calls (SAT/UNSAT): 3585(11/3574)

[2020-05-30 08:33:55] [INFO ] Computation of co-enabling matrix(219/653) took 9484 ms. Total solver calls (SAT/UNSAT): 4717(16/4701)

[2020-05-30 08:33:58] [INFO ] Computation of co-enabling matrix(255/653) took 12843 ms. Total solver calls (SAT/UNSAT): 5540(18/5522)

[2020-05-30 08:34:01] [INFO ] Computation of co-enabling matrix(276/653) took 15883 ms. Total solver calls (SAT/UNSAT): 5711(20/5691)

[2020-05-30 08:34:04] [INFO ] Computation of co-enabling matrix(287/653) took 18902 ms. Total solver calls (SAT/UNSAT): 6209(20/6189)

[2020-05-30 08:34:07] [INFO ] Computation of co-enabling matrix(363/653) took 21941 ms. Total solver calls (SAT/UNSAT): 7280(26/7254)

[2020-05-30 08:34:10] [INFO ] Computation of co-enabling matrix(434/653) took 24945 ms. Total solver calls (SAT/UNSAT): 8246(31/8215)

[2020-05-30 08:34:13] [INFO ] Computation of co-enabling matrix(504/653) took 27960 ms. Total solver calls (SAT/UNSAT): 9068(36/9032)

[2020-05-30 08:34:16] [INFO ] Computation of co-enabling matrix(613/653) took 30970 ms. Total solver calls (SAT/UNSAT): 9840(54/9786)

[2020-05-30 08:34:18] [INFO ] Computation of Finished co-enabling matrix. took 32042 ms. Total solver calls (SAT/UNSAT): 9888(70/9818)

[2020-05-30 08:34:18] [INFO ] Computing Do-Not-Accords matrix : 653 transitions.

[2020-05-30 08:34:18] [INFO ] Computation of Completed DNA matrix. took 81 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-30 08:34:18] [INFO ] Built C files in 33832ms conformant to PINS in folder :/home/mcc/execution

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/home/mcc/execution]

Compilation finished in 8687 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 81 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc: error while loading shared libraries: libltdl.so.7: cannot open shared object file: No such file or directory

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

127

java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

127

at fr.lip6.move.gal.application.LTSminRunner.checkProperty(LTSminRunner.java:170)

at fr.lip6.move.gal.application.LTSminRunner.access$10(LTSminRunner.java:124)

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:93)

at java.base/java.lang.Thread.run(Thread.java:834)

Detected timeout of ITS tools.

[2020-05-30 08:43:48] [INFO ] Applying decomposition

[2020-05-30 08:43:48] [INFO ] Flatten gal took : 25 ms

[2020-05-30 08:43:48] [INFO ] Decomposing Gal with order

[2020-05-30 08:43:48] [INFO ] Rewriting arrays to variables to allow decomposition.

[2020-05-30 08:43:48] [INFO ] Flatten gal took : 66 ms

[2020-05-30 08:43:48] [INFO ] Fuse similar labels procedure discarded/fused a total of 0 labels/synchronizations in 4 ms.

[2020-05-30 08:43:48] [INFO ] Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 30 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK

No direction supplied, using forward translation only.

built 2 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 12 ordering constraints for composite.

built 11 ordering constraints for composite.

built 13 ordering constraints for composite.

built 11 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 10 ordering constraints for composite.

built 9 ordering constraints for composite.

built 11 ordering constraints for composite.

built 10 ordering constraints for composite.

built 9 ordering constraints for composite.

built 7 ordering constraints for composite.

built 5 ordering constraints for composite.

Detected timeout of ITS tools.

[2020-05-30 08:53:53] [INFO ] Flatten gal took : 393 ms

[2020-05-30 08:53:54] [INFO ] Input system was already deterministic with 653 transitions.

[2020-05-30 08:53:54] [INFO ] Transformed 703 places.

[2020-05-30 08:53:54] [INFO ] Transformed 653 transitions.

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/pinvar, /home/mcc/execution/gspn], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/RGMEDD2, /home/mcc/execution/gspn, -META, -varord-only], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Using order generated by GreatSPN with heuristic : META

[2020-05-30 08:53:54] [INFO ] Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 10 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK, --load-order, /home/mcc/execution/model.ord, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK --load-order /home/mcc/execution/model.ord --gen-order FOLLOW

Successfully loaded order from file /home/mcc/execution/model.ord

No direction supplied, using forward translation only.

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityDeadlock = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityDeadlock -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 1800

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityDeadlock -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 1800 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ShieldIIPt-PT-010B"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="1800"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is ShieldIIPt-PT-010B, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r217-tajo-159033489600191"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ShieldIIPt-PT-010B.tgz

mv ShieldIIPt-PT-010B execution

cd execution

if [ "ReachabilityDeadlock" = "ReachabilityDeadlock" ] || [ "ReachabilityDeadlock" = "UpperBounds" ] || [ "ReachabilityDeadlock" = "QuasiLiveness" ] || [ "ReachabilityDeadlock" = "StableMarking" ] || [ "ReachabilityDeadlock" = "Liveness" ] || [ "ReachabilityDeadlock" = "OneSafe" ] || [ "ReachabilityDeadlock" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityDeadlock" = "ReachabilityDeadlock" ] || [ "ReachabilityDeadlock" = "QuasiLiveness" ] || [ "ReachabilityDeadlock" = "StableMarking" ] || [ "ReachabilityDeadlock" = "Liveness" ] || [ "ReachabilityDeadlock" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityDeadlock"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;