About the Execution of ITS-LoLa for DLCround-PT-05b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15743.260 | 3600000.00 | 3650796.00 | 1086.90 | FTF?T?TTF?TFFTTF | normal |

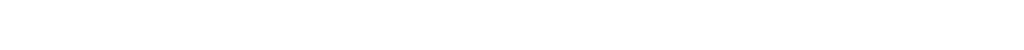

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2020-input.r180-ebro-158987900300492.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2020-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

..........................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itslola

Input is DLCround-PT-05b, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r180-ebro-158987900300492

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 852K

-rw-r--r-- 1 mcc users 3.2K Mar 30 18:50 CTLCardinality.txt

-rw-r--r-- 1 mcc users 17K Mar 30 18:50 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.4K Mar 29 08:48 CTLFireability.txt

-rw-r--r-- 1 mcc users 15K Mar 29 08:48 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 24 05:37 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K Mar 24 05:37 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.4K Apr 8 14:50 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Apr 28 14:00 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.0K Apr 8 14:50 LTLFireability.txt

-rw-r--r-- 1 mcc users 17K Apr 28 14:00 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.9K Mar 28 04:41 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 21K Mar 28 04:41 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.2K Mar 26 23:09 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 11K Mar 26 23:09 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Mar 28 14:49 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Mar 28 14:49 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 24 05:37 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 24 05:37 instance

-rw-r--r-- 1 mcc users 6 Mar 24 05:37 iscolored

-rw-r--r-- 1 mcc users 674K Mar 24 05:37 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-05b-CTLFireability-00

FORMULA_NAME DLCround-PT-05b-CTLFireability-01

FORMULA_NAME DLCround-PT-05b-CTLFireability-02

FORMULA_NAME DLCround-PT-05b-CTLFireability-03

FORMULA_NAME DLCround-PT-05b-CTLFireability-04

FORMULA_NAME DLCround-PT-05b-CTLFireability-05

FORMULA_NAME DLCround-PT-05b-CTLFireability-06

FORMULA_NAME DLCround-PT-05b-CTLFireability-07

FORMULA_NAME DLCround-PT-05b-CTLFireability-08

FORMULA_NAME DLCround-PT-05b-CTLFireability-09

FORMULA_NAME DLCround-PT-05b-CTLFireability-10

FORMULA_NAME DLCround-PT-05b-CTLFireability-11

FORMULA_NAME DLCround-PT-05b-CTLFireability-12

FORMULA_NAME DLCround-PT-05b-CTLFireability-13

FORMULA_NAME DLCround-PT-05b-CTLFireability-14

FORMULA_NAME DLCround-PT-05b-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1591237604012

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

[2020-06-04 02:26:47] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -timeout, 3600, -rebuildPNML]

[2020-06-04 02:26:47] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-06-04 02:26:47] [INFO ] Load time of PNML (sax parser for PT used): 357 ms

[2020-06-04 02:26:47] [INFO ] Transformed 1999 places.

[2020-06-04 02:26:47] [INFO ] Transformed 2887 transitions.

[2020-06-04 02:26:47] [INFO ] Found NUPN structural information;

[2020-06-04 02:26:48] [INFO ] Parsed PT model containing 1999 places and 2887 transitions in 575 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 185 ms.

Incomplete random walk after 100000 steps, including 2 resets, run finished after 1002 ms. (steps per millisecond=99 ) properties seen :[0, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 0, 0, 1, 0, 1, 1, 1, 1, 0, 1, 1, 1, 0, 1, 1, 1, 1, 1]

// Phase 1: matrix 2887 rows 1999 cols

[2020-06-04 02:26:49] [INFO ] Computed 88 place invariants in 111 ms

[2020-06-04 02:26:51] [INFO ] [Real]Absence check using 88 positive place invariants in 398 ms returned sat

[2020-06-04 02:26:51] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:27:09] [INFO ] SMT solver returned unknown. Retrying;

[2020-06-04 02:27:09] [INFO ] [Real]Absence check using state equation in 18314 ms returned (error "Failed to check-sat")

[2020-06-04 02:27:10] [INFO ] [Real]Absence check using 88 positive place invariants in 301 ms returned sat

[2020-06-04 02:27:10] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:27:29] [INFO ] SMT solver returned unknown. Retrying;

[2020-06-04 02:27:29] [INFO ] [Real]Absence check using state equation in 19112 ms returned (error "Failed to check-sat")

[2020-06-04 02:27:30] [INFO ] [Real]Absence check using 88 positive place invariants in 298 ms returned sat

[2020-06-04 02:27:30] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:27:49] [INFO ] SMT solver returned unknown. Retrying;

[2020-06-04 02:27:49] [INFO ] [Real]Absence check using state equation in 19308 ms returned (error "Failed to check-sat")

[2020-06-04 02:27:50] [INFO ] [Real]Absence check using 88 positive place invariants in 270 ms returned sat

[2020-06-04 02:27:50] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:28:09] [INFO ] [Real]Absence check using state equation in 19013 ms returned sat

[2020-06-04 02:28:12] [INFO ] Deduced a trap composed of 12 places in 3148 ms

[2020-06-04 02:28:12] [WARNING] SMT solver failed with error :java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Failed to assert expression: java.io.IOException: Stream closed (> (+ s0 s1142 s1989 s1990 s1991 s1992 s1993 s1994 s1995 s1996 s1997 s1998) 0)") while checking expression at index 3

[2020-06-04 02:28:13] [INFO ] [Real]Absence check using 88 positive place invariants in 294 ms returned sat

[2020-06-04 02:28:13] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:28:32] [INFO ] SMT solver returned unknown. Retrying;

[2020-06-04 02:28:32] [INFO ] [Real]Absence check using state equation in 19318 ms returned unknown

[2020-06-04 02:28:33] [INFO ] [Real]Absence check using 88 positive place invariants in 274 ms returned sat

[2020-06-04 02:28:33] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-04 02:28:51] [INFO ] [Real]Absence check using state equation in 18529 ms returned sat

[2020-06-04 02:28:53] [INFO ] Deduced a trap composed of 138 places in 1611 ms

[2020-06-04 02:28:53] [WARNING] SMT solver failed with error :java.lang.RuntimeException: SMT solver raised an error when submitting script. Raised (error "Failed to assert expression: java.io.IOException: Stream closed (> (+ s0 s663 s664 s665 s666 s667 s668 s669 s670 s671 s672 s673 s674 s675 s676 s677 s678 s679 s680 s681 s682 s683 s684 s685 s686 s687 s688 s689 s690 s691 s692 s693 s694 s695 s696 s697 s698 s699 s700 s701 s702 s703 s704 s705 s706 s707 s708 s709 s710 s711 s712 s713 s714 s715 s716 s717 s718 s719 s720 s721 s722 s723 s724 s725 s726 s727 s728 s729 s730 s731 s732 s733 s734 s735 s736 s737 s738 s739 s740 s741 s742 s743 s744 s745 s746 s747 s748 s749 s750 s751 s752 s753 s754 s755 s756 s757 s758 s759 s760 s761 s762 s763 s764 s765 s766 s767 s768 s769 s770 s771 s772 s773 s774 s775 s776 s777 s778 s1142 s1143 s1144 s1145 s1146 s1147 s1148 s1149 s1150 s1151 s1152 s1153 s1154 s1869 s1872 s1873 s1874 s1875 s1876 s1877 s1878) 0)") while checking expression at index 5

[2020-06-04 02:28:54] [INFO ] Flatten gal took : 437 ms

[2020-06-04 02:28:54] [INFO ] Flatten gal took : 234 ms

[2020-06-04 02:28:54] [INFO ] Export to MCC properties in file /home/mcc/execution/CTLFireability.sr.xml took 9 ms.

[2020-06-04 02:28:55] [INFO ] Export to PNML in file /home/mcc/execution/model.sr.pnml took 49 ms.

info: Time: 3600 - MCC

vrfy: Checking CTLFireability @ DLCround-PT-05b @ 3570 seconds

FORMULA DLCround-PT-05b-CTLFireability-06 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-08 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-11 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-12 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-14 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-01 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-07 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-00 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-13 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-10 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-02 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA DLCround-PT-05b-CTLFireability-04 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

TIME LIMIT: Killed by timeout after 3600 seconds

MemTotal: 16427456 kB

MemFree: 10164856 kB

After kill :

MemTotal: 16427456 kB

MemFree: 10218212 kB

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-05b"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itslola"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itslola"

echo " Input is DLCround-PT-05b, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r180-ebro-158987900300492"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-05b.tgz

mv DLCround-PT-05b execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;