About the Execution of ITS-LoLa for Railroad-PT-020

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15789.160 | 3600000.00 | 3641746.00 | 25870.50 | ?FFFF?FFFFF?F?FT | normal |

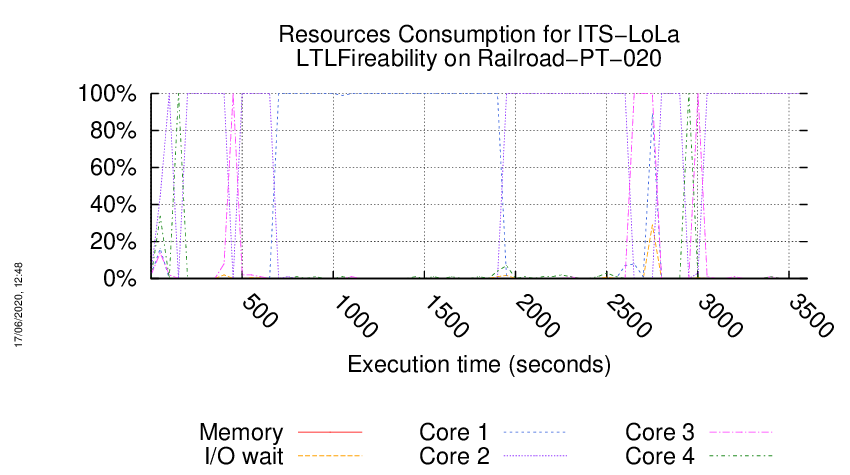

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2020-input.r172-smll-158987827700306.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2020-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

..............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itslola

Input is Railroad-PT-020, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r172-smll-158987827700306

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 424K

-rw-r--r-- 1 mcc users 3.4K Apr 12 08:38 CTLCardinality.txt

-rw-r--r-- 1 mcc users 18K Apr 12 08:38 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.6K Apr 11 09:47 CTLFireability.txt

-rw-r--r-- 1 mcc users 16K Apr 11 09:47 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 24 05:38 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K Mar 24 05:38 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.7K Apr 14 12:47 LTLCardinality.txt

-rw-r--r-- 1 mcc users 24K Apr 28 14:02 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.3K Apr 14 12:47 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K Apr 28 14:02 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.9K Apr 10 14:53 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 19K Apr 10 14:53 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.8K Apr 9 21:29 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 15K Apr 9 21:29 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K Apr 10 22:28 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K Apr 10 22:28 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 24 05:38 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 24 05:38 instance

-rw-r--r-- 1 mcc users 6 Mar 24 05:38 iscolored

-rw-r--r-- 1 mcc users 249K Mar 24 05:38 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME Railroad-PT-020-00

FORMULA_NAME Railroad-PT-020-01

FORMULA_NAME Railroad-PT-020-02

FORMULA_NAME Railroad-PT-020-03

FORMULA_NAME Railroad-PT-020-04

FORMULA_NAME Railroad-PT-020-05

FORMULA_NAME Railroad-PT-020-06

FORMULA_NAME Railroad-PT-020-07

FORMULA_NAME Railroad-PT-020-08

FORMULA_NAME Railroad-PT-020-09

FORMULA_NAME Railroad-PT-020-10

FORMULA_NAME Railroad-PT-020-11

FORMULA_NAME Railroad-PT-020-12

FORMULA_NAME Railroad-PT-020-13

FORMULA_NAME Railroad-PT-020-14

FORMULA_NAME Railroad-PT-020-15

=== Now, execution of the tool begins

BK_START 1591374642117

bash -c /home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n "BK_STOP " ; date -u +%s%3N

[2020-06-05 16:30:44] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -timeout, 3600, -rebuildPNML]

[2020-06-05 16:30:45] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-06-05 16:30:45] [INFO ] Load time of PNML (sax parser for PT used): 194 ms

[2020-06-05 16:30:45] [INFO ] Transformed 218 places.

[2020-06-05 16:30:45] [INFO ] Transformed 506 transitions.

[2020-06-05 16:30:45] [INFO ] Parsed PT model containing 218 places and 506 transitions in 271 ms.

Deduced a syphon composed of 61 places in 8 ms

Reduce places removed 61 places and 20 transitions.

Parsed 16 properties from file /home/mcc/execution/LTLFireability.xml in 56 ms.

Working with output stream class java.io.PrintStream

Incomplete random walk after 100000 steps, including 0 resets, run finished after 826 ms. (steps per millisecond=121 ) properties seen :[1, 0, 1, 1, 1, 1, 1, 1, 1, 0, 1, 0, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 0, 1, 1, 1, 1, 0, 1, 0, 1, 0, 1, 1, 1, 1, 0, 0, 0, 1, 1, 1, 1, 0, 1, 1, 1]

// Phase 1: matrix 486 rows 157 cols

[2020-06-05 16:30:46] [INFO ] Invariants computation overflowed in 23 ms

[2020-06-05 16:30:46] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:30:46] [INFO ] [Real]Absence check using state equation in 339 ms returned sat

[2020-06-05 16:30:47] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 100 ms.

[2020-06-05 16:30:47] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:30:47] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:30:47] [INFO ] [Nat]Absence check using state equation in 259 ms returned sat

[2020-06-05 16:30:47] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 72 ms.

[2020-06-05 16:31:03] [INFO ] Added : 430 causal constraints over 86 iterations in 16268 ms. Result :unknown

[2020-06-05 16:31:03] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:03] [INFO ] [Real]Absence check using state equation in 150 ms returned unsat

[2020-06-05 16:31:04] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:04] [INFO ] [Real]Absence check using state equation in 255 ms returned sat

[2020-06-05 16:31:04] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 110 ms.

[2020-06-05 16:31:04] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:31:04] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:04] [INFO ] [Nat]Absence check using state equation in 272 ms returned sat

[2020-06-05 16:31:04] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 83 ms.

[2020-06-05 16:31:17] [INFO ] Added : 420 causal constraints over 84 iterations in 12257 ms. Result :unknown

[2020-06-05 16:31:17] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:17] [INFO ] [Real]Absence check using state equation in 302 ms returned sat

[2020-06-05 16:31:17] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 44 ms.

[2020-06-05 16:31:17] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:31:17] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:18] [INFO ] [Nat]Absence check using state equation in 351 ms returned sat

[2020-06-05 16:31:18] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 60 ms.

[2020-06-05 16:31:31] [INFO ] Added : 425 causal constraints over 85 iterations in 13482 ms. Result :sat

[2020-06-05 16:31:31] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:31] [INFO ] [Real]Absence check using state equation in 374 ms returned sat

[2020-06-05 16:31:32] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 60 ms.

[2020-06-05 16:31:32] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:31:32] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:32] [INFO ] [Nat]Absence check using state equation in 273 ms returned sat

[2020-06-05 16:31:32] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 56 ms.

[2020-06-05 16:31:41] [INFO ] Added : 466 causal constraints over 94 iterations in 9366 ms. Result :sat

[2020-06-05 16:31:41] [INFO ] Deduced a trap composed of 21 places in 50 ms

[2020-06-05 16:31:42] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 261 ms

[2020-06-05 16:31:42] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:42] [INFO ] [Real]Absence check using state equation in 340 ms returned sat

[2020-06-05 16:31:42] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 53 ms.

[2020-06-05 16:31:42] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:31:42] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:42] [INFO ] [Nat]Absence check using state equation in 233 ms returned sat

[2020-06-05 16:31:43] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 58 ms.

[2020-06-05 16:31:57] [INFO ] Added : 450 causal constraints over 90 iterations in 14380 ms. Result :unknown

[2020-06-05 16:31:57] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:57] [INFO ] [Real]Absence check using state equation in 234 ms returned sat

[2020-06-05 16:31:57] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 36 ms.

[2020-06-05 16:31:57] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:31:57] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:31:58] [INFO ] [Nat]Absence check using state equation in 264 ms returned sat

[2020-06-05 16:31:58] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 70 ms.

[2020-06-05 16:32:12] [INFO ] Added : 450 causal constraints over 90 iterations in 14335 ms. Result :unknown

[2020-06-05 16:32:12] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:12] [INFO ] [Real]Absence check using state equation in 234 ms returned sat

[2020-06-05 16:32:12] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 37 ms.

[2020-06-05 16:32:12] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:32:12] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:13] [INFO ] [Nat]Absence check using state equation in 375 ms returned sat

[2020-06-05 16:32:13] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 67 ms.

[2020-06-05 16:32:26] [INFO ] Added : 425 causal constraints over 85 iterations in 13319 ms. Result :unknown

[2020-06-05 16:32:26] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:26] [INFO ] [Real]Absence check using state equation in 230 ms returned sat

[2020-06-05 16:32:26] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 62 ms.

[2020-06-05 16:32:27] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:32:27] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:27] [INFO ] [Nat]Absence check using state equation in 343 ms returned sat

[2020-06-05 16:32:27] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 47 ms.

[2020-06-05 16:32:37] [INFO ] Added : 425 causal constraints over 85 iterations in 10157 ms. Result :sat

[2020-06-05 16:32:37] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:38] [INFO ] [Real]Absence check using state equation in 357 ms returned sat

[2020-06-05 16:32:38] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 63 ms.

[2020-06-05 16:32:38] [INFO ] Solution in real domain found non-integer solution.

[2020-06-05 16:32:38] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:38] [INFO ] [Nat]Absence check using state equation in 241 ms returned sat

[2020-06-05 16:32:38] [INFO ] Computed and/alt/rep : 466/9311/466 causal constraints in 75 ms.

[2020-06-05 16:32:56] [INFO ] Added : 430 causal constraints over 86 iterations in 18203 ms. Result :unknown

[2020-06-05 16:32:56] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-06-05 16:32:56] [INFO ] [Real]Absence check using state equation in 65 ms returned unsat

Successfully simplified 2 atomic propositions for a total of 2 simplifications.

[2020-06-05 16:32:57] [INFO ] Initial state reduction rules for CTL removed 4 formulas.

[2020-06-05 16:32:57] [INFO ] Flatten gal took : 149 ms

FORMULA Railroad-PT-020-15 TRUE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Railroad-PT-020-14 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Railroad-PT-020-08 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA Railroad-PT-020-01 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2020-06-05 16:32:57] [INFO ] Flatten gal took : 80 ms

[2020-06-05 16:32:57] [INFO ] Export to MCC properties in file /home/mcc/execution/LTLFireability.sr.xml took 5 ms.

[2020-06-05 16:32:57] [INFO ] Export to PNML in file /home/mcc/execution/model.sr.pnml took 12 ms.

info: Time: 3600 - MCC

vrfy: Checking LTLFireability @ Railroad-PT-020 @ 3570 seconds

FORMULA Railroad-PT-020-04 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-06 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-07 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-09 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-03 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-12 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-02 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

FORMULA Railroad-PT-020-00 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

TIME LIMIT: Killed by timeout after 3600 seconds

MemTotal: 16427332 kB

MemFree: 272676 kB

After kill :

MemTotal: 16427332 kB

MemFree: 16316064 kB

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="Railroad-PT-020"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="itslola"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itslola"

echo " Input is Railroad-PT-020, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r172-smll-158987827700306"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/Railroad-PT-020.tgz

mv Railroad-PT-020 execution

cd execution

if [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "UpperBounds" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] || [ "LTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "LTLFireability" = "ReachabilityDeadlock" ] || [ "LTLFireability" = "QuasiLiveness" ] || [ "LTLFireability" = "StableMarking" ] || [ "LTLFireability" = "Liveness" ] || [ "LTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME LTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;