About the Execution of ITS-Tools for LamportFastMutEx-PT-6

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15743.500 | 440482.00 | 1244088.00 | 634.40 | TTFFTTFFFTTFFTTF | normal |

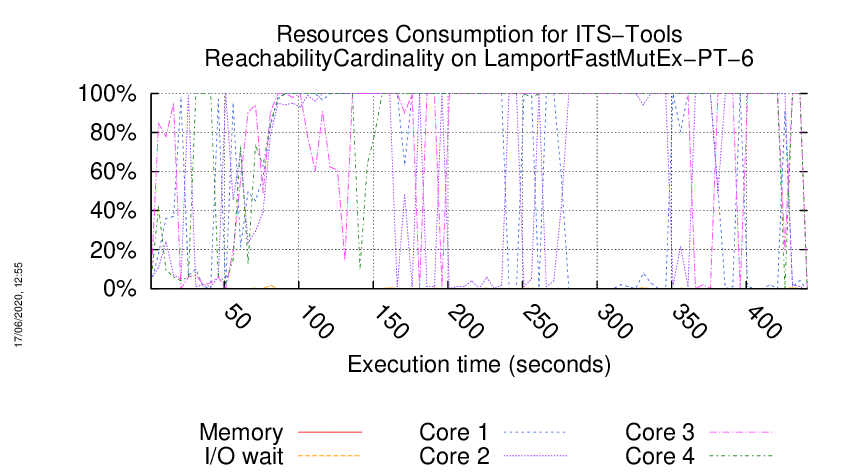

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fko/mcc2020-input.r096-oct2-158940145400678.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fko/mcc2020-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

.................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is LamportFastMutEx-PT-6, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r096-oct2-158940145400678

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 632K

-rw-r--r-- 1 mcc users 7.0K Apr 30 13:04 CTLCardinality.txt

-rw-r--r-- 1 mcc users 31K Apr 30 13:04 CTLCardinality.xml

-rw-r--r-- 1 mcc users 8.9K Apr 30 13:04 CTLFireability.txt

-rw-r--r-- 1 mcc users 42K Apr 30 13:04 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Apr 30 13:04 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.3K Apr 30 13:04 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 15K Apr 30 13:04 LTLCardinality.txt

-rw-r--r-- 1 mcc users 68K Apr 30 13:04 LTLCardinality.xml

-rw-r--r-- 1 mcc users 13K Apr 30 13:04 LTLFireability.txt

-rw-r--r-- 1 mcc users 63K Apr 30 13:04 LTLFireability.xml

-rw-r--r-- 1 mcc users 9.4K Apr 30 13:04 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 38K Apr 30 13:04 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 15K Apr 30 13:04 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 65K Apr 30 13:04 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.3K Apr 30 13:04 UpperBounds.txt

-rw-r--r-- 1 mcc users 5.4K Apr 30 13:04 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Apr 30 13:04 equiv_col

-rw-r--r-- 1 mcc users 2 Apr 30 13:04 instance

-rw-r--r-- 1 mcc users 6 Apr 30 13:04 iscolored

-rw-r--r-- 1 mcc users 200K Apr 30 13:04 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-00

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-01

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-02

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-03

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-04

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-05

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-06

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-07

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-08

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-09

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-10

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-11

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-12

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-13

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-14

FORMULA_NAME LamportFastMutEx-PT-6-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1589594450466

[2020-05-16 02:00:52] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2020-05-16 02:00:52] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-05-16 02:00:52] [INFO ] Load time of PNML (sax parser for PT used): 87 ms

[2020-05-16 02:00:52] [INFO ] Transformed 217 places.

[2020-05-16 02:00:52] [INFO ] Transformed 420 transitions.

[2020-05-16 02:00:52] [INFO ] Parsed PT model containing 217 places and 420 transitions in 163 ms.

Deduced a syphon composed of 41 places in 3 ms

Reduce places removed 41 places and 66 transitions.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 73 ms.

Working with output stream class java.io.PrintStream

Incomplete random walk after 10000 steps, including 0 resets, run finished after 121 ms. (steps per millisecond=82 ) properties seen :[1, 0, 1, 1, 0, 1, 1, 0, 0, 0, 1, 1, 1, 1, 0, 1]

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-15 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-13 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-12 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-11 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-10 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-06 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-05 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-03 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-02 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-00 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 0 resets, run finished after 23 ms. (steps per millisecond=434 ) properties seen :[0, 0, 0, 0, 0, 0]

Incomplete Best-First random walk after 10001 steps, including 0 resets, run finished after 26 ms. (steps per millisecond=384 ) properties seen :[0, 0, 0, 0, 0, 0]

Incomplete Best-First random walk after 10001 steps, including 0 resets, run finished after 13 ms. (steps per millisecond=769 ) properties seen :[0, 0, 1, 0, 0, 0]

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-07 FALSE TECHNIQUES TOPOLOGICAL BESTFIRST_WALK

Incomplete Best-First random walk after 10001 steps, including 0 resets, run finished after 9 ms. (steps per millisecond=1111 ) properties seen :[0, 0, 0, 0, 0]

Incomplete Best-First random walk after 10000 steps, including 0 resets, run finished after 34 ms. (steps per millisecond=294 ) properties seen :[0, 0, 0, 0, 0]

Incomplete Best-First random walk after 10001 steps, including 0 resets, run finished after 9 ms. (steps per millisecond=1111 ) properties seen :[0, 0, 0, 0, 0]

[2020-05-16 02:00:52] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:00:52] [INFO ] Computed 50 place invariants in 9 ms

[2020-05-16 02:00:53] [INFO ] [Real]Absence check using 50 positive place invariants in 70 ms returned sat

[2020-05-16 02:00:53] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:00:53] [INFO ] [Real]Absence check using state equation in 202 ms returned sat

[2020-05-16 02:00:53] [INFO ] State equation strengthened by 84 read => feed constraints.

[2020-05-16 02:00:53] [INFO ] [Real]Added 84 Read/Feed constraints in 33 ms returned sat

[2020-05-16 02:00:53] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:00:53] [INFO ] [Nat]Absence check using 50 positive place invariants in 19 ms returned sat

[2020-05-16 02:00:53] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:00:53] [INFO ] [Nat]Absence check using state equation in 146 ms returned sat

[2020-05-16 02:00:53] [INFO ] [Nat]Added 84 Read/Feed constraints in 19 ms returned sat

[2020-05-16 02:00:53] [INFO ] Deduced a trap composed of 9 places in 167 ms

[2020-05-16 02:00:53] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 220 ms

[2020-05-16 02:00:53] [INFO ] Computed and/alt/rep : 348/2412/258 causal constraints in 19 ms.

[2020-05-16 02:00:55] [INFO ] Added : 211 causal constraints over 43 iterations in 1572 ms. Result :sat

[2020-05-16 02:00:55] [INFO ] Deduced a trap composed of 9 places in 167 ms

[2020-05-16 02:00:56] [INFO ] Deduced a trap composed of 9 places in 1108 ms

[2020-05-16 02:00:57] [INFO ] Deduced a trap composed of 8 places in 139 ms

[2020-05-16 02:00:57] [INFO ] Deduced a trap composed of 9 places in 73 ms

[2020-05-16 02:00:57] [INFO ] Trap strengthening (SAT) tested/added 5/4 trap constraints in 1697 ms

Attempting to minimize the solution found.

Minimization took 30 ms.

[2020-05-16 02:00:57] [INFO ] [Real]Absence check using 50 positive place invariants in 16 ms returned sat

[2020-05-16 02:00:57] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:00:57] [INFO ] [Real]Absence check using state equation in 215 ms returned sat

[2020-05-16 02:00:57] [INFO ] [Real]Added 84 Read/Feed constraints in 13 ms returned sat

[2020-05-16 02:00:57] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:00:57] [INFO ] [Nat]Absence check using 50 positive place invariants in 38 ms returned sat

[2020-05-16 02:00:57] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:00:57] [INFO ] [Nat]Absence check using state equation in 176 ms returned sat

[2020-05-16 02:00:57] [INFO ] [Nat]Added 84 Read/Feed constraints in 21 ms returned sat

[2020-05-16 02:00:59] [INFO ] Deduced a trap composed of 12 places in 1274 ms

[2020-05-16 02:00:59] [INFO ] Deduced a trap composed of 26 places in 82 ms

[2020-05-16 02:00:59] [INFO ] Deduced a trap composed of 24 places in 93 ms

[2020-05-16 02:00:59] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 1518 ms

[2020-05-16 02:00:59] [INFO ] Computed and/alt/rep : 348/2412/258 causal constraints in 21 ms.

[2020-05-16 02:01:00] [INFO ] Added : 225 causal constraints over 45 iterations in 1586 ms. Result :sat

[2020-05-16 02:01:01] [INFO ] Deduced a trap composed of 15 places in 170 ms

[2020-05-16 02:01:01] [INFO ] Deduced a trap composed of 9 places in 258 ms

[2020-05-16 02:01:01] [INFO ] Deduced a trap composed of 9 places in 431 ms

[2020-05-16 02:01:01] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 978 ms

Attempting to minimize the solution found.

Minimization took 69 ms.

[2020-05-16 02:01:02] [INFO ] [Real]Absence check using 50 positive place invariants in 64 ms returned unsat

[2020-05-16 02:01:02] [INFO ] [Real]Absence check using 50 positive place invariants in 5 ms returned unsat

[2020-05-16 02:01:02] [INFO ] [Real]Absence check using 50 positive place invariants in 75 ms returned unsat

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-14 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-09 TRUE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-08 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Incomplete Parikh walk after 77900 steps, including 1000 resets, run finished after 285 ms. (steps per millisecond=273 ) properties seen :[0, 0] could not realise parikh vector

Incomplete Parikh walk after 54700 steps, including 983 resets, run finished after 221 ms. (steps per millisecond=247 ) properties seen :[0, 0] could not realise parikh vector

Support contains 42 out of 176 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 176/176 places, 354/354 transitions.

Applied a total of 0 rules in 38 ms. Remains 176 /176 variables (removed 0) and now considering 354/354 (removed 0) transitions.

Finished structural reductions, in 1 iterations. Remains : 176/176 places, 354/354 transitions.

Incomplete random walk after 1000000 steps, including 0 resets, run finished after 2135 ms. (steps per millisecond=468 ) properties seen :[0, 0]

Incomplete Best-First random walk after 1000001 steps, including 0 resets, run finished after 718 ms. (steps per millisecond=1392 ) properties seen :[1, 0]

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-01 TRUE TECHNIQUES TOPOLOGICAL BESTFIRST_WALK

Incomplete Best-First random walk after 1000001 steps, including 0 resets, run finished after 807 ms. (steps per millisecond=1239 ) properties seen :[0]

[2020-05-16 02:01:06] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:06] [INFO ] Computed 50 place invariants in 4 ms

[2020-05-16 02:01:06] [INFO ] [Real]Absence check using 50 positive place invariants in 13 ms returned sat

[2020-05-16 02:01:06] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:06] [INFO ] [Real]Absence check using state equation in 128 ms returned sat

[2020-05-16 02:01:06] [INFO ] State equation strengthened by 84 read => feed constraints.

[2020-05-16 02:01:06] [INFO ] [Real]Added 84 Read/Feed constraints in 13 ms returned sat

[2020-05-16 02:01:06] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:01:06] [INFO ] [Nat]Absence check using 50 positive place invariants in 15 ms returned sat

[2020-05-16 02:01:06] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:06] [INFO ] [Nat]Absence check using state equation in 101 ms returned sat

[2020-05-16 02:01:06] [INFO ] [Nat]Added 84 Read/Feed constraints in 12 ms returned sat

[2020-05-16 02:01:06] [INFO ] Deduced a trap composed of 12 places in 75 ms

[2020-05-16 02:01:07] [INFO ] Deduced a trap composed of 26 places in 62 ms

[2020-05-16 02:01:07] [INFO ] Deduced a trap composed of 24 places in 67 ms

[2020-05-16 02:01:07] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 251 ms

[2020-05-16 02:01:07] [INFO ] Computed and/alt/rep : 348/2412/258 causal constraints in 15 ms.

[2020-05-16 02:01:08] [INFO ] Added : 225 causal constraints over 45 iterations in 1302 ms. Result :sat

[2020-05-16 02:01:08] [INFO ] Deduced a trap composed of 15 places in 94 ms

[2020-05-16 02:01:08] [INFO ] Deduced a trap composed of 9 places in 40 ms

[2020-05-16 02:01:08] [INFO ] Deduced a trap composed of 9 places in 32 ms

[2020-05-16 02:01:08] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 285 ms

Attempting to minimize the solution found.

Minimization took 25 ms.

Incomplete Parikh walk after 77900 steps, including 1000 resets, run finished after 131 ms. (steps per millisecond=594 ) properties seen :[0] could not realise parikh vector

Support contains 30 out of 176 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 176/176 places, 354/354 transitions.

Applied a total of 0 rules in 13 ms. Remains 176 /176 variables (removed 0) and now considering 354/354 (removed 0) transitions.

Finished structural reductions, in 1 iterations. Remains : 176/176 places, 354/354 transitions.

Incomplete random walk after 1000000 steps, including 0 resets, run finished after 1657 ms. (steps per millisecond=603 ) properties seen :[0]

Incomplete Best-First random walk after 1000001 steps, including 0 resets, run finished after 833 ms. (steps per millisecond=1200 ) properties seen :[0]

Interrupted probabilistic random walk after 18767671 steps, run timeout after 30001 ms. (steps per millisecond=625 ) properties seen :[0]

Probabilistic random walk after 18767671 steps, saw 3114459 distinct states, run finished after 30002 ms. (steps per millisecond=625 ) properties seen :[0]

[2020-05-16 02:01:41] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:41] [INFO ] Computed 50 place invariants in 25 ms

[2020-05-16 02:01:41] [INFO ] [Real]Absence check using 50 positive place invariants in 113 ms returned sat

[2020-05-16 02:01:41] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:41] [INFO ] [Real]Absence check using state equation in 291 ms returned sat

[2020-05-16 02:01:41] [INFO ] State equation strengthened by 84 read => feed constraints.

[2020-05-16 02:01:41] [INFO ] [Real]Added 84 Read/Feed constraints in 14 ms returned sat

[2020-05-16 02:01:41] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:01:41] [INFO ] [Nat]Absence check using 50 positive place invariants in 68 ms returned sat

[2020-05-16 02:01:41] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:42] [INFO ] [Nat]Absence check using state equation in 371 ms returned sat

[2020-05-16 02:01:42] [INFO ] [Nat]Added 84 Read/Feed constraints in 8 ms returned sat

[2020-05-16 02:01:43] [INFO ] Deduced a trap composed of 12 places in 969 ms

[2020-05-16 02:01:45] [INFO ] Deduced a trap composed of 26 places in 2229 ms

[2020-05-16 02:01:47] [INFO ] Deduced a trap composed of 24 places in 1626 ms

[2020-05-16 02:01:47] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 4884 ms

[2020-05-16 02:01:47] [INFO ] Computed and/alt/rep : 348/2412/258 causal constraints in 23 ms.

[2020-05-16 02:01:49] [INFO ] Added : 225 causal constraints over 45 iterations in 2513 ms. Result :sat

[2020-05-16 02:01:49] [INFO ] Deduced a trap composed of 15 places in 82 ms

[2020-05-16 02:01:49] [INFO ] Deduced a trap composed of 9 places in 40 ms

[2020-05-16 02:01:50] [INFO ] Deduced a trap composed of 9 places in 380 ms

[2020-05-16 02:01:50] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 723 ms

Attempting to minimize the solution found.

Minimization took 53 ms.

Incomplete Parikh walk after 77900 steps, including 1000 resets, run finished after 135 ms. (steps per millisecond=577 ) properties seen :[0] could not realise parikh vector

Support contains 30 out of 176 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 176/176 places, 354/354 transitions.

Applied a total of 0 rules in 25 ms. Remains 176 /176 variables (removed 0) and now considering 354/354 (removed 0) transitions.

Finished structural reductions, in 1 iterations. Remains : 176/176 places, 354/354 transitions.

Starting structural reductions, iteration 0 : 176/176 places, 354/354 transitions.

Applied a total of 0 rules in 12 ms. Remains 176 /176 variables (removed 0) and now considering 354/354 (removed 0) transitions.

[2020-05-16 02:01:50] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:50] [INFO ] Computed 50 place invariants in 1 ms

[2020-05-16 02:01:51] [INFO ] Implicit Places using invariants in 432 ms returned []

[2020-05-16 02:01:51] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:51] [INFO ] Computed 50 place invariants in 2 ms

[2020-05-16 02:01:51] [INFO ] State equation strengthened by 84 read => feed constraints.

[2020-05-16 02:01:54] [INFO ] Implicit Places using invariants and state equation in 3022 ms returned []

Implicit Place search using SMT with State Equation took 3468 ms to find 0 implicit places.

[2020-05-16 02:01:54] [INFO ] Redundant transitions in 17 ms returned []

[2020-05-16 02:01:54] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:54] [INFO ] Computed 50 place invariants in 17 ms

[2020-05-16 02:01:55] [INFO ] Dead Transitions using invariants and state equation in 1611 ms returned []

Finished structural reductions, in 1 iterations. Remains : 176/176 places, 354/354 transitions.

Incomplete random walk after 100000 steps, including 0 resets, run finished after 175 ms. (steps per millisecond=571 ) properties seen :[0]

[2020-05-16 02:01:56] [INFO ] Flow matrix only has 264 transitions (discarded 90 similar events)

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:01:56] [INFO ] Computed 50 place invariants in 16 ms

[2020-05-16 02:01:56] [INFO ] [Real]Absence check using 50 positive place invariants in 295 ms returned sat

[2020-05-16 02:01:56] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:56] [INFO ] [Real]Absence check using state equation in 550 ms returned sat

[2020-05-16 02:01:56] [INFO ] State equation strengthened by 84 read => feed constraints.

[2020-05-16 02:01:56] [INFO ] [Real]Added 84 Read/Feed constraints in 22 ms returned sat

[2020-05-16 02:01:57] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:01:57] [INFO ] [Nat]Absence check using 50 positive place invariants in 335 ms returned sat

[2020-05-16 02:01:57] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:01:57] [INFO ] [Nat]Absence check using state equation in 288 ms returned sat

[2020-05-16 02:01:57] [INFO ] [Nat]Added 84 Read/Feed constraints in 17 ms returned sat

[2020-05-16 02:01:58] [INFO ] Deduced a trap composed of 12 places in 528 ms

[2020-05-16 02:01:58] [INFO ] Deduced a trap composed of 26 places in 153 ms

[2020-05-16 02:02:00] [INFO ] Deduced a trap composed of 24 places in 1995 ms

[2020-05-16 02:02:00] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 2750 ms

[2020-05-16 02:02:00] [INFO ] Computed and/alt/rep : 348/2412/258 causal constraints in 20 ms.

[2020-05-16 02:02:03] [INFO ] Added : 225 causal constraints over 45 iterations in 2853 ms. Result :sat

[2020-05-16 02:02:04] [INFO ] Deduced a trap composed of 15 places in 980 ms

[2020-05-16 02:02:05] [INFO ] Deduced a trap composed of 9 places in 629 ms

[2020-05-16 02:02:05] [INFO ] Deduced a trap composed of 9 places in 295 ms

[2020-05-16 02:02:05] [INFO ] Trap strengthening (SAT) tested/added 4/3 trap constraints in 2123 ms

Ensure Unique test removed 90 transitions

Reduce isomorphic transitions removed 90 transitions.

Iterating post reduction 0 with 90 rules applied. Total rules applied 90 place count 176 transition count 264

Performed 36 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 1 with 36 Pre rules applied. Total rules applied 90 place count 176 transition count 228

Deduced a syphon composed of 36 places in 0 ms

Ensure Unique test removed 36 places

Reduce places removed 72 places and 0 transitions.

Iterating global reduction 1 with 108 rules applied. Total rules applied 198 place count 104 transition count 228

Performed 6 Post agglomeration using F-continuation condition.Transition count delta: -30

Deduced a syphon composed of 6 places in 0 ms

Reduce places removed 6 places and 0 transitions.

Iterating global reduction 1 with 12 rules applied. Total rules applied 210 place count 98 transition count 258

Free-agglomeration rule applied 6 times.

Iterating global reduction 1 with 6 rules applied. Total rules applied 216 place count 98 transition count 252

Reduce places removed 6 places and 0 transitions.

Iterating post reduction 1 with 6 rules applied. Total rules applied 222 place count 92 transition count 252

Partial Free-agglomeration rule applied 12 times.

Drop transitions removed 12 transitions

Iterating global reduction 2 with 12 rules applied. Total rules applied 234 place count 92 transition count 252

Applied a total of 234 rules in 48 ms. Remains 92 /176 variables (removed 84) and now considering 252/354 (removed 102) transitions.

// Phase 1: matrix 252 rows 92 cols

[2020-05-16 02:02:05] [INFO ] Computed 14 place invariants in 0 ms

[2020-05-16 02:02:05] [INFO ] [Real]Absence check using 14 positive place invariants in 34 ms returned sat

[2020-05-16 02:02:05] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-16 02:02:05] [INFO ] [Real]Absence check using state equation in 156 ms returned sat

[2020-05-16 02:02:05] [INFO ] Computed and/alt/rep : 240/2010/240 causal constraints in 24 ms.

[2020-05-16 02:02:05] [INFO ] Solution in real domain found non-integer solution.

[2020-05-16 02:02:05] [INFO ] [Nat]Absence check using 14 positive place invariants in 56 ms returned sat

[2020-05-16 02:02:05] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-16 02:02:06] [INFO ] [Nat]Absence check using state equation in 194 ms returned sat

[2020-05-16 02:02:06] [INFO ] Computed and/alt/rep : 240/2010/240 causal constraints in 63 ms.

[2020-05-16 02:02:08] [INFO ] Added : 206 causal constraints over 42 iterations in 2833 ms. Result :sat

Attempting to minimize the solution found.

Minimization took 67 ms.

[2020-05-16 02:02:09] [INFO ] Flatten gal took : 200 ms

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

[2020-05-16 02:02:09] [INFO ] Applying decomposition

[2020-05-16 02:02:09] [INFO ] Flatten gal took : 50 ms

[2020-05-16 02:02:09] [INFO ] Flatten gal took : 108 ms

[2020-05-16 02:02:09] [INFO ] Input system was already deterministic with 354 transitions.

[2020-05-16 02:02:10] [INFO ] Input system was already deterministic with 354 transitions.

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/convert-linux64, -i, /tmp/graph245934949115135218.txt, -o, /tmp/graph245934949115135218.bin, -w, /tmp/graph245934949115135218.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/louvain-linux64, /tmp/graph245934949115135218.bin, -l, -1, -v, -w, /tmp/graph245934949115135218.weights, -q, 0, -e, 0.001], workingDir=null]

[2020-05-16 02:02:10] [INFO ] Decomposing Gal with order

[2020-05-16 02:02:10] [INFO ] Rewriting arrays to variables to allow decomposition.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

Normalized transition count is 264 out of 354 initially.

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:02:10] [INFO ] Computed 50 place invariants in 1 ms

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_await_13_1 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_4 + P_done_5_4 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_3 + P_done_5_3 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_4 + P_done_2_4 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_1 + P_done_1_1 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_await_13_2 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_6 + P_done_6_6 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_2 + P_done_2_2 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_6 + P_done_3_6 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_1 + P_done_5_1 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_5 + P_done_2_5 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_b_4_false + P_b_4_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_2 + P_done_4_2 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_3 + P_done_1_3 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_4 + P_done_6_4 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_b_5_false + P_b_5_true = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_6 + P_done_5_6 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_b_2_false + P_b_2_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_3 + P_done_4_3 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_4 + P_done_1_4 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_1 + P_done_2_1 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_2 + P_done_3_2 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_5 + P_done_3_5 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_b_6_false + P_b_6_true = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_1 + P_done_6_1 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_b_1_false + P_b_1_true = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_6 + P_done_1_6 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_6 + P_done_4_6 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_1 + P_done_3_1 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_await_13_6 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : x_0 + x_1 + x_2 + x_3 + x_4 + x_5 + x_6 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_await_13_5 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_3 + P_done_3_3 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_2 + P_done_6_2 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_5 + P_done_4_5 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : y_0 + y_1 + y_2 + y_3 + y_4 + y_5 + y_6 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_await_13_3 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_5 + P_done_6_5 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_await_13_4 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_4 + P_done_3_4 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_3 + P_done_6_3 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_4 + P_done_4_4 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_2 + P_done_5_2 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_5 + P_done_5_5 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_5 + P_done_1_5 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_6 + P_done_2_6 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_b_3_false + P_b_3_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_1 + P_done_4_1 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_3 + P_done_2_3 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_2 + P_done_1_2 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

Total of 50 invariants.

[2020-05-16 02:02:10] [INFO ] Computed 50 place invariants in 2 ms

[2020-05-16 02:02:10] [INFO ] Removed a total of 565 redundant transitions.

[2020-05-16 02:02:10] [INFO ] Ran tautology test, simplified 0 / 1 in 567 ms.

[2020-05-16 02:02:10] [INFO ] Flatten gal took : 389 ms

[2020-05-16 02:02:10] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=0 took 171 ms

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

Normalized transition count is 264 out of 354 initially.

// Phase 1: matrix 264 rows 176 cols

[2020-05-16 02:02:10] [INFO ] Computed 50 place invariants in 1 ms

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_await_13_1 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_4 + P_done_5_4 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_3 + P_done_5_3 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_4 + P_done_2_4 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_1 + P_done_1_1 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_await_13_2 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_6 + P_done_6_6 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_2 + P_done_2_2 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_6 + P_done_3_6 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_1 + P_done_5_1 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_5 + P_done_2_5 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_b_4_false + P_b_4_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_2 + P_done_4_2 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_3 + P_done_1_3 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_4 + P_done_6_4 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_b_5_false + P_b_5_true = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_6 + P_done_5_6 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_b_2_false + P_b_2_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_3 + P_done_4_3 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_4 + P_done_1_4 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_1 + P_done_2_1 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_2 + P_done_3_2 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_5 + P_done_3_5 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_b_6_false + P_b_6_true = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_1 + P_done_6_1 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_b_1_false + P_b_1_true = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_6 + P_done_1_6 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_6 + P_done_4_6 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_1 + P_done_3_1 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_await_13_6 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : x_0 + x_1 + x_2 + x_3 + x_4 + x_5 + x_6 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_await_13_5 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_3 + P_done_3_3 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_2 + P_done_6_2 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_5 + P_done_4_5 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : y_0 + y_1 + y_2 + y_3 + y_4 + y_5 + y_6 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_await_13_3 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_5 + P_done_6_5 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_await_13_4 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_3 + P_setx_3_3 + P_setbi_5_3 + P_ify0_4_3 + P_sety_9_3 + P_ifxi_10_3 + P_setbi_11_3 + P_fordo_12_3 + P_wait_3_4 + P_done_3_4 + P_ifyi_15_3 + P_awaity_3 + P_CS_21_3 + P_setbi_24_3 = 1

inv : P_start_1_6 + P_setx_3_6 + P_setbi_5_6 + P_ify0_4_6 + P_sety_9_6 + P_ifxi_10_6 + P_setbi_11_6 + P_fordo_12_6 + P_wait_6_3 + P_done_6_3 + P_ifyi_15_6 + P_awaity_6 + P_CS_21_6 + P_setbi_24_6 = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_4 + P_done_4_4 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_2 + P_done_5_2 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_5 + P_setx_3_5 + P_setbi_5_5 + P_ify0_4_5 + P_sety_9_5 + P_ifxi_10_5 + P_setbi_11_5 + P_fordo_12_5 + P_wait_5_5 + P_done_5_5 + P_ifyi_15_5 + P_awaity_5 + P_CS_21_5 + P_setbi_24_5 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_5 + P_done_1_5 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_6 + P_done_2_6 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_b_3_false + P_b_3_true = 1

inv : P_start_1_4 + P_setx_3_4 + P_setbi_5_4 + P_ify0_4_4 + P_sety_9_4 + P_ifxi_10_4 + P_setbi_11_4 + P_fordo_12_4 + P_wait_4_1 + P_done_4_1 + P_ifyi_15_4 + P_awaity_4 + P_CS_21_4 + P_setbi_24_4 = 1

inv : P_start_1_2 + P_setx_3_2 + P_setbi_5_2 + P_ify0_4_2 + P_sety_9_2 + P_ifxi_10_2 + P_setbi_11_2 + P_fordo_12_2 + P_wait_2_3 + P_done_2_3 + P_ifyi_15_2 + P_awaity_2 + P_CS_21_2 + P_setbi_24_2 = 1

inv : P_start_1_1 + P_setx_3_1 + P_setbi_5_1 + P_ify0_4_1 + P_sety_9_1 + P_ifxi_10_1 + P_setbi_11_1 + P_fordo_12_1 + P_wait_1_2 + P_done_1_2 + P_ifyi_15_1 + P_awaity_1 + P_CS_21_1 + P_setbi_24_1 = 1

Total of 50 invariants.

[2020-05-16 02:02:10] [INFO ] Computed 50 place invariants in 2 ms

[2020-05-16 02:02:10] [INFO ] Fuse similar labels procedure discarded/fused a total of 90 labels/synchronizations in 65 ms.

[2020-05-16 02:02:10] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=1 took 110 ms

[2020-05-16 02:02:10] [INFO ] Time to serialize gal into /home/mcc/execution/ReachabilityCardinality.pnml.gal : 5 ms

[2020-05-16 02:02:11] [INFO ] Time to serialize properties into /home/mcc/execution/ReachabilityCardinality.prop : 0 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-reach-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityCardinality.pnml.gal, -t, CGAL, -reachable-file, ReachabilityCardinality.prop, --nowitness, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

[2020-05-16 02:02:11] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=2 took 291 ms

its-reach command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-reach-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityCardinality.pnml.gal -t CGAL -reachable-file ReachabilityCardinality.prop --nowitness --gen-order FOLLOW

Loading property file ReachabilityCardinality.prop.

Read [reachable] property : LamportFastMutEx-PT-6-ReachabilityCardinality-04 with value :((((((((((gu0.P_start_1_1+gu0.P_start_1_2)+gu0.P_start_1_3)+gu0.P_start_1_4)+gu0.P_start_1_5)+gu0.P_start_1_6)<1)&&((((((gi3.gu65.P_setbi_24_1+gi3.gu65.P_setbi_24_2)+gi3.gu65.P_setbi_24_3)+gi3.gu65.P_setbi_24_4)+gi3.gu65.P_setbi_24_5)+gi3.gu65.P_setbi_24_6)<=(((((gi3.gu43.P_await_13_1+gi3.gu43.P_await_13_2)+gi3.gu43.P_await_13_3)+gi3.gu43.P_await_13_4)+gi3.gu43.P_await_13_5)+gi3.gu43.P_await_13_6)))&&((((((gu64.P_CS_21_1+gu64.P_CS_21_2)+gu64.P_CS_21_3)+gu64.P_CS_21_4)+gu64.P_CS_21_5)+gu64.P_CS_21_6)<=1))&&((((((gu20.P_fordo_12_1+gu20.P_fordo_12_2)+gu20.P_fordo_12_3)+gu20.P_fordo_12_4)+gu20.P_fordo_12_5)+gu20.P_fordo_12_6)<=(((((gi3.gu65.P_setbi_24_1+gi3.gu65.P_setbi_24_2)+gi3.gu65.P_setbi_24_3)+gi3.gu65.P_setbi_24_4)+gi3.gu65.P_setbi_24_5)+gi3.gu65.P_setbi_24_6)))&&(((((((gu0.P_start_1_1+gu0.P_start_1_2)+gu0.P_start_1_3)+gu0.P_start_1_4)+gu0.P_start_1_5)+gu0.P_start_1_6)>=6)||((((((gi3.gu65.P_setbi_24_1+gi3.gu65.P_setbi_24_2)+gi3.gu65.P_setbi_24_3)+gi3.gu65.P_setbi_24_4)+gi3.gu65.P_setbi_24_5)+gi3.gu65.P_setbi_24_6)>=3)))

SDD proceeding with computation, new max is 4

SDD proceeding with computation, new max is 8

SDD proceeding with computation, new max is 16

SDD proceeding with computation, new max is 32

SDD proceeding with computation, new max is 64

SDD proceeding with computation, new max is 128

SDD proceeding with computation, new max is 256

SDD proceeding with computation, new max is 512

SDD proceeding with computation, new max is 1024

SDD proceeding with computation, new max is 2048

SDD proceeding with computation, new max is 4096

[2020-05-16 02:02:12] [INFO ] Proved 176 variables to be positive in 2457 ms

[2020-05-16 02:02:12] [INFO ] Computing symmetric may disable matrix : 354 transitions.

[2020-05-16 02:02:12] [INFO ] Computation of disable matrix completed :0/354 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-16 02:02:12] [INFO ] Computation of Complete disable matrix. took 74 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-16 02:02:12] [INFO ] Computing symmetric may enable matrix : 354 transitions.

[2020-05-16 02:02:12] [INFO ] Computation of Complete enable matrix. took 76 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-16 02:02:12] [INFO ] Proved 176 variables to be positive in 2261 ms

[2020-05-16 02:02:13] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:02:13] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=0 took 71 ms

SDD proceeding with computation, new max is 8192

[2020-05-16 02:02:13] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:02:13] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=1 took 83 ms

[2020-05-16 02:02:14] [INFO ] Computing symmetric co enabling matrix : 354 transitions.

SDD proceeding with computation, new max is 16384

[2020-05-16 02:02:14] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:02:14] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=2 took 1802 ms

[2020-05-16 02:02:15] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=3 took 4713 ms

[2020-05-16 02:02:16] [INFO ] Computation of co-enabling matrix(15/354) took 2143 ms. Total solver calls (SAT/UNSAT): 1248(70/1178)

[2020-05-16 02:02:19] [INFO ] Computation of co-enabling matrix(24/354) took 5264 ms. Total solver calls (SAT/UNSAT): 2310(154/2156)

[2020-05-16 02:02:22] [INFO ] Computation of co-enabling matrix(41/354) took 8393 ms. Total solver calls (SAT/UNSAT): 4095(280/3815)

SDD proceeding with computation, new max is 32768

[2020-05-16 02:02:25] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=4 took 9503 ms

[2020-05-16 02:02:25] [INFO ] Computation of co-enabling matrix(60/354) took 11640 ms. Total solver calls (SAT/UNSAT): 6518(484/6034)

[2020-05-16 02:02:28] [INFO ] Computation of co-enabling matrix(70/354) took 14669 ms. Total solver calls (SAT/UNSAT): 8343(669/7674)

[2020-05-16 02:02:31] [INFO ] Computation of co-enabling matrix(82/354) took 17790 ms. Total solver calls (SAT/UNSAT): 10401(869/9532)

[2020-05-16 02:02:35] [INFO ] Computation of co-enabling matrix(103/354) took 20861 ms. Total solver calls (SAT/UNSAT): 12416(1054/11362)

[2020-05-16 02:02:38] [INFO ] Computation of co-enabling matrix(109/354) took 24032 ms. Total solver calls (SAT/UNSAT): 13325(1179/12146)

[2020-05-16 02:02:40] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:02:40] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=3 took 25018 ms

[2020-05-16 02:02:41] [INFO ] Computation of co-enabling matrix(124/354) took 27522 ms. Total solver calls (SAT/UNSAT): 15440(1406/14034)

[2020-05-16 02:02:44] [INFO ] Computation of co-enabling matrix(140/354) took 30697 ms. Total solver calls (SAT/UNSAT): 17448(1611/15837)

[2020-05-16 02:02:48] [INFO ] Computation of co-enabling matrix(150/354) took 34307 ms. Total solver calls (SAT/UNSAT): 18573(1720/16853)

[2020-05-16 02:02:51] [INFO ] Computation of co-enabling matrix(153/354) took 37763 ms. Total solver calls (SAT/UNSAT): 18891(1750/17141)

SDD proceeding with computation, new max is 65536

[2020-05-16 02:02:55] [INFO ] Computation of co-enabling matrix(157/354) took 41379 ms. Total solver calls (SAT/UNSAT): 19231(1780/17451)

[2020-05-16 02:02:58] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=5 took 33342 ms

[2020-05-16 02:02:58] [INFO ] Computation of co-enabling matrix(162/354) took 44689 ms. Total solver calls (SAT/UNSAT): 19546(1804/17742)

[2020-05-16 02:03:01] [INFO ] Computation of co-enabling matrix(177/354) took 47728 ms. Total solver calls (SAT/UNSAT): 20341(1856/18485)

[2020-05-16 02:03:04] [INFO ] Computation of co-enabling matrix(253/354) took 50746 ms. Total solver calls (SAT/UNSAT): 22551(2135/20416)

[2020-05-16 02:03:08] [INFO ] Computation of co-enabling matrix(268/354) took 54052 ms. Total solver calls (SAT/UNSAT): 23706(2272/21434)

[2020-05-16 02:03:11] [INFO ] Computation of co-enabling matrix(277/354) took 57255 ms. Total solver calls (SAT/UNSAT): 24291(2338/21953)

[2020-05-16 02:03:14] [INFO ] Computation of co-enabling matrix(285/354) took 60549 ms. Total solver calls (SAT/UNSAT): 24743(2388/22355)

[2020-05-16 02:03:17] [INFO ] Computation of co-enabling matrix(291/354) took 63667 ms. Total solver calls (SAT/UNSAT): 25040(2420/22620)

[2020-05-16 02:03:21] [INFO ] Computation of co-enabling matrix(321/354) took 66865 ms. Total solver calls (SAT/UNSAT): 25915(2516/23399)

[2020-05-16 02:03:22] [INFO ] Computation of Finished co-enabling matrix. took 67980 ms. Total solver calls (SAT/UNSAT): 26151(2535/23616)

[2020-05-16 02:03:22] [INFO ] Computing Do-Not-Accords matrix : 354 transitions.

[2020-05-16 02:03:22] [INFO ] Computation of Completed DNA matrix. took 29 ms. Total solver calls (SAT/UNSAT): 0(0/0)

[2020-05-16 02:03:22] [INFO ] Built C files in 72455ms conformant to PINS in folder :/home/mcc/execution

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/home/mcc/execution]

SDD proceeding with computation, new max is 131072

Compilation finished in 11102 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 130 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -i, LamportFastMutExPT6ReachabilityCardinality04==true], workingDir=/home/mcc/execution]

/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc: error while loading shared libraries: libltdl.so.7: cannot open shared object file: No such file or directory

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -i, LamportFastMutExPT6ReachabilityCardinality04==true], workingDir=/home/mcc/execution]

127

java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, -i, LamportFastMutExPT6ReachabilityCardinality04==true], workingDir=/home/mcc/execution]

127

at fr.lip6.move.gal.application.LTSminRunner.checkProperty(LTSminRunner.java:170)

at fr.lip6.move.gal.application.LTSminRunner.access$10(LTSminRunner.java:124)

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:93)

at java.base/java.lang.Thread.run(Thread.java:834)

SDD proceeding with computation, new max is 262144

[2020-05-16 02:04:54] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=6 took 116069 ms

[2020-05-16 02:05:05] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:05:05] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=4 took 145953 ms

Reachability property LamportFastMutEx-PT-6-ReachabilityCardinality-04 is true.

FORMULA LamportFastMutEx-PT-6-ReachabilityCardinality-04 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL COLLATERAL_PROCESSING USE_NUPN

Found states matching all0 target predicate

Will report total states built up to this point. Computation was interrupted after 262145 fixpoint passes

[2020-05-16 02:07:51] [INFO ] Induction result is SAT, non conclusive we might be starting from unreachable statesLamportFastMutEx-PT-6-ReachabilityCardinality-04

[2020-05-16 02:07:51] [INFO ] KInduction solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(SAT) depth K=5 took 165782 ms

[2020-05-16 02:08:06] [INFO ] BMC solution for property LamportFastMutEx-PT-6-ReachabilityCardinality-04(UNSAT) depth K=7 took 191477 ms

[2020-05-16 02:08:06] [INFO ] SMT solved 0/ 1 properties. Interrupting SMT analysis.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

petri\_inst\_inst\_mod\_flatf,6.51803e+08,354.557,4387076,2,458834,23,9.96796e+06,6,0,1055,1.51653e+07,0

Total reachable state count : 651802630

Verifying 1 reachability properties.

Reachability property LamportFastMutEx-PT-6-ReachabilityCardinality-04 is true.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

LamportFastMutEx-PT-6-ReachabilityCardinality-04,27648,356.531,4387076,2,385,23,9.96796e+06,4,0,1290,1.51653e+07,0

BK_STOP 1589594890948

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityCardinality -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="LamportFastMutEx-PT-6"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is LamportFastMutEx-PT-6, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r096-oct2-158940145400678"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/LamportFastMutEx-PT-6.tgz

mv LamportFastMutEx-PT-6 execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;