About the Execution of ITS-Tools for FamilyReunion-PT-L00010M0001C001P001G001

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15741.370 | 12285.00 | 23552.00 | 258.40 | TTTTTTFTTFTFFTFF | normal |

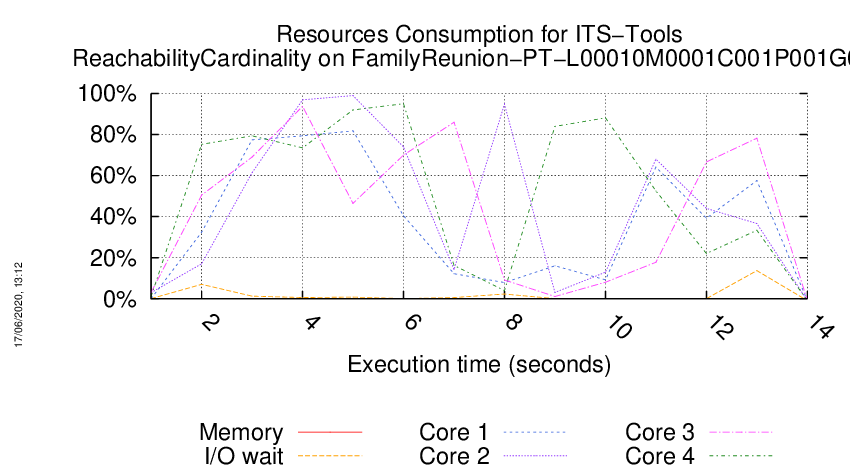

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2020-input.r081-smll-158922977600214.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2020-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

..............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is FamilyReunion-PT-L00010M0001C001P001G001, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r081-smll-158922977600214

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 960K

-rw-r--r-- 1 mcc users 11K Apr 1 20:23 CTLCardinality.txt

-rw-r--r-- 1 mcc users 48K Apr 1 20:23 CTLCardinality.xml

-rw-r--r-- 1 mcc users 18K Apr 1 13:50 CTLFireability.txt

-rw-r--r-- 1 mcc users 55K Apr 1 13:50 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 24 05:37 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.7K Mar 24 05:37 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 9.6K Apr 8 14:53 LTLCardinality.txt

-rw-r--r-- 1 mcc users 51K Apr 28 14:01 LTLCardinality.xml

-rw-r--r-- 1 mcc users 15K Apr 8 14:53 LTLFireability.txt

-rw-r--r-- 1 mcc users 49K Apr 28 14:01 LTLFireability.xml

-rw-r--r-- 1 mcc users 11K Apr 1 10:51 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 47K Apr 1 10:51 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 11K Apr 1 06:34 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 30K Apr 1 06:34 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 3.1K Apr 1 13:18 UpperBounds.txt

-rw-r--r-- 1 mcc users 7.3K Apr 1 13:18 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Mar 24 05:37 equiv_col

-rw-r--r-- 1 mcc users 24 Mar 24 05:37 instance

-rw-r--r-- 1 mcc users 6 Mar 24 05:37 iscolored

-rw-r--r-- 1 mcc users 552K Mar 24 05:37 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-00

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-01

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-02

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-03

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-04

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-05

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-06

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-07

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-08

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-09

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-10

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-11

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-12

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-13

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-14

FORMULA_NAME FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-15

=== Now, execution of the tool begins

BK_START 1589577798879

[2020-05-15 21:23:21] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityCardinality, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2020-05-15 21:23:21] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-05-15 21:23:21] [INFO ] Load time of PNML (sax parser for PT used): 287 ms

[2020-05-15 21:23:22] [INFO ] Transformed 1475 places.

[2020-05-15 21:23:22] [INFO ] Transformed 1234 transitions.

[2020-05-15 21:23:22] [INFO ] Parsed PT model containing 1475 places and 1234 transitions in 365 ms.

Reduce places removed 10 places and 0 transitions.

Parsed 16 properties from file /home/mcc/execution/ReachabilityCardinality.xml in 117 ms.

Working with output stream class java.io.PrintStream

Incomplete random walk after 10000 steps, including 15 resets, run finished after 156 ms. (steps per millisecond=64 ) properties seen :[1, 1, 0, 1, 1, 1, 1, 1, 1, 0, 1, 1, 1, 1, 0, 0]

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-13 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-12 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-11 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-10 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-08 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-07 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-06 FALSE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-05 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-04 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-03 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-01 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-00 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

Incomplete Best-First random walk after 10001 steps, including 1 resets, run finished after 72 ms. (steps per millisecond=138 ) properties seen :[0, 0, 0, 0]

Incomplete Best-First random walk after 10001 steps, including 1 resets, run finished after 28 ms. (steps per millisecond=357 ) properties seen :[0, 0, 0, 0]

Incomplete Best-First random walk after 10000 steps, including 1 resets, run finished after 27 ms. (steps per millisecond=370 ) properties seen :[0, 0, 0, 0]

Incomplete Best-First random walk after 10001 steps, including 1 resets, run finished after 36 ms. (steps per millisecond=277 ) properties seen :[0, 0, 0, 0]

// Phase 1: matrix 1234 rows 1465 cols

[2020-05-15 21:23:22] [INFO ] Computed 332 place invariants in 163 ms

[2020-05-15 21:23:23] [INFO ] [Real]Absence check using 30 positive place invariants in 95 ms returned sat

[2020-05-15 21:23:23] [INFO ] [Real]Absence check using 30 positive and 302 generalized place invariants in 523 ms returned sat

[2020-05-15 21:23:23] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-15 21:23:27] [INFO ] [Real]Absence check using state equation in 3961 ms returned (error "Solver has unexpectedly terminated")

[2020-05-15 21:23:28] [INFO ] [Real]Absence check using 30 positive place invariants in 104 ms returned sat

[2020-05-15 21:23:28] [INFO ] [Real]Absence check using 30 positive and 302 generalized place invariants in 222 ms returned unsat

[2020-05-15 21:23:28] [INFO ] [Real]Absence check using 30 positive place invariants in 99 ms returned sat

[2020-05-15 21:23:28] [INFO ] [Real]Absence check using 30 positive and 302 generalized place invariants in 137 ms returned unsat

[2020-05-15 21:23:29] [INFO ] [Real]Absence check using 30 positive place invariants in 107 ms returned sat

[2020-05-15 21:23:29] [INFO ] [Real]Absence check using 30 positive and 302 generalized place invariants in 380 ms returned unsat

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-15 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-14 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-09 FALSE TECHNIQUES STRUCTURAL_REDUCTION TOPOLOGICAL SAT_SMT

Support contains 79 out of 1465 places. Attempting structural reductions.

Starting structural reductions, iteration 0 : 1465/1465 places, 1234/1234 transitions.

Discarding 480 places :

Also discarding 418 output transitions

Drop transitions removed 418 transitions

Graph (complete) has 2215 edges and 1465 vertex of which 985 are kept as prefixes of interest. Removing 480 places using SCC suffix rule.38 ms

Discarding 132 places :

Implicit places reduction removed 132 places

Performed 352 Post agglomeration using F-continuation condition.Transition count delta: 352

Iterating post reduction 0 with 484 rules applied. Total rules applied 485 place count 853 transition count 464

Reduce places removed 352 places and 0 transitions.

Iterating post reduction 1 with 352 rules applied. Total rules applied 837 place count 501 transition count 464

Performed 66 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 2 with 66 Pre rules applied. Total rules applied 837 place count 501 transition count 398

Deduced a syphon composed of 66 places in 2 ms

Ensure Unique test removed 22 places

Reduce places removed 88 places and 0 transitions.

Iterating global reduction 2 with 154 rules applied. Total rules applied 991 place count 413 transition count 398

Symmetric choice reduction at 2 with 55 rule applications. Total rules 1046 place count 413 transition count 398

Deduced a syphon composed of 55 places in 1 ms

Reduce places removed 55 places and 55 transitions.

Iterating global reduction 2 with 110 rules applied. Total rules applied 1156 place count 358 transition count 343

Ensure Unique test removed 11 transitions

Reduce isomorphic transitions removed 11 transitions.

Discarding 22 places :

Implicit places reduction removed 22 places

Performed 44 Post agglomeration using F-continuation condition.Transition count delta: 44

Iterating post reduction 2 with 77 rules applied. Total rules applied 1233 place count 336 transition count 288

Reduce places removed 44 places and 0 transitions.

Iterating post reduction 3 with 44 rules applied. Total rules applied 1277 place count 292 transition count 288

Performed 11 Pre agglomeration using Quasi-Persistent + Divergent Free condition..

Pre-agglomeration after 4 with 11 Pre rules applied. Total rules applied 1277 place count 292 transition count 277

Deduced a syphon composed of 11 places in 1 ms

Reduce places removed 11 places and 0 transitions.

Iterating global reduction 4 with 22 rules applied. Total rules applied 1299 place count 281 transition count 277

Symmetric choice reduction at 4 with 2 rule applications. Total rules 1301 place count 281 transition count 277

Deduced a syphon composed of 2 places in 0 ms

Reduce places removed 2 places and 22 transitions.

Iterating global reduction 4 with 4 rules applied. Total rules applied 1305 place count 279 transition count 255

Discarding 22 places :

Implicit places reduction removed 22 places

Iterating post reduction 4 with 22 rules applied. Total rules applied 1327 place count 257 transition count 255

Symmetric choice reduction at 5 with 11 rule applications. Total rules 1338 place count 257 transition count 255

Deduced a syphon composed of 11 places in 0 ms

Reduce places removed 11 places and 11 transitions.

Iterating global reduction 5 with 22 rules applied. Total rules applied 1360 place count 246 transition count 244

Performed 33 Post agglomeration using F-continuation condition.Transition count delta: 33

Deduced a syphon composed of 33 places in 4 ms

Reduce places removed 33 places and 0 transitions.

Iterating global reduction 5 with 66 rules applied. Total rules applied 1426 place count 213 transition count 211

Free-agglomeration rule (complex) applied 11 times.

Iterating global reduction 5 with 11 rules applied. Total rules applied 1437 place count 213 transition count 200

Reduce places removed 11 places and 0 transitions.

Iterating post reduction 5 with 11 rules applied. Total rules applied 1448 place count 202 transition count 200

Applied a total of 1448 rules in 323 ms. Remains 202 /1465 variables (removed 1263) and now considering 200/1234 (removed 1034) transitions.

Finished structural reductions, in 1 iterations. Remains : 202/1465 places, 200/1234 transitions.

Finished random walk after 6224 steps, including 39 resets, run visited all 1 properties in 39 ms. (steps per millisecond=159 )

FORMULA FamilyReunion-PT-L00010M0001C001P001G001-ReachabilityCardinality-02 TRUE TECHNIQUES TOPOLOGICAL RANDOM_WALK

All properties solved without resorting to model-checking.

BK_STOP 1589577811164

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ ReachabilityCardinality = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityCardinality -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityCardinality -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FamilyReunion-PT-L00010M0001C001P001G001"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is FamilyReunion-PT-L00010M0001C001P001G001, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r081-smll-158922977600214"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/FamilyReunion-PT-L00010M0001C001P001G001.tgz

mv FamilyReunion-PT-L00010M0001C001P001G001 execution

cd execution

if [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "UpperBounds" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] || [ "ReachabilityCardinality" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "ReachabilityCardinality" = "ReachabilityDeadlock" ] || [ "ReachabilityCardinality" = "QuasiLiveness" ] || [ "ReachabilityCardinality" = "StableMarking" ] || [ "ReachabilityCardinality" = "Liveness" ] || [ "ReachabilityCardinality" = "OneSafe" ] ; then

echo "FORMULA_NAME ReachabilityCardinality"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;