About the Execution of ITS-Tools for DiscoveryGPU-PT-15b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15741.730 | 3600000.00 | 3587015.00 | 64644.10 | TFTFTTFF???????? | normal |

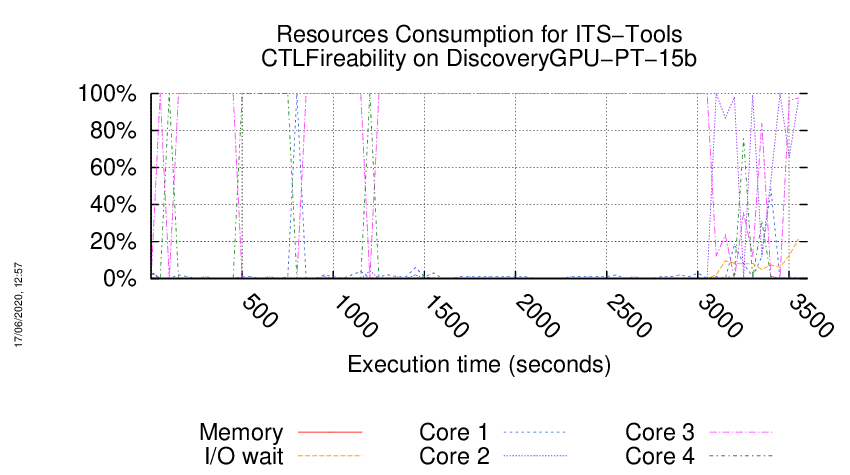

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2020-input.r066-tajo-158922814800740.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2020-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is DiscoveryGPU-PT-15b, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r066-tajo-158922814800740

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 292K

-rw-r--r-- 1 mcc users 3.4K Mar 31 07:41 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K Mar 31 07:41 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.3K Mar 30 00:27 CTLFireability.txt

-rw-r--r-- 1 mcc users 15K Mar 30 00:27 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 24 05:37 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.3K Mar 24 05:37 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.3K Apr 8 14:50 LTLCardinality.txt

-rw-r--r-- 1 mcc users 25K Apr 28 14:00 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.0K Apr 8 14:50 LTLFireability.txt

-rw-r--r-- 1 mcc users 18K Apr 28 14:00 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.4K Mar 28 14:44 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 17K Mar 28 14:44 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.9K Mar 27 07:46 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 19K Mar 27 07:46 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K Mar 28 14:50 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K Mar 28 14:50 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 24 05:37 equiv_col

-rw-r--r-- 1 mcc users 4 Mar 24 05:37 instance

-rw-r--r-- 1 mcc users 6 Mar 24 05:37 iscolored

-rw-r--r-- 1 mcc users 111K Mar 24 05:37 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-00

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-01

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-02

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-03

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-04

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-05

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-06

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-07

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-08

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-09

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-10

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-11

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-12

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-13

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-14

FORMULA_NAME DiscoveryGPU-PT-15b-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1590132924256

[2020-05-22 07:35:26] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2020-05-22 07:35:26] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-05-22 07:35:26] [INFO ] Load time of PNML (sax parser for PT used): 83 ms

[2020-05-22 07:35:26] [INFO ] Transformed 436 places.

[2020-05-22 07:35:26] [INFO ] Transformed 464 transitions.

[2020-05-22 07:35:26] [INFO ] Found NUPN structural information;

[2020-05-22 07:35:26] [INFO ] Parsed PT model containing 436 places and 464 transitions in 134 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 25 ms.

Incomplete random walk after 100000 steps, including 204 resets, run finished after 272 ms. (steps per millisecond=367 ) properties seen :[1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 0, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 0, 1, 1, 1, 0, 1, 1, 1, 1]

// Phase 1: matrix 464 rows 436 cols

[2020-05-22 07:35:27] [INFO ] Computed 17 place invariants in 32 ms

[2020-05-22 07:35:27] [INFO ] [Real]Absence check using 17 positive place invariants in 37 ms returned unsat

[2020-05-22 07:35:27] [INFO ] [Real]Absence check using 17 positive place invariants in 16 ms returned sat

[2020-05-22 07:35:27] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-22 07:35:27] [INFO ] [Real]Absence check using state equation in 354 ms returned sat

[2020-05-22 07:35:28] [INFO ] Deduced a trap composed of 17 places in 333 ms

[2020-05-22 07:35:28] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 400 ms

[2020-05-22 07:35:28] [INFO ] Solution in real domain found non-integer solution.

[2020-05-22 07:35:29] [INFO ] [Nat]Absence check using 17 positive place invariants in 745 ms returned sat

[2020-05-22 07:35:29] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-22 07:35:29] [INFO ] [Nat]Absence check using state equation in 513 ms returned sat

[2020-05-22 07:35:29] [INFO ] Deduced a trap composed of 17 places in 138 ms

[2020-05-22 07:35:29] [INFO ] Trap strengthening (SAT) tested/added 2/1 trap constraints in 184 ms

[2020-05-22 07:35:29] [INFO ] Computed and/alt/rep : 463/1133/463 causal constraints in 35 ms.

[2020-05-22 07:35:32] [INFO ] Added : 372 causal constraints over 75 iterations in 2365 ms. Result :sat

[2020-05-22 07:35:32] [INFO ] [Real]Absence check using 17 positive place invariants in 20 ms returned sat

[2020-05-22 07:35:32] [INFO ] [Real]Adding state equation constraints to refine reachable states.

[2020-05-22 07:35:32] [INFO ] [Real]Absence check using state equation in 342 ms returned sat

[2020-05-22 07:35:32] [INFO ] Computed and/alt/rep : 463/1133/463 causal constraints in 51 ms.

[2020-05-22 07:35:32] [INFO ] Solution in real domain found non-integer solution.

[2020-05-22 07:35:33] [INFO ] [Nat]Absence check using 17 positive place invariants in 867 ms returned sat

[2020-05-22 07:35:33] [INFO ] [Nat]Adding state equation constraints to refine reachable states.

[2020-05-22 07:35:34] [INFO ] [Nat]Absence check using state equation in 393 ms returned sat

[2020-05-22 07:35:34] [INFO ] Computed and/alt/rep : 463/1133/463 causal constraints in 43 ms.

[2020-05-22 07:35:36] [INFO ] Added : 369 causal constraints over 74 iterations in 2313 ms. Result :sat

Successfully simplified 1 atomic propositions for a total of 1 simplifications.

[2020-05-22 07:35:36] [INFO ] Flatten gal took : 77 ms

[2020-05-22 07:35:36] [INFO ] Flatten gal took : 28 ms

[2020-05-22 07:35:36] [INFO ] Applying decomposition

[2020-05-22 07:35:36] [INFO ] Flatten gal took : 22 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/convert-linux64, -i, /tmp/graph16461304543238496643.txt, -o, /tmp/graph16461304543238496643.bin, -w, /tmp/graph16461304543238496643.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/louvain-linux64, /tmp/graph16461304543238496643.bin, -l, -1, -v, -w, /tmp/graph16461304543238496643.weights, -q, 0, -e, 0.001], workingDir=null]

[2020-05-22 07:35:37] [INFO ] Decomposing Gal with order

[2020-05-22 07:35:37] [INFO ] Rewriting arrays to variables to allow decomposition.

[2020-05-22 07:35:37] [INFO ] Removed a total of 130 redundant transitions.

[2020-05-22 07:35:37] [INFO ] Flatten gal took : 117 ms

[2020-05-22 07:35:37] [INFO ] Fuse similar labels procedure discarded/fused a total of 0 labels/synchronizations in 6 ms.

[2020-05-22 07:35:37] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 9 ms

[2020-05-22 07:35:37] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 16 CTL formulae.

built 109 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 8 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 11 ordering constraints for composite.

built 6 ordering constraints for composite.

built 6 ordering constraints for composite.

built 6 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 4 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 10 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 5 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 8 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 7 ordering constraints for composite.

built 6 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 8 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 6 ordering constraints for composite.

built 3 ordering constraints for composite.

built 5 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 8 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 8 ordering constraints for composite.

built 6 ordering constraints for composite.

built 4 ordering constraints for composite.

built 6 ordering constraints for composite.

built 5 ordering constraints for composite.

built 4 ordering constraints for composite.

built 3 ordering constraints for composite.

built 6 ordering constraints for composite.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.54856e+22,474.657,7886792,422858,47,1.65364e+07,439,712,2.36049e+07,54,1810,0

Converting to forward existential form...Done !

original formula: EG(((i34.u131.p348!=1)||(i33.u128.p340==1)))

=> equivalent forward existential formula: [FwdG(Init,((i34.u131.p348!=1)||(i33.u128.p340==1)))] != FALSE

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Fast SCC detection found an SCC at level 18

Fast SCC detection found an SCC at level 19

Fast SCC detection found an SCC at level 20

Fast SCC detection found an SCC at level 21

Fast SCC detection found an SCC at level 22

Fast SCC detection found an SCC at level 23

Fast SCC detection found an SCC at level 24

Fast SCC detection found an SCC at level 25

Fast SCC detection found an SCC at level 26

Fast SCC detection found an SCC at level 27

Fast SCC detection found an SCC at level 28

Fast SCC detection found an SCC at level 29

Fast SCC detection found an SCC at level 30

Fast SCC detection found an SCC at level 31

Fast SCC detection found an SCC at level 32

Fast SCC detection found an SCC at level 33

Fast SCC detection found an SCC at level 34

Fast SCC detection found an SCC at level 35

Fast SCC detection found an SCC at level 36

Fast SCC detection found an SCC at level 37

Fast SCC detection found an SCC at level 38

Fast SCC detection found an SCC at level 39

Fast SCC detection found an SCC at level 40

Fast SCC detection found an SCC at level 41

(forward)formula 0,1,1128.92,14284980,1,0,2.94612e+07,463,3009,4.40931e+07,208,2286,70092557

FORMULA DiscoveryGPU-PT-15b-CTLFireability-00 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is TRUE !

***************************************

original formula: (!(EX(AG((i33.u128.p340==1)))) * !(E((i21.i0.u80.p213!=1) U ((i38.i1.u151.p406==1)&&(u158.p427==1)))))

=> equivalent forward existential formula: ([(EY(Init) * !(E(TRUE U !((i33.u128.p340==1)))))] = FALSE * [(FwdU(Init,(i21.i0.u80.p213!=1)) * ((i38.i1.u151.p406==1)&&(u158.p427==1)))] = FALSE)

(forward)formula 1,0,1170.42,15221124,1,0,3.12701e+07,463,3085,4.67771e+07,210,2286,76636678

FORMULA DiscoveryGPU-PT-15b-CTLFireability-01 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is FALSE !

***************************************

original formula: EF(((i10.i1.u31.p80==1)||((i39.i1.u154.p414==1)&&(i41.i1.u160.p434==1))))

=> equivalent forward existential formula: [(FwdU(Init,TRUE) * ((i10.i1.u31.p80==1)||((i39.i1.u154.p414==1)&&(i41.i1.u160.p434==1))))] != FALSE

(forward)formula 2,1,1174.2,15278676,1,0,3.13764e+07,463,3096,4.71032e+07,211,2286,76938039

FORMULA DiscoveryGPU-PT-15b-CTLFireability-02 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is TRUE !

Detected timeout of ITS tools.

[2020-05-22 07:55:40] [INFO ] Applying decomposition

[2020-05-22 07:55:40] [INFO ] Flatten gal took : 35 ms

[2020-05-22 07:55:40] [INFO ] Decomposing Gal with order

[2020-05-22 07:55:40] [INFO ] Rewriting arrays to variables to allow decomposition.

[2020-05-22 07:55:40] [INFO ] Removed a total of 130 redundant transitions.

[2020-05-22 07:55:41] [INFO ] Flatten gal took : 80 ms

[2020-05-22 07:55:41] [INFO ] Fuse similar labels procedure discarded/fused a total of 1184 labels/synchronizations in 44 ms.

[2020-05-22 07:55:41] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 7 ms

[2020-05-22 07:55:41] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 1 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 13 CTL formulae.

built 2 ordering constraints for composite.

built 17 ordering constraints for composite.

built 17 ordering constraints for composite.

built 17 ordering constraints for composite.

built 17 ordering constraints for composite.

built 17 ordering constraints for composite.

built 17 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 12 ordering constraints for composite.

built 7 ordering constraints for composite.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.54856e+22,199.385,3685848,859,577,6.26953e+06,52414,309,2.08868e+07,153,817989,0

Converting to forward existential form...Done !

original formula: EG(EF(AG((i0.i0.u28.p366==1))))

=> equivalent forward existential formula: [FwdG(Init,E(TRUE U !(E(TRUE U !((i0.i0.u28.p366==1))))))] != FALSE

Reverse transition relation is NOT exact ! Due to transitions i0.u29.t17, i0.u29.t23, i0.u29.t27, i0.u29.t29, i0.u29.t31, i0.u29.t33, i0.i0.u28.t36, i0.i0.u28.t42, i0.i0.u28.t46, i0.i0.u28.t48, i0.i0.u28.t50, i0.i0.u28.t52, i0.i0.i0.u27.t55, i0.i0.i0.u27.t61, i0.i0.i0.u27.t65, i0.i0.i0.u27.t67, i0.i0.i0.u27.t69, i0.i0.i0.u27.t71, i0.i0.i0.i0.u26.t74, i0.i0.i0.i0.u26.t80, i0.i0.i0.i0.u26.t84, i0.i0.i0.i0.u26.t86, i0.i0.i0.i0.u26.t88, i0.i0.i0.i0.u26.t90, i0.i0.i0.i0.i0.u25.t93, i0.i0.i0.i0.i0.u25.t99, i0.i0.i0.i0.i0.u25.t103, i0.i0.i0.i0.i0.u25.t105, i0.i0.i0.i0.i0.u25.t107, i0.i0.i0.i0.i0.u25.t109, i0.i0.i0.i0.i0.i0.u24.t112, i0.i0.i0.i0.i0.i0.u24.t118, i0.i0.i0.i0.i0.i0.u24.t122, i0.i0.i0.i0.i0.i0.u24.t124, i0.i0.i0.i0.i0.i0.u24.t126, i0.i0.i0.i0.i0.i0.u24.t128, i0.i0.i0.i0.i0.i0.i0.u23.t131, i0.i0.i0.i0.i0.i0.i0.u23.t137, i0.i0.i0.i0.i0.i0.i0.u23.t141, i0.i0.i0.i0.i0.i0.i0.u23.t143, i0.i0.i0.i0.i0.i0.i0.u23.t145, i0.i0.i0.i0.i0.i0.i0.u23.t147, i0.i0.i0.i0.i0.i0.i0.i0.u22.t150, i0.i0.i0.i0.i0.i0.i0.i0.u22.t156, i0.i0.i0.i0.i0.i0.i0.i0.u22.t160, i0.i0.i0.i0.i0.i0.i0.i0.u22.t162, i0.i0.i0.i0.i0.i0.i0.i0.u22.t164, i0.i0.i0.i0.i0.i0.i0.i0.u22.t166, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t169, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t175, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t179, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t181, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t183, i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.t185, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t188, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t194, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t198, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t200, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t202, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u20.t204, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t207, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t213, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t217, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t219, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t221, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u19.t223, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t226, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t232, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t236, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t238, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t240, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.t242, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t245, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t251, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t255, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t257, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t259, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u17.t261, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t282, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t288, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t292, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t294, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t296, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u15.t298, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t264, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t270, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t274, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t276, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t278, i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.t280, i1.u31.t9, i1.u31.t11, i1.u31.t12, i1.u31.t14, i1.u32.t3, i1.u32.t4, i1.u32.t6, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/242/97/339

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Fast SCC detection found an SCC at level 2

(forward)formula 0,0,201.738,3685848,1,0,6.26953e+06,52414,6234,2.08868e+07,865,817989,423666

FORMULA DiscoveryGPU-PT-15b-CTLFireability-03 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is FALSE !

***************************************

original formula: (!(EF(EX(((i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.p117==1)&&(i1.u32.p434==1))))) + !(AG(AF((i0.u40.p1==1)))))

=> equivalent forward existential formula: [(EY(FwdU((Init * !(!(!(E(TRUE U !(!(EG(!((i0.u40.p1==1)))))))))),TRUE)) * ((i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u18.p117==1)&&(i1.u32.p434==1)))] = FALSE

(forward)formula 1,1,232.804,3686124,1,0,6.26953e+06,144872,6290,2.08868e+07,881,1.2961e+06,1177319

FORMULA DiscoveryGPU-PT-15b-CTLFireability-04 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is TRUE !

***************************************

original formula: !(AF(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)&&(i0.i0.i0.i0.i0.u25.p296!=1))))

=> equivalent forward existential formula: [FwdG(Init,!(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)&&(i0.i0.i0.i0.i0.u25.p296!=1))))] != FALSE

(forward)formula 2,1,521.144,7101472,1,0,1.07529e+07,381881,6351,4.30127e+07,901,3.28795e+06,3155927

FORMULA DiscoveryGPU-PT-15b-CTLFireability-05 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is TRUE !

***************************************

original formula: A(!(EX((i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.p195==1))) U AF(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)||(i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.p61==1))))

=> equivalent forward existential formula: [((Init * !(EG(!(!(EG(!(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)||(i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.p61==1))))))))) * !(E(!(!(EG(!(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)||(i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.p61==1)))))) U (!(!(EX((i0.i0.i0.i0.i0.i0.i0.i0.i0.u21.p195==1)))) * !(!(EG(!(((i0.i0.i0.i0.i0.i0.i0.i0.u22.p227==1)||(i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.i0.u16.p61==1))))))))))] != FALSE

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

Using saturation style SCC detection

(forward)formula 3,0,809.606,7878356,1,0,1.20839e+07,611976,790,4.78694e+07,458,4.92113e+06,2381780

FORMULA DiscoveryGPU-PT-15b-CTLFireability-06 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is FALSE !

***************************************

original formula: AF(EG(((i1.u32.p435!=1)&&(i1.u31.p425==1))))

=> equivalent forward existential formula: [FwdG(Init,!(EG(((i1.u32.p435!=1)&&(i1.u31.p425==1)))))] = FALSE

(forward)formula 4,0,907.136,7878356,1,0,1.20839e+07,714218,1117,4.78694e+07,539,6.29965e+06,4549487

FORMULA DiscoveryGPU-PT-15b-CTLFireability-07 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

Formula is FALSE !

Detected timeout of ITS tools.

[2020-05-22 08:15:44] [INFO ] Flatten gal took : 36 ms

[2020-05-22 08:15:44] [INFO ] Input system was already deterministic with 464 transitions.

[2020-05-22 08:15:44] [INFO ] Transformed 436 places.

[2020-05-22 08:15:44] [INFO ] Transformed 464 transitions.

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/pinvar, /home/mcc/execution/gspn], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/RGMEDD2, /home/mcc/execution/gspn, -META, -varord-only], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Using order generated by GreatSPN with heuristic : META

[2020-05-22 08:15:44] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 5 ms

[2020-05-22 08:15:44] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl, --load-order, /home/mcc/execution/model.ord, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl --load-order /home/mcc/execution/model.ord --gen-order FOLLOW

Successfully loaded order from file /home/mcc/execution/model.ord

No direction supplied, using forward translation only.

Parsed 8 CTL formulae.

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ CTLFireability = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution CTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination CTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DiscoveryGPU-PT-15b"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is DiscoveryGPU-PT-15b, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r066-tajo-158922814800740"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/DiscoveryGPU-PT-15b.tgz

mv DiscoveryGPU-PT-15b execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;