About the Execution of ITS-Tools for SmallOperatingSystem-PT-MT0512DC0256

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15744.750 | 3600000.00 | 3679249.00 | 631.90 | FFFTTTTF??FF??F? | normal |

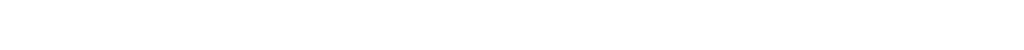

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/local/x2003239/mcc2020-input.r193-csrt-159033388300084.qcow2', fmt=qcow2 size=4294967296 backing_file=/local/x2003239/mcc2020-input.qcow2 encryption=off cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

=====================================================================

Generated by BenchKit 2-4028

Executing tool itstools

Input is SmallOperatingSystem-PT-MT0512DC0256, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r193-csrt-159033388300084

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 208K

-rw-r--r-- 1 mcc users 4.7K Apr 12 17:46 CTLCardinality.txt

-rw-r--r-- 1 mcc users 22K Apr 12 17:46 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.7K Apr 11 20:04 CTLFireability.txt

-rw-r--r-- 1 mcc users 13K Apr 11 20:04 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 24 05:38 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.3K Mar 24 05:38 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 4.1K Apr 14 12:52 LTLCardinality.txt

-rw-r--r-- 1 mcc users 26K Apr 28 14:02 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.4K Apr 14 12:52 LTLFireability.txt

-rw-r--r-- 1 mcc users 15K Apr 28 14:02 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.8K Apr 10 20:34 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 21K Apr 10 20:34 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 3.3K Apr 10 05:24 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 16K Apr 10 05:24 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.1K Apr 10 22:29 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Apr 10 22:29 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Mar 24 05:38 equiv_col

-rw-r--r-- 1 mcc users 13 Mar 24 05:38 instance

-rw-r--r-- 1 mcc users 6 Mar 24 05:38 iscolored

-rw-r--r-- 1 mcc users 8.2K Mar 24 05:38 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-00

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-01

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-02

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-03

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-04

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-05

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-06

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-07

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-08

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-09

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-10

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-11

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-12

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-13

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-14

FORMULA_NAME SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1590471052739

[2020-05-26 05:30:55] [INFO ] Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -greatspnpath, /home/mcc/BenchKit//greatspn/, -order, META, -manyOrder, -smt, -timeout, 3600]

[2020-05-26 05:30:55] [INFO ] Parsing pnml file : /home/mcc/execution/model.pnml

[2020-05-26 05:30:55] [INFO ] Load time of PNML (sax parser for PT used): 26 ms

[2020-05-26 05:30:55] [INFO ] Transformed 9 places.

[2020-05-26 05:30:55] [INFO ] Transformed 8 transitions.

[2020-05-26 05:30:55] [INFO ] Parsed PT model containing 9 places and 8 transitions in 70 ms.

Parsed 16 properties from file /home/mcc/execution/CTLFireability.xml in 15 ms.

Finished random walk after 8472 steps, including 0 resets, run visited all 21 properties in 11 ms. (steps per millisecond=770 )

[2020-05-26 05:30:56] [INFO ] Initial state reduction rules for CTL removed 3 formulas.

[2020-05-26 05:30:56] [INFO ] Flatten gal took : 29 ms

[2020-05-26 05:30:56] [INFO ] Initial state reduction rules for CTL removed 3 formulas.

[2020-05-26 05:30:56] [INFO ] Flatten gal took : 5 ms

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-14 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-11 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-10 FALSE TECHNIQUES TOPOLOGICAL INITIAL_STATE

[2020-05-26 05:30:56] [INFO ] Applying decomposition

[2020-05-26 05:30:56] [INFO ] Flatten gal took : 3 ms

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/convert-linux64, -i, /tmp/graph17158358702383038901.txt, -o, /tmp/graph17158358702383038901.bin, -w, /tmp/graph17158358702383038901.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.202005100927/bin/louvain-linux64, /tmp/graph17158358702383038901.bin, -l, -1, -v, -w, /tmp/graph17158358702383038901.weights, -q, 0, -e, 0.001], workingDir=null]

[2020-05-26 05:30:56] [INFO ] Decomposing Gal with order

[2020-05-26 05:30:56] [INFO ] Rewriting arrays to variables to allow decomposition.

[2020-05-26 05:30:56] [INFO ] Removed a total of 1 redundant transitions.

[2020-05-26 05:30:56] [INFO ] Flatten gal took : 91 ms

[2020-05-26 05:30:56] [INFO ] Fuse similar labels procedure discarded/fused a total of 0 labels/synchronizations in 1 ms.

[2020-05-26 05:30:56] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 1 ms

[2020-05-26 05:30:56] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 2 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 13 CTL formulae.

built 3 ordering constraints for composite.

built 8 ordering constraints for composite.

Detected timeout of ITS tools.

[2020-05-26 05:50:56] [INFO ] Flatten gal took : 3 ms

[2020-05-26 05:50:56] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 20 ms

[2020-05-26 05:50:56] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 5 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl --gen-order FOLLOW

No direction supplied, using forward translation only.

Parsed 13 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,2.45286e+11,133.886,744652,2,68874,5,2.05952e+06,6,0,47,2.15051e+06,0

Converting to forward existential form...Done !

original formula: ((A(((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))||(TransferToDisk>=1)) U ((TaskReady>=1)||(ExecutingTask>=1))) * EF(AG((ExecutingTask>=1)))) * EX(((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))&&((TaskSuspended<1)||(CPUUnit<1)))))

=> equivalent forward existential formula: [(EY((Init * (!((E(!(((TaskReady>=1)||(ExecutingTask>=1))) U (!(((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))||(TransferToDisk>=1))) * !(((TaskReady>=1)||(ExecutingTask>=1))))) + EG(!(((TaskReady>=1)||(ExecutingTask>=1)))))) * E(TRUE U !(E(TRUE U !((ExecutingTask>=1)))))))) * ((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))&&((TaskSuspended<1)||(CPUUnit<1))))] != FALSE

Reverse transition relation is exact ! Faster fixpoint algorithm enabled.

(forward)formula 0,0,276.851,855936,1,0,8,2.05952e+06,22,0,3799,2.15051e+06,6

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-00 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: (!(AF((TaskReady>=1))) * (EX(((LoadingMem>=1)||((TaskSuspended>=1)&&(CPUUnit>=1)))) + AX((TransferToDisk>=1))))

=> equivalent forward existential formula: ([(Init * !(EG(!((TaskReady>=1)))))] = FALSE * [(EY((Init * !(EX(((LoadingMem>=1)||((TaskSuspended>=1)&&(CPUUnit>=1))))))) * !((TransferToDisk>=1)))] = FALSE)

(forward)formula 1,0,361.458,1477368,1,0,16,3.71286e+06,35,5,3819,3.31541e+06,13

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-01 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EG(((TaskReady<1)&&(((TaskOnDisk<1)||(DiskControllerUnit<1))||(TaskSuspended<1))))

=> equivalent forward existential formula: [FwdG(Init,((TaskReady<1)&&(((TaskOnDisk<1)||(DiskControllerUnit<1))||(TaskSuspended<1))))] != FALSE

Hit Full ! (commute/partial/dont) 0/2/8

(forward)formula 2,0,362.102,1490564,1,0,18,3.7876e+06,43,6,3845,3.32334e+06,17

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-02 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: E(((ExecutingTask>=1)&&((TransferToDisk<1)||(LoadingMem<1))) U ((TaskReady>=1) + AF((TaskReady>=1))))

=> equivalent forward existential formula: ([(FwdU(Init,((ExecutingTask>=1)&&((TransferToDisk<1)||(LoadingMem<1)))) * (TaskReady>=1))] != FALSE + [(FwdU(Init,((ExecutingTask>=1)&&((TransferToDisk<1)||(LoadingMem<1)))) * !(EG(!((TaskReady>=1)))))] != FALSE)

Hit Full ! (commute/partial/dont) 1/4/7

(forward)formula 3,1,362.165,1494524,1,0,21,3.78786e+06,50,7,3864,3.32361e+06,21

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-03 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: AF(((TaskReady>=1)&&(CPUUnit>=1)))

=> equivalent forward existential formula: [FwdG(Init,!(((TaskReady>=1)&&(CPUUnit>=1))))] = FALSE

Hit Full ! (commute/partial/dont) 2/0/6

(forward)formula 4,1,362.282,1497692,1,0,21,3.78786e+06,58,8,3880,3.32361e+06,24

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-04 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: AG((EF((((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))&&(TaskSuspended>=1))&&(CPUUnit>=1))) + (ExecutingTask>=1)))

=> equivalent forward existential formula: [((FwdU(Init,TRUE) * !((ExecutingTask>=1))) * !(E(TRUE U (((((TaskOnDisk>=1)&&(FreeMemSegment>=1))&&(DiskControllerUnit>=1))&&(TaskSuspended>=1))&&(CPUUnit>=1)))))] = FALSE

(forward)formula 5,1,367.877,1558676,1,0,22,4.12579e+06,59,8,3883,3.56233e+06,27

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-05 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: E(AF(((ExecutingTask>=1)||((TaskReady>=1)&&(CPUUnit>=1)))) U (((TaskOnDisk>=1)&&(DiskControllerUnit>=1))&&(TaskSuspended>=1)))

=> equivalent forward existential formula: [(FwdU(Init,!(EG(!(((ExecutingTask>=1)||((TaskReady>=1)&&(CPUUnit>=1))))))) * (((TaskOnDisk>=1)&&(DiskControllerUnit>=1))&&(TaskSuspended>=1)))] != FALSE

(forward)formula 6,1,528.861,2519804,1,0,25,6.40737e+06,10,8,3715,5.60724e+06,2

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-06 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: !(AF(((TaskReady>=1)&&(CPUUnit>=1))))

=> equivalent forward existential formula: [FwdG(Init,!(((TaskReady>=1)&&(CPUUnit>=1))))] != FALSE

Hit Full ! (commute/partial/dont) 2/0/6

(forward)formula 7,0,529.198,2519804,1,0,25,6.40737e+06,20,8,3739,5.60724e+06,6

FORMULA SmallOperatingSystem-PT-MT0512DC0256-CTLFireability-07 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: (E(((((TaskOnDisk<1)||(DiskControllerUnit<1))||(TaskSuspended<1))||(TransferToDisk>=1)) U AX(((TaskSuspended>=1)&&(CPUUnit>=1)))) * !(A((TransferToDisk>=1) U ((TaskSuspended>=1)&&(CPUUnit>=1)))))

=> equivalent forward existential formula: ([(FwdU((Init * E(((((TaskOnDisk<1)||(DiskControllerUnit<1))||(TaskSuspended<1))||(TransferToDisk>=1)) U !(EX(!(((TaskSuspended>=1)&&(CPUUnit>=1))))))),!(((TaskSuspended>=1)&&(CPUUnit>=1)))) * (!((TransferToDisk>=1)) * !(((TaskSuspended>=1)&&(CPUUnit>=1)))))] != FALSE + [FwdG((Init * E(((((TaskOnDisk<1)||(DiskControllerUnit<1))||(TaskSuspended<1))||(TransferToDisk>=1)) U !(EX(!(((TaskSuspended>=1)&&(CPUUnit>=1))))))),!(((TaskSuspended>=1)&&(CPUUnit>=1))))] != FALSE)

Hit Full ! (commute/partial/dont) 2/0/6

Hit Full ! (commute/partial/dont) 4/0/4

Detected timeout of ITS tools.

[2020-05-26 06:10:56] [INFO ] Flatten gal took : 3 ms

[2020-05-26 06:10:56] [INFO ] Input system was already deterministic with 8 transitions.

[2020-05-26 06:10:56] [INFO ] Transformed 9 places.

[2020-05-26 06:10:56] [INFO ] Transformed 8 transitions.

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/pinvar, /home/mcc/execution/gspn], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Running greatSPN : CommandLine [args=[/home/mcc/BenchKit//greatspn//bin/RGMEDD2, /home/mcc/execution/gspn, -META, -varord-only], workingDir=/home/mcc/execution]

Run of greatSPN captured in /home/mcc/execution/outPut.txt

Using order generated by GreatSPN with heuristic : META

[2020-05-26 06:10:56] [INFO ] Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 2 ms

[2020-05-26 06:10:56] [INFO ] Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 1 ms

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl, --load-order, /home/mcc/execution/model.ord, --gen-order, FOLLOW], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.202005100927/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl --load-order /home/mcc/execution/model.ord --gen-order FOLLOW

Successfully loaded order from file /home/mcc/execution/model.ord

No direction supplied, using forward translation only.

Parsed 5 CTL formulae.

BK_TIME_CONFINEMENT_REACHED

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ CTLFireability = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution CTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination CTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -greatspnpath /home/mcc/BenchKit//greatspn/ -order META -manyOrder -smt -timeout 3600 -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss128m -Xms40m -Xmx16000m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="SmallOperatingSystem-PT-MT0512DC0256"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-4028"

echo " Executing tool itstools"

echo " Input is SmallOperatingSystem-PT-MT0512DC0256, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r193-csrt-159033388300084"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/SmallOperatingSystem-PT-MT0512DC0256.tgz

mv SmallOperatingSystem-PT-MT0512DC0256 execution

cd execution

if [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "UpperBounds" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] || [ "CTLFireability" = "StateSpace" ]; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

elif [ "CTLFireability" = "ReachabilityDeadlock" ] || [ "CTLFireability" = "QuasiLiveness" ] || [ "CTLFireability" = "StableMarking" ] || [ "CTLFireability" = "Liveness" ] || [ "CTLFireability" = "OneSafe" ] ; then

echo "FORMULA_NAME CTLFireability"

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;