About the Execution of ITS-Tools for ASLink-PT-01b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 1295.620 | 36643.00 | 81450.00 | 369.90 | T | normal |

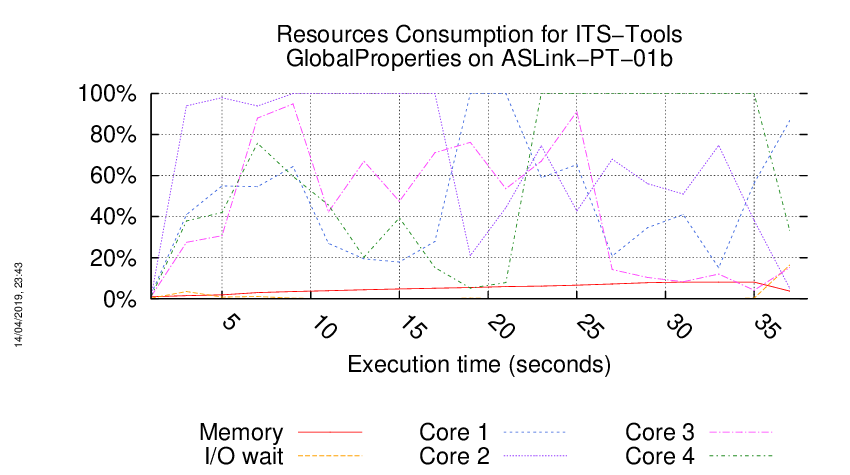

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fkordon/mcc2019-input.r008-smll-155225013900021.qcow2', fmt=qcow2 size=4294967296 backing_file='/data/fkordon/mcc2019-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

...................

=====================================================================

Generated by BenchKit 2-3817

Executing tool itstools

Input is ASLink-PT-01b, examination is GlobalProperties

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r008-smll-155225013900021

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 448K

-rw-r--r-- 1 mcc users 3.1K Feb 9 05:48 CTLCardinality.txt

-rw-r--r-- 1 mcc users 17K Feb 9 05:48 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K Feb 5 01:59 CTLFireability.txt

-rw-r--r-- 1 mcc users 18K Feb 5 01:59 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 10 17:31 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 100 Feb 24 15:05 GlobalProperties.txt

-rw-r--r-- 1 mcc users 338 Feb 24 15:05 GlobalProperties.xml

-rw-r--r-- 1 mcc users 2.4K Feb 4 22:50 LTLCardinality.txt

-rw-r--r-- 1 mcc users 12K Feb 4 22:50 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.7K Feb 4 22:31 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.0K Feb 4 22:31 LTLFireability.xml

-rw-r--r-- 1 mcc users 2.9K Feb 1 23:27 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 14K Feb 1 23:27 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.8K Jan 29 09:53 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K Jan 29 09:53 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K Feb 4 22:17 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K Feb 4 22:17 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Jan 29 09:34 equiv_col

-rw-r--r-- 1 mcc users 4 Jan 29 09:34 instance

-rw-r--r-- 1 mcc users 6 Jan 29 09:34 iscolored

-rw-r--r-- 1 mcc users 293K Mar 10 17:31 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ASLink-PT-01b-GlobalProperties-0

=== Now, execution of the tool begins

BK_START 1552431576466

Working with output stream class java.io.PrintStream

Flatten gal took : 453 ms

Constant places removed 1 places and 1 transitions.

Performed 352 Post agglomeration using F-continuation condition.

Iterating post reduction 0 with 353 rules applied. Total rules applied 353 place count 845 transition count 795

Constant places removed 371 places and 2 transitions.

Reduce isomorphic transitions removed 7 transitions.

Implicit places reduction removed 2 places :[p575, p447]

Performed 17 Post agglomeration using F-continuation condition.

Iterating post reduction 1 with 397 rules applied. Total rules applied 750 place count 472 transition count 769

Constant places removed 19 places and 0 transitions.

Performed 5 Post agglomeration using F-continuation condition.

Iterating post reduction 2 with 24 rules applied. Total rules applied 774 place count 453 transition count 764

Constant places removed 5 places and 0 transitions.

Implicit places reduction removed 1 places :[p402]

Performed 1 Post agglomeration using F-continuation condition.

Iterating post reduction 3 with 7 rules applied. Total rules applied 781 place count 447 transition count 763

Constant places removed 1 places and 0 transitions.

Iterating post reduction 4 with 1 rules applied. Total rules applied 782 place count 446 transition count 763

Performed 77 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 5 with 77 Pre rules applied. Total rules applied 782 place count 446 transition count 686

Constant places removed 78 places and 0 transitions.

Implicit places reduction removed 1 places :[p416]

Performed 1 Post agglomeration using F-continuation condition.

Iterating post reduction 5 with 80 rules applied. Total rules applied 862 place count 367 transition count 685

Constant places removed 1 places and 0 transitions.

Iterating post reduction 6 with 1 rules applied. Total rules applied 863 place count 366 transition count 685

Performed 1 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 7 with 1 Pre rules applied. Total rules applied 863 place count 366 transition count 684

Constant places removed 1 places and 0 transitions.

Iterating post reduction 7 with 1 rules applied. Total rules applied 864 place count 365 transition count 684

Symmetric choice reduction at 8 with 8 rule applications. Total rules 872 place count 365 transition count 684

Constant places removed 8 places and 8 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 1 places :[p845]

Performed 4 Post agglomeration using F-continuation condition.

Iterating post reduction 8 with 14 rules applied. Total rules applied 886 place count 356 transition count 671

Constant places removed 5 places and 0 transitions.

Iterating post reduction 9 with 5 rules applied. Total rules applied 891 place count 351 transition count 671

Symmetric choice reduction at 10 with 4 rule applications. Total rules 895 place count 351 transition count 671

Constant places removed 4 places and 17 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 2 places :[p584, p388]

Performed 5 Post agglomeration using F-continuation condition.

Iterating post reduction 10 with 12 rules applied. Total rules applied 907 place count 345 transition count 648

Constant places removed 5 places and 0 transitions.

Iterating post reduction 11 with 5 rules applied. Total rules applied 912 place count 340 transition count 648

Symmetric choice reduction at 12 with 2 rule applications. Total rules 914 place count 340 transition count 648

Constant places removed 2 places and 9 transitions.

Iterating post reduction 12 with 2 rules applied. Total rules applied 916 place count 338 transition count 639

Symmetric choice reduction at 13 with 1 rule applications. Total rules 917 place count 338 transition count 639

Constant places removed 1 places and 8 transitions.

Iterating post reduction 13 with 1 rules applied. Total rules applied 918 place count 337 transition count 631

Symmetric choice reduction at 14 with 1 rule applications. Total rules 919 place count 337 transition count 631

Constant places removed 1 places and 8 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 920 place count 336 transition count 623

Symmetric choice reduction at 15 with 1 rule applications. Total rules 921 place count 336 transition count 623

Constant places removed 1 places and 8 transitions.

Iterating post reduction 15 with 1 rules applied. Total rules applied 922 place count 335 transition count 615

Symmetric choice reduction at 16 with 1 rule applications. Total rules 923 place count 335 transition count 615

Constant places removed 1 places and 8 transitions.

Iterating post reduction 16 with 1 rules applied. Total rules applied 924 place count 334 transition count 607

Symmetric choice reduction at 17 with 1 rule applications. Total rules 925 place count 334 transition count 607

Constant places removed 1 places and 8 transitions.

Iterating post reduction 17 with 1 rules applied. Total rules applied 926 place count 333 transition count 599

Symmetric choice reduction at 18 with 1 rule applications. Total rules 927 place count 333 transition count 599

Constant places removed 1 places and 8 transitions.

Iterating post reduction 18 with 1 rules applied. Total rules applied 928 place count 332 transition count 591

Symmetric choice reduction at 19 with 1 rule applications. Total rules 929 place count 332 transition count 591

Constant places removed 1 places and 8 transitions.

Iterating post reduction 19 with 1 rules applied. Total rules applied 930 place count 331 transition count 583

Symmetric choice reduction at 20 with 1 rule applications. Total rules 931 place count 331 transition count 583

Constant places removed 1 places and 8 transitions.

Iterating post reduction 20 with 1 rules applied. Total rules applied 932 place count 330 transition count 575

Symmetric choice reduction at 21 with 1 rule applications. Total rules 933 place count 330 transition count 575

Constant places removed 1 places and 8 transitions.

Iterating post reduction 21 with 1 rules applied. Total rules applied 934 place count 329 transition count 567

Symmetric choice reduction at 22 with 1 rule applications. Total rules 935 place count 329 transition count 567

Constant places removed 1 places and 8 transitions.

Iterating post reduction 22 with 1 rules applied. Total rules applied 936 place count 328 transition count 559

Symmetric choice reduction at 23 with 1 rule applications. Total rules 937 place count 328 transition count 559

Constant places removed 1 places and 8 transitions.

Iterating post reduction 23 with 1 rules applied. Total rules applied 938 place count 327 transition count 551

Symmetric choice reduction at 24 with 1 rule applications. Total rules 939 place count 327 transition count 551

Constant places removed 1 places and 8 transitions.

Iterating post reduction 24 with 1 rules applied. Total rules applied 940 place count 326 transition count 543

Symmetric choice reduction at 25 with 1 rule applications. Total rules 941 place count 326 transition count 543

Constant places removed 1 places and 8 transitions.

Iterating post reduction 25 with 1 rules applied. Total rules applied 942 place count 325 transition count 535

Symmetric choice reduction at 26 with 1 rule applications. Total rules 943 place count 325 transition count 535

Constant places removed 1 places and 8 transitions.

Iterating post reduction 26 with 1 rules applied. Total rules applied 944 place count 324 transition count 527

Symmetric choice reduction at 27 with 1 rule applications. Total rules 945 place count 324 transition count 527

Constant places removed 1 places and 8 transitions.

Iterating post reduction 27 with 1 rules applied. Total rules applied 946 place count 323 transition count 519

Performed 19 Post agglomeration using F-continuation condition.

Constant places removed 19 places and 0 transitions.

Iterating post reduction 28 with 19 rules applied. Total rules applied 965 place count 304 transition count 499

Performed 1 Post agglomeration using F-continuation condition.

Constant places removed 1 places and 0 transitions.

Iterating post reduction 29 with 1 rules applied. Total rules applied 966 place count 303 transition count 508

Applied a total of 966 rules in 461 ms. Remains 303 /846 variables (removed 543) and now considering 508/1148 (removed 640) transitions.

// Phase 1: matrix 508 rows 303 cols

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903111103/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/GlobalProperties.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903111103/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/GlobalProperties.pnml.gal -t CGAL -ctl DEADLOCK

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 508 rows 303 cols

invariant :p95 + p99 + p103 + p107 + p111 + p115 + p119 + p123 + p479 + p482 + p485 + p488 + p491 + p494 + p497 + p500 + p503 + -1'p594 + -1'p597 + -1'p600 + -1'p603 + -1'p782 + -1'p790 + -1'p798 + -1'p828 + -1'p836 = 0

invariant :-1'p682 + -1'p683 + -1'p684 + p689 + p690 + p691 = 0

invariant :-1'p736 + -1'p737 + -1'p738 + p740 + p741 + p742 = 0

invariant :p130 + p133 + p136 + p139 + p142 + p145 + p148 + p151 + p228 + p289 + p326 + p360 + p421 + p423 = 1

invariant :p531 + p680 + p691 + p699 + p707 + p715 + p723 + p734 + p742 + p750 + p761 + p769 = 1

invariant :p573 + -1'p778 + -1'p786 + -1'p794 + -1'p832 = 0

invariant :p744 + p745 + p746 + -1'p748 + -1'p749 + -1'p750 = 0

invariant :p772 + p773 + -1'p780 + -1'p781 + -1'p782 = 0

invariant :p314 + p318 + p320 + p321 + p323 + p326 + p328 + -1'p329 + -1'p330 + -1'p331 = 0

invariant :p51 + p55 + p60 + p62 + p63 + p65 + p67 + p68 + p70 + p72 + p421 = 1

invariant :p225 + p228 + p230 + -1'p231 + -1'p232 + -1'p236 + -1'p237 + -1'p241 + -1'p242 + -1'p245 + -1'p246 + -1'p250 + -1'p251 + p294 + p331 + p365 + p470 = 1

invariant :p534 + p541 + -1'p672 + p679 + -1'p683 + p690 + -1'p694 + p698 + -1'p702 + p706 + -1'p710 + p714 + p717 + p719 + -1'p721 + -1'p723 + -1'p726 + p733 + -1'p737 + p741 + p744 + p746 + -1'p748 + -1'p750 + -1'p753 + p760 + p763 + p765 + -1'p767 + -1'p769 = 0

invariant :p543 + -1'p684 + -1'p695 + -1'p703 + -1'p711 + -1'p727 + -1'p738 + -1'p754 = 0

invariant :p126 + p275 + p278 + p281 + p284 + p318 + p321 + p355 = 1

invariant :p8 + p12 + p16 + p20 + p24 + p28 + p32 + p36 + p40 + p55 + p63 + p68 + p72 + p159 + p162 + p165 + p168 + p171 + p174 + p177 + p180 = 1

invariant :p11 + p15 + p19 + p23 + p27 + p31 + p35 + p39 + -1'p159 + -1'p162 + -1'p165 + -1'p168 + -1'p171 + -1'p174 + -1'p177 + -1'p180 = 0

invariant :p154 + p212 = 1

invariant :p233 + p294 + p331 + p365 + p470 = 1

invariant :p87 + p219 + p220 + p231 + p232 + p236 + p241 + p245 + p250 + p292 + p293 + p329 + p330 + p363 + p364 + p394 + -1'p470 = 0

invariant :-1'p701 + -1'p702 + -1'p703 + p705 + p706 + p707 = 0

invariant :p776 + p777 + p778 + -1'p780 + -1'p781 + -1'p782 = 0

invariant :p47 + p51 + p55 + p60 + p67 + p68 + p70 + p72 + p421 = 1

invariant :-1'p693 + -1'p694 + -1'p695 + p697 + p698 + p699 = 0

invariant :p537 + p538 + p544 + p546 + p547 + p549 + p550 + p552 + p553 + p555 + p556 + p558 + p559 + p561 + p562 + p564 + p565 + p567 + p568 + p672 + p673 + -1'p679 + -1'p680 + p683 + p684 + -1'p690 + -1'p691 + p694 + p695 + -1'p698 + -1'p699 + p702 + p703 + -1'p706 + -1'p707 + p710 + p711 + -1'p714 + -1'p715 + -1'p717 + p721 + p726 + p727 + -1'p733 + -1'p734 + p737 + p738 + -1'p741 + -1'p742 + -1'p744 + p748 + p753 + p754 + -1'p760 + -1'p761 + -1'p763 + p767 = 0

invariant :p130 + p133 + p136 + p139 + p142 + p145 + p148 + p151 + p421 + p423 + p438 + p440 + p441 = 1

invariant :p157 + p159 + p160 + p162 + p163 + p165 + p166 + p168 + p169 + p171 + p172 + p174 + p175 + p177 + p178 + p180 + p181 + -1'p212 = 0

invariant :p784 + p785 + p786 + -1'p788 + -1'p789 + -1'p790 = 0

invariant :-1'p752 + -1'p753 + -1'p754 + p759 + p760 + p761 = 0

invariant :p469 + p470 = 1

invariant :p128 + p130 + p132 + p133 + p135 + p136 + p138 + p139 + p141 + p142 + p144 + p145 + p147 + p148 + p150 + p151 + p153 + -1'p275 + -1'p278 + -1'p281 + -1'p284 + -1'p318 + -1'p321 + -1'p355 = 0

invariant :-1'p130 + -1'p133 + -1'p136 + -1'p139 + -1'p142 + -1'p145 + -1'p148 + -1'p151 + -1'p428 + p432 + p435 + -1'p440 + p537 + -1'p541 + p546 + p549 + p552 + p555 + p558 + p561 + p564 + p567 + p672 + p673 + -1'p679 + p683 + -1'p690 + p694 + -1'p698 + p702 + -1'p706 + p710 + -1'p714 + -1'p717 + p721 + p723 + p726 + -1'p733 + p737 + -1'p741 + -1'p744 + p748 + p750 + p753 + -1'p760 + -1'p763 + p767 + p769 = 0

invariant :p49 + -1'p51 + -1'p55 + -1'p60 + -1'p67 + -1'p68 + -1'p70 + -1'p72 + -1'p421 = 0

invariant :-1'p709 + -1'p710 + -1'p711 + p713 + p714 + p715 = 0

invariant :p717 + p718 + p719 + -1'p721 + -1'p722 + -1'p723 = 0

invariant :p792 + p793 + p794 + -1'p796 + -1'p797 + -1'p798 = 0

invariant :p428 + p434 + p440 + -1'p537 + p541 + -1'p546 + -1'p549 + -1'p552 + -1'p555 + -1'p558 + -1'p561 + -1'p564 + -1'p567 + -1'p672 + -1'p673 + p679 + -1'p683 + p690 + -1'p694 + p698 + -1'p702 + p706 + -1'p710 + p714 + p717 + -1'p721 + -1'p723 + -1'p726 + p733 + -1'p737 + p741 + p744 + -1'p748 + -1'p750 + -1'p753 + p760 + p763 + -1'p767 + -1'p769 = 0

invariant :p410 + p421 = 1

invariant :p586 + p594 + p596 + p597 + p599 + p600 + p602 + p603 + p605 = 1

invariant :p7 + -1'p55 + -1'p63 + -1'p68 + -1'p72 = 0

invariant :-1'p671 + -1'p672 + -1'p673 + p678 + p679 + p680 = 0

invariant :p577 + p778 + p786 + p794 + p832 = 1

invariant :p92 + p95 + p96 + p99 + p100 + p103 + p104 + p107 + p108 + p111 + p112 + p115 + p116 + p119 + p120 + p123 + p124 + -1'p219 + -1'p220 + -1'p231 + -1'p232 + -1'p236 + -1'p241 + -1'p245 + -1'p250 + -1'p292 + -1'p293 + -1'p329 + -1'p330 + -1'p363 + -1'p364 + -1'p394 + p470 = 1

invariant :p594 + p596 + p597 + p599 + p600 + p602 + p603 + p605 + p606 + p667 + p671 + p672 + p673 + p682 + p683 + p684 + p693 + p694 + p695 + p701 + p702 + p703 + p709 + p710 + p711 + p721 + p722 + p723 + p725 + p726 + p727 + p736 + p737 + p738 + p748 + p749 + p750 + p752 + p753 + p754 + p767 + p768 + p769 + p780 + p781 + p782 + p788 + p789 + p790 + p796 + p797 + p798 + p826 + p827 + p828 + p834 + p835 + p836 = 1

invariant :-1'p725 + -1'p726 + -1'p727 + p732 + p733 + p734 = 0

invariant :-1'p130 + -1'p133 + -1'p136 + -1'p139 + -1'p142 + -1'p145 + -1'p148 + -1'p151 + -1'p228 + p271 + p275 + p277 + p278 + p280 + p281 + p283 + p284 + p286 + p291 + -1'p292 + -1'p293 + -1'p294 + -1'p326 + -1'p360 + -1'p421 + -1'p423 = -1

invariant :p536 + -1'p673 + -1'p719 + -1'p746 + -1'p765 = 0

invariant :p763 + p764 + p765 + -1'p767 + -1'p768 + -1'p769 = 0

invariant :p830 + p831 + p832 + -1'p834 + -1'p835 + -1'p836 = 0

invariant :p209 + p212 + p214 + p219 + p220 + p231 + p232 + p236 + p237 + p241 + p242 + p245 + p246 + p250 + p251 + p292 + p293 + p329 + p330 + p363 + p364 + p394 + p400 + -1'p470 = 0

invariant :-1'p421 + p426 + p428 + p429 = 0

invariant :p810 + p818 + -1'p826 + -1'p827 + -1'p828 = 0

invariant :p351 + p355 + p357 + p360 + p362 + -1'p363 + -1'p364 + -1'p365 = 0

invariant :p476 + p594 + p597 + p600 + p603 + p782 + p790 + p798 + p828 + p836 = 1

invariant :-1'p95 + -1'p99 + -1'p103 + -1'p107 + -1'p111 + -1'p115 + -1'p119 + -1'p123 + p481 + p484 + p487 + p490 + p493 + p496 + p499 + p502 = 0

No direction supplied, using forward translation only.

built 3 ordering constraints for composite.

built 174 ordering constraints for composite.

built 33 ordering constraints for composite.

built 21 ordering constraints for composite.

built 141 ordering constraints for composite.

built 138 ordering constraints for composite.

built 190 ordering constraints for composite.

built 49 ordering constraints for composite.

built 46 ordering constraints for composite.

built 43 ordering constraints for composite.

built 141 ordering constraints for composite.

built 7 ordering constraints for composite.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,7.88726e+06,27.7722,712588,7357,577,1.21228e+06,3030,1486,4.61539e+06,147,17663,0

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

dead,13280,28.6557,712588,835,250,1.21228e+06,6472,3959,4.61539e+06,634,17663,111686

System contains 13280 deadlocks (shown below if less than --print-limit option) !

FORMULA ASLink-PT-01b-GlobalProperties-0 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

[ 13280 states ] showing 10 first states

[ i1={[ i1={[ u134={[ ]

} u100={[ ]

} u99={[ ]

} u98={[ ]

} u97={[ ]

} u92={[ ]

} u91={[ ]

} u90={[ ]

} u89={[ ]

} u88={[ ]

} u84={[ p769=1 ]

} u83={[ p763=1 ]

} u82={[ ]

} u81={[ ]

} u80={[ ]

} u79={[ ]

} u78={[ ]

} u77={[ ]

} u76={[ ]

} u75={[ ]

} u74={[ ]

} u73={[ ]

} u72={[ ]

} u71={[ ]

} u70={[ ]

} u69={[ ]

} u68={[ ]

} u67={[ ]

} u66={[ ]

} u65={[ ]

} u64={[ ]

} u63={[ ]

} i22={[ u87={[ ]

} u86={[ ]

} ]

} ]

[ u134={[ ]

} u100={[ ]

} u99={[ ]

} u98={[ ]

} u97={[ ]

} u92={[ ]

} u91={[ ]

} u90={[ ]

} u89={[ ]

} u88={[ ]

} u84={[ ]

} u83={[ ]

} u82={[ ]

} u81={[ ]

} u80={[ p750=1 ]

} u79={[ p744=1 ]

} u78={[ ]

} u77={[ ]

} u76={[ ]

} u75={[ ]

} u74={[ ]

} u73={[ ]

} u72={[ ]

} u71={[ ]

} u70={[ ]

} u69={[ ]

} u68={[ ]

} u67={[ ]

} u66={[ ]

} u65={[ ]

} u64={[ ]

} u63={[ ]

} i22={[ u87={[ ]

} u86={[ ]

} ]

} ]

[ u134={[ ]

} u100={[ ]

} u99={[ ]

} u98={[ ]

} u97={[ ]

} u92={[ ]

} u91={[ ]

} u90={[ ]

} u89={[ ]

} u88={[ ]

} u84={[ ]

} u83={[ ]

} u82={[ ]

} u81={[ ]

} u80={[ ]

} u79={[ ]

} u78={[ ]

} u77={[ ]

} u76={[ ]

} u75={[ ]

} u74={[ p723=1 ]

} u73={[ p717=1 ]

} u72={[ ]

} u71={[ ]

} u70={[ ]

} u69={[ ]

} u68={[ ]

} u67={[ ]

} u66={[ ]

} u65={[ ]

} u64={[ ]

} u63={[ ]

} i22={[ u87={[ ]

} u86={[ ]

} ]

} ]

} i0={[ u61={[ p586=1 ]

} i0={[ u60={[ p577=1 ]

} i0={[ u59={[ p544=1 ]

} u58={[ p476=1 ]

} ]

} ]

} ]

} ]

} i0={[ i1={[ u53={[ p470=1 ]

} i0={[ u129={[ p410=1 ]

} u128={[ ]

} u126={[ ]

} u123={[ ]

} u121={[ ]

} u115={[ p219=1 ]

} u50={[ p423=1 ]

} u49={[ ]

} u44={[ ]

} u37={[ ]

} u31={[ ]

} u25={[ ]

} u19={[ ]

} u17={[ p154=1 ]

} u16={[ p126=1 ]

} u15={[ p124=1 ]

} ]

[ u129={[ p410=1 ]

} u128={[ ]

} u126={[ ]

} u123={[ ]

} u121={[ ]

} u115={[ ]

} u50={[ p423=1 ]

} u49={[ ]

} u44={[ p394=1 ]

} u37={[ ]

} u31={[ ]

} u25={[ ]

} u19={[ ]

} u17={[ p154=1 ]

} u16={[ p126=1 ]

} u15={[ p124=1 ]

} ]

[ u129={[ p410=1 ]

} u128={[ ]

} u126={[ ]

} u123={[ ]

} u121={[ p231=1 ]

[ p250=1 ]

} u115={[ ]

} u50={[ p423=1 ]

} u49={[ ]

} u44={[ ]

} u37={[ ]

} u31={[ ]

} u25={[ ]

} u19={[ p225=1 ]

} u17={[ p154=1 ]

} u16={[ p126=1 ]

} u15={[ p124=1 ]

} ]

} ]

} i0={[ u6={[ p65=1 ]

} i0={[ u5={[ p47=1 ]

} u4={[ p40=1 ]

} ]

} ]

[ u6={[ p51=1 ]

[ p70=1 ]

} i0={[ u5={[ p49=1 ]

} u4={[ p40=1 ]

} ]

} ]

} ]

} ]

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/home/mcc/execution]

WARNING : LTS min runner thread was asked to interrupt. Dying gracefully.

BK_STOP 1552431613109

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ GlobalProperties = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution GlobalProperties -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination GlobalProperties -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Mar 12, 2019 10:59:39 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, GlobalProperties, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

Mar 12, 2019 10:59:39 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Mar 12, 2019 10:59:39 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 263 ms

Mar 12, 2019 10:59:39 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 846 places.

Mar 12, 2019 10:59:40 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1148 transitions.

Mar 12, 2019 10:59:40 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

Mar 12, 2019 10:59:40 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 59 ms

Mar 12, 2019 10:59:40 PM fr.lip6.move.gal.instantiate.PropertySimplifier evalInInitialState

WARNING: Unexpected boolean logic operator in evalInInitialState fr.lip6.move.gal.impl.EXImpl

Mar 12, 2019 10:59:40 PM fr.lip6.move.gal.instantiate.PropertySimplifier rewriteWithInitialState

INFO: Reachable property ASLink-PT-01b-GlobalProperties-0 is trivially true : it is verified in initial state.

Mar 12, 2019 10:59:40 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 446 ms

Mar 12, 2019 10:59:40 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.simple.gal : 9 ms

Mar 12, 2019 10:59:41 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 1148 transitions.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.PropertySimplifier rewriteWithInitialState

INFO: Reachable property ASLink-PT-01b-GlobalProperties-0 is trivially true : it is verified in initial state.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 113 ms

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.PropertySimplifier rewriteWithInitialState

INFO: Reachable property ASLink-PT-01b-GlobalProperties-0 is trivially true : it is verified in initial state.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 96 ms

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 508 transitions.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1023.t139.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1028.t136.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 12 events :t1100.t399,t1100.t399,t1100.t399,t1100.t399,t1100.t399,t1100.t399,t1099.t348,t1099.t348,t1099.t348,t1099.t348,t1099.t348,t1099.t348,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t16.t130.t526.t131.t525.t132,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 4 events :t22.t90.t47,t22.t90.t47,t22.t90.t47,t22.t90.t47,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1007.t114.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1050.t158.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 71 events :t186.t239.t706,t186.t242.t705,t186.t245.t704,t240.t1078.t375.t501.t244,t240.t1078.t375.t501.t244,t240.t1078.t375.t501.t244,t240.t1078.t375.t501.t244,t240.t1078.t375.t501.t244,t240.t1078.t375.t501.t244,t243.t1063.t244,t243.t1063.t244,t243.t1063.t244,t243.t1063.t244,t243.t1063.t244,t243.t1063.t244,t243.t1063.t244,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t186.t239.t706,t186.t242.t705,t186.t245.t704,t1082.t374,t1082.t374,t1082.t374,t1070.t397,t1070.t397,t1070.t397,t1070.t397,t1070.t397,t1070.t397,t1070.t397,t661,t660,t659,t661,t660,t659,t661,t660,t659,t661,t660,t659,t661,t660,t659,t661,t660,t659,t661,t660,t659,t661,t660,t659,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1142.t440.t427,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1019.t133.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1024.t142.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 122 events :t1114,t1114,t1086.t421,t1086.t421,t1086.t421,t1086.t421,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t211.t402.t403.t968,t211.t404.t405.t967,t211.t406.t407.t966,t211.t408.t409.t965,t211.t410.t411.t964,t211.t412.t413.t963,t211.t414.t415.t962,t211.t416.t417.t961,t1114,t1114,t1114,t1114,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,t848,t847,t846,t845,t844,t843,t842,t841,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 112 events :t379.t460.t461.t539,t379.t460.t461.t539,t379.t460.t461.t539,t379.t460.t461.t539,t379.t460.t461.t539,t379.t460.t461.t539,t379.t460.t461.t539,t380.t460.t461.t555,t380.t460.t461.t555,t380.t460.t461.t555,t380.t460.t461.t555,t380.t460.t461.t555,t380.t460.t461.t555,t380.t460.t461.t555,t381.t460.t461.t571,t381.t460.t461.t571,t381.t460.t461.t571,t381.t460.t461.t571,t381.t460.t461.t571,t381.t460.t461.t571,t381.t460.t461.t571,t382.t460.t461.t587,t382.t460.t461.t587,t382.t460.t461.t587,t382.t460.t461.t587,t382.t460.t461.t587,t382.t460.t461.t587,t382.t460.t461.t587,t383.t460.t461.t603,t383.t460.t461.t603,t383.t460.t461.t603,t383.t460.t461.t603,t383.t460.t461.t603,t383.t460.t461.t603,t383.t460.t461.t603,t384.t460.t461.t619,t384.t460.t461.t619,t384.t460.t461.t619,t384.t460.t461.t619,t384.t460.t461.t619,t384.t460.t461.t619,t384.t460.t461.t619,t385.t460.t461.t635,t385.t460.t461.t635,t385.t460.t461.t635,t385.t460.t461.t635,t385.t460.t461.t635,t385.t460.t461.t635,t385.t460.t461.t635,t386.t460.t461.t651,t386.t460.t461.t651,t386.t460.t461.t651,t386.t460.t461.t651,t386.t460.t461.t651,t386.t460.t461.t651,t386.t460.t461.t651,t643,t643,t643,t643,t643,t643,t643,t627,t627,t627,t627,t627,t627,t627,t611,t611,t611,t611,t611,t611,t611,t595,t595,t595,t595,t595,t595,t595,t579,t579,t579,t579,t579,t579,t579,t563,t563,t563,t563,t563,t563,t563,t547,t547,t547,t547,t547,t547,t547,t531,t531,t531,t531,t531,t531,t531,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 6 events :t175.t970.t176,t175.t970.t176,t175.t970.t176,t969.t88,t969.t88,t969.t88,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t1012.t109.t178,t19.t111.t520.t112.t519.t113,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1008.t117.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t21.t95.t514.t96.t513.t97,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 14 events :t126.t127,t126.t127,t126.t127,t126.t127,t126.t127,t11.t161.t162,t11.t161.t162,t11.t161.t162,t11.t161.t162,t11.t161.t162,t11.t161.t162,t11.t161.t162,t126.t127,t126.t127,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 128 events :t212.t973.t213,t212.t973.t213,t212.t973.t213,t212.t973.t213,t212.t973.t213,t212.t973.t213,t212.t973.t213,t212.t973.t213,t204.t416.t417.t849,t204.t416.t417.t849,t204.t416.t417.t849,t204.t416.t417.t849,t204.t416.t417.t849,t204.t416.t417.t849,t204.t416.t417.t849,t205.t416.t417.t865,t205.t416.t417.t865,t205.t416.t417.t865,t205.t416.t417.t865,t205.t416.t417.t865,t205.t416.t417.t865,t205.t416.t417.t865,t206.t416.t417.t881,t206.t416.t417.t881,t206.t416.t417.t881,t206.t416.t417.t881,t206.t416.t417.t881,t206.t416.t417.t881,t206.t416.t417.t881,t207.t416.t417.t897,t207.t416.t417.t897,t207.t416.t417.t897,t207.t416.t417.t897,t207.t416.t417.t897,t207.t416.t417.t897,t207.t416.t417.t897,t208.t416.t417.t913,t208.t416.t417.t913,t208.t416.t417.t913,t208.t416.t417.t913,t208.t416.t417.t913,t208.t416.t417.t913,t208.t416.t417.t913,t209.t416.t417.t929,t209.t416.t417.t929,t209.t416.t417.t929,t209.t416.t417.t929,t209.t416.t417.t929,t209.t416.t417.t929,t209.t416.t417.t929,t210.t416.t417.t945,t210.t416.t417.t945,t210.t416.t417.t945,t210.t416.t417.t945,t210.t416.t417.t945,t210.t416.t417.t945,t210.t416.t417.t945,t211.t416.t417.t961,t211.t416.t417.t961,t211.t416.t417.t961,t211.t416.t417.t961,t211.t416.t417.t961,t211.t416.t417.t961,t211.t416.t417.t961,t1046.t155,t1046.t155,t1046.t155,t1046.t155,t1046.t155,t1046.t155,t1046.t155,t1046.t155,t953,t953,t953,t953,t953,t953,t953,t937,t937,t937,t937,t937,t937,t937,t921,t921,t921,t921,t921,t921,t921,t905,t905,t905,t905,t905,t905,t905,t889,t889,t889,t889,t889,t889,t889,t873,t873,t873,t873,t873,t873,t873,t857,t857,t857,t857,t857,t857,t857,t841,t841,t841,t841,t841,t841,t841,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 116 events :t462.t1141.t463,t462.t1141.t463,t1143.t428,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t386.t446.t447.t658,t386.t448.t449.t657,t386.t450.t451.t656,t386.t452.t453.t655,t386.t454.t455.t654,t386.t456.t457.t653,t386.t458.t459.t652,t386.t460.t461.t651,t1143.t428,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,t538,t537,t536,t535,t534,t533,t532,t531,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t19.t111.t520.t112.t519.t113,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 4 events :t22.t90.t47,t22.t90.t47,t22.t90.t47,t22.t90.t47,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t1000.t93.t178,t21.t95.t514.t96.t513.t97,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 7 events :t1.t376.t377,t1.t376.t377,t1.t376.t377,t356.t357.t500,t356.t357.t500,t356.t357.t500,t356.t357.t500,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 6 events :t218.t1130.t219,t218.t1130.t219,t218.t1130.t219,t1126.t368.t370.t497.t372.t496.t499.t371.t498.t494.t369.t495.t0.t373,t1126.t368.t370.t497.t372.t496.t499.t371.t498.t494.t369.t495.t0.t373,t1126.t368.t370.t497.t372.t496.t499.t371.t498.t494.t369.t495.t0.t373,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t1032.t128.t178,t16.t130.t526.t131.t525.t132,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t999.t98.t178,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 84 events :t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t1050.t158.t190,t1050.t158.t178,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t188.t998.t189,t192.t245.t710.t193,t192.t245.t710.t193,t179.t245.t662,t179.t245.t662,t180.t245.t668,t180.t245.t668,t181.t245.t674,t181.t245.t674,t182.t245.t680,t182.t245.t680,t183.t245.t686,t183.t245.t686,t184.t245.t692,t184.t245.t692,t185.t245.t698,t185.t245.t698,t186.t245.t704,t186.t245.t704,t187.t996,t187.t996,t187.t996,t187.t996,t187.t996,t187.t996,t191.t1003,t191.t1003,t191.t1003,t1052.t527.t159.t528.t160,t1026.t523.t143.t524.t144,t1052.t527.t159.t528.t160,t1026.t523.t143.t524.t144,t1026.t523.t143.t524.t144,t1052.t527.t159.t528.t160,t1026.t523.t143.t524.t144,t1026.t523.t143.t524.t144,t1026.t523.t143.t524.t144,t707,t707,t701,t701,t695,t695,t689,t689,t683,t683,t677,t677,t671,t671,t665,t665,t659,t659,

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 704 redundant transitions.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.PropertySimplifier rewriteWithInitialState

INFO: Reachable property ASLink-PT-01b-GlobalProperties-0 is trivially true : it is verified in initial state.

Mar 12, 2019 10:59:42 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 266 ms

Mar 12, 2019 10:59:42 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/GlobalProperties.pnml.gal : 19 ms

Mar 12, 2019 10:59:43 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 54 place invariants in 178 ms

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 303 variables to be positive in 1265 ms

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 508 transitions.

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/508 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 79 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 508 transitions.

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 37 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 12, 2019 10:59:44 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 508 transitions.

Mar 12, 2019 10:59:47 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(12/508) took 3094 ms. Total solver calls (SAT/UNSAT): 1657(249/1408)

Mar 12, 2019 10:59:50 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(35/508) took 6184 ms. Total solver calls (SAT/UNSAT): 4256(380/3876)

Mar 12, 2019 10:59:53 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(67/508) took 9382 ms. Total solver calls (SAT/UNSAT): 7047(648/6399)

Mar 12, 2019 10:59:56 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(83/508) took 12547 ms. Total solver calls (SAT/UNSAT): 8606(1979/6627)

Mar 12, 2019 10:59:59 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(103/508) took 15627 ms. Total solver calls (SAT/UNSAT): 11034(4293/6741)

Mar 12, 2019 11:00:03 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(124/508) took 18762 ms. Total solver calls (SAT/UNSAT): 13890(7149/6741)

Mar 12, 2019 11:00:06 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(149/508) took 21818 ms. Total solver calls (SAT/UNSAT): 16715(9974/6741)

Mar 12, 2019 11:00:09 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(175/508) took 24965 ms. Total solver calls (SAT/UNSAT): 18634(11140/7494)

SMT solver raised 'unknown', retrying with same input.

Skipping mayMatrices nes/nds SMT solver raised an error :unknown

java.lang.RuntimeException: SMT solver raised an error :unknown

at fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver.computeCoEnablingMatrix(NecessaryEnablingsolver.java:490)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.printLabels(Gal2PinsTransformerNext.java:530)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.printDependencyMatrix(Gal2PinsTransformerNext.java:209)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.buildBodyFile(Gal2PinsTransformerNext.java:85)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.transform(Gal2PinsTransformerNext.java:830)

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:71)

at java.lang.Thread.run(Thread.java:748)

Mar 12, 2019 11:00:11 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 29546ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ASLink-PT-01b"

export BK_EXAMINATION="GlobalProperties"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3817"

echo " Executing tool itstools"

echo " Input is ASLink-PT-01b, examination is GlobalProperties"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r008-smll-155225013900021"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ASLink-PT-01b.tgz

mv ASLink-PT-01b execution

cd execution

if [ "GlobalProperties" = "GlobalProperties" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

if [ "GlobalProperties" = "UpperBounds" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "GlobalProperties" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "GlobalProperties" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "GlobalProperties.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property GlobalProperties.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "GlobalProperties.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;