About the Execution of ITS-Tools for ResAllocation-PT-R050C002

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 895.040 | 34943.00 | 113571.00 | 265.50 | FFFFFFFFFFFFTFFF | normal |

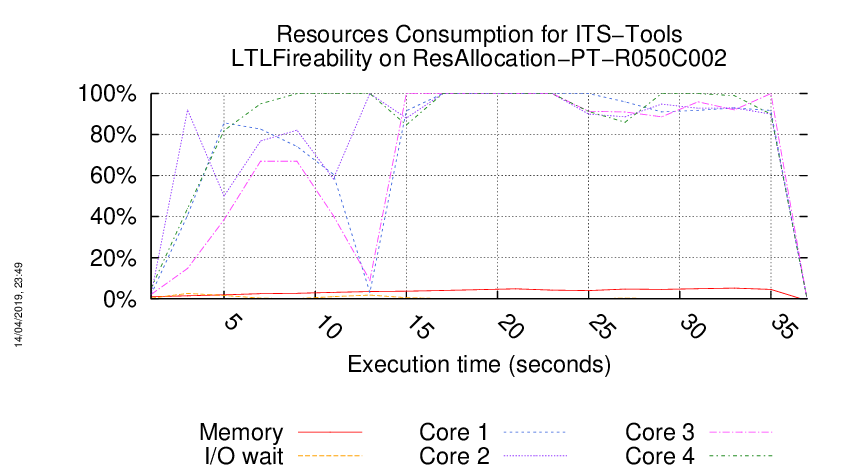

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/mnt/tpsp/fkordon/mcc2019-input.r151-ebro-155286406200124.qcow2', fmt=qcow2 size=4294967296 backing_file='/mnt/tpsp/fkordon/mcc2019-input.qcow2' encryption=off cluster_size=65536 lazy_refcounts=off

Waiting for the VM to be ready (probing ssh)

...................

=====================================================================

Generated by BenchKit 2-3954

Executing tool itstools

Input is ResAllocation-PT-R050C002, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r151-ebro-155286406200124

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 368K

-rw-r--r-- 1 mcc users 3.2K Feb 12 14:31 CTLCardinality.txt

-rw-r--r-- 1 mcc users 16K Feb 12 14:31 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K Feb 8 16:27 CTLFireability.txt

-rw-r--r-- 1 mcc users 19K Feb 8 16:27 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 10 17:31 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.3K Mar 10 17:31 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 112 Feb 24 15:05 GlobalProperties.txt

-rw-r--r-- 1 mcc users 350 Feb 24 15:05 GlobalProperties.xml

-rw-r--r-- 1 mcc users 2.5K Feb 5 01:12 LTLCardinality.txt

-rw-r--r-- 1 mcc users 11K Feb 5 01:12 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K Feb 4 22:47 LTLFireability.txt

-rw-r--r-- 1 mcc users 11K Feb 4 22:47 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Feb 4 16:39 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 20K Feb 4 16:39 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 3.0K Feb 1 13:01 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K Feb 1 13:01 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K Feb 4 22:30 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K Feb 4 22:30 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Jan 29 09:35 equiv_col

-rw-r--r-- 1 mcc users 9 Jan 29 09:35 instance

-rw-r--r-- 1 mcc users 6 Jan 29 09:35 iscolored

-rw-r--r-- 1 mcc users 202K Mar 10 17:31 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-00

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-01

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-02

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-03

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-04

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-05

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-06

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-07

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-08

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-09

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-10

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-11

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-12

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-13

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-14

FORMULA_NAME ResAllocation-PT-R050C002-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1553108649664

Working with output stream class java.io.PrintStream

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903111103/bin/its-ltl-linux64, --gc-threshold, 2000000, -i, /home/mcc/execution/LTLFireability.pnml.gal, -t, CGAL, -LTL, /home/mcc/execution/LTLFireability.ltl, -c, -stutter-deadlock], workingDir=/home/mcc/execution]

its-ltl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903111103/bin/its-ltl-linux64 --gc-threshold 2000000 -i /home/mcc/execution/LTLFireability.pnml.gal -t CGAL -LTL /home/mcc/execution/LTLFireability.ltl -c -stutter-deadlock

Read 16 LTL properties

Checking formula 0 : !((F(("(((r_1_5>=1)&&(p_1_6>=1))&&(r_0_5>=1))")U(("(((r_1_28>=1)&&(p_1_29>=1))&&(r_0_28>=1))")U("(((r_1_23>=1)&&(p_1_24>=1))&&(r_0_23>=1))")))))

Formula 0 simplified : !F("(((r_1_5>=1)&&(p_1_6>=1))&&(r_0_5>=1))" U ("(((r_1_28>=1)&&(p_1_29>=1))&&(r_0_28>=1))" U "(((r_1_23>=1)&&(p_1_24>=1))&&(r_0_23>=1))"))

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 102 rows 200 cols

invariant :p_0_24 + r_0_24 + -1'r_1_24 = 0

invariant :p_1_12 + r_1_12 = 1

invariant :p_1_2 + r_1_2 = 1

invariant :p_1_46 + r_1_46 = 1

invariant :p_0_33 + r_0_33 + -1'r_1_33 = 0

invariant :p_0_44 + r_0_44 + -1'r_1_44 = 0

invariant :p_0_6 + r_0_6 + -1'r_1_6 = 0

invariant :p_1_11 + r_1_11 = 1

invariant :p_0_10 + r_0_10 + -1'r_1_10 = 0

invariant :p_0_0 + r_0_0 + -1'r_1_0 = 0

invariant :p_0_19 + r_0_19 + -1'r_1_19 = 0

invariant :p_1_6 + r_1_6 = 1

invariant :p_0_4 + r_0_4 + -1'r_1_4 = 0

invariant :p_0_12 + r_0_12 + -1'r_1_12 = 0

invariant :p_1_19 + r_1_19 = 1

invariant :p_0_34 + r_0_34 + -1'r_1_34 = 0

invariant :p_0_46 + r_0_46 + -1'r_1_46 = 0

invariant :p_0_9 + r_0_9 + -1'r_1_9 = 0

invariant :p_1_20 + r_1_20 = 1

invariant :p_1_47 + r_1_47 = 1

invariant :p_0_11 + r_0_11 + -1'r_1_11 = 0

invariant :p_1_29 + r_1_29 = 1

invariant :p_0_2 + r_0_2 + -1'r_1_2 = 0

invariant :p_1_37 + r_1_37 = 1

invariant :p_0_35 + r_0_35 + -1'r_1_35 = 0

invariant :p_0_48 + r_0_48 + -1'r_1_48 = 0

invariant :p_0_15 + r_0_15 + -1'r_1_15 = 0

invariant :p_1_27 + r_1_27 = 1

invariant :p_1_34 + r_1_34 = 1

invariant :p_0_17 + r_0_17 + -1'r_1_17 = 0

invariant :p_1_32 + r_1_32 = 1

invariant :p_0_41 + r_0_41 + -1'r_1_41 = 0

invariant :p_1_10 + r_1_10 = 1

invariant :p_1_30 + r_1_30 = 1

invariant :p_1_39 + r_1_39 = 1

invariant :p_0_14 + r_0_14 + -1'r_1_14 = 0

invariant :p_0_43 + r_0_43 + -1'r_1_43 = 0

invariant :p_1_36 + r_1_36 = 1

invariant :p_1_1 + r_1_1 = 1

invariant :p_0_13 + r_0_13 + -1'r_1_13 = 0

invariant :p_0_22 + r_0_22 + -1'r_1_22 = 0

invariant :p_1_17 + r_1_17 = 1

invariant :p_0_26 + r_0_26 + -1'r_1_26 = 0

invariant :p_1_18 + r_1_18 = 1

invariant :p_0_7 + r_0_7 + -1'r_1_7 = 0

invariant :p_0_37 + r_0_37 + -1'r_1_37 = 0

invariant :p_1_5 + r_1_5 = 1

invariant :p_0_27 + r_0_27 + -1'r_1_27 = 0

invariant :p_1_33 + r_1_33 = 1

invariant :p_1_31 + r_1_31 = 1

invariant :p_0_16 + r_0_16 + -1'r_1_16 = 0

invariant :p_1_35 + r_1_35 = 1

invariant :p_1_48 + r_1_48 = 1

invariant :p_1_49 + r_1_49 = 1

invariant :p_0_20 + r_0_20 + -1'r_1_20 = 0

invariant :p_1_0 + r_1_0 = 1

invariant :p_0_21 + r_0_21 + -1'r_1_21 = 0

invariant :p_0_28 + r_0_28 + -1'r_1_28 = 0

invariant :p_1_40 + r_1_40 = 1

invariant :p_0_40 + r_0_40 + -1'r_1_40 = 0

invariant :p_1_4 + r_1_4 = 1

invariant :p_1_23 + r_1_23 = 1

invariant :p_0_39 + r_0_39 + -1'r_1_39 = 0

invariant :p_0_1 + r_0_1 + -1'r_1_1 = 0

invariant :p_1_43 + r_1_43 = 1

invariant :p_1_24 + r_1_24 = 1

invariant :p_0_18 + r_0_18 + -1'r_1_18 = 0

invariant :p_1_9 + r_1_9 = 1

invariant :p_0_8 + r_0_8 + -1'r_1_8 = 0

invariant :p_0_23 + r_0_23 + -1'r_1_23 = 0

invariant :p_1_28 + r_1_28 = 1

invariant :p_1_16 + r_1_16 = 1

invariant :p_1_38 + r_1_38 = 1

invariant :p_1_15 + r_1_15 = 1

invariant :p_0_30 + r_0_30 + -1'r_1_30 = 0

invariant :p_1_25 + r_1_25 = 1

invariant :p_1_41 + r_1_41 = 1

invariant :p_0_45 + r_0_45 + -1'r_1_45 = 0

invariant :p_0_31 + r_0_31 + -1'r_1_31 = 0

invariant :p_1_26 + r_1_26 = 1

invariant :p_1_22 + r_1_22 = 1

invariant :p_0_5 + r_0_5 + -1'r_1_5 = 0

invariant :p_0_32 + r_0_32 + -1'r_1_32 = 0

invariant :p_0_36 + r_0_36 + -1'r_1_36 = 0

invariant :p_1_7 + r_1_7 = 1

invariant :p_1_45 + r_1_45 = 1

invariant :p_1_44 + r_1_44 = 1

invariant :p_0_29 + r_0_29 + -1'r_1_29 = 0

invariant :p_0_3 + r_0_3 + -1'r_1_3 = 0

invariant :p_0_47 + r_0_47 + -1'r_1_47 = 0

invariant :p_0_49 + r_0_49 + -1'r_1_49 = 0

invariant :p_1_3 + r_1_3 = 1

invariant :p_1_42 + r_1_42 = 1

invariant :p_0_25 + r_0_25 + -1'r_1_25 = 0

invariant :p_1_14 + r_1_14 = 1

invariant :p_0_38 + r_0_38 + -1'r_1_38 = 0

invariant :p_0_42 + r_0_42 + -1'r_1_42 = 0

invariant :p_1_13 + r_1_13 = 1

invariant :p_1_8 + r_1_8 = 1

invariant :p_1_21 + r_1_21 = 1

Reverse transition relation is NOT exact ! Due to transitions t_0_50, t_1_0, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/100/2/102

Computing Next relation with stutter on 49 deadlock states

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/home/mcc/execution]

Compilation finished in 3241 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 57 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, <>(((LTLAP0==true))U(((LTLAP1==true))U((LTLAP2==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 7060 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-00 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, []((LTLAP3==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 3439 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-01 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, ([]([](X((LTLAP4==true)))))U(<>(X(<>((LTLAP5==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

2 unique states visited

2 strongly connected components in search stack

2 transitions explored

2 items max in DFS search stack

1403 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,14.0876,252688,1,0,2818,1.38962e+06,230,3282,5942,1.92827e+06,6595

an accepting run exists (use option '-e' to print it)

Formula 0 is FALSE accepting run found.

FORMULA ResAllocation-PT-R050C002-LTLFireability-00 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 1 : !((G("((p_0_41>=1)&&(r_0_42>=1))")))

Formula 1 simplified : !G"((p_0_41>=1)&&(r_0_42>=1))"

Computing Next relation with stutter on 49 deadlock states

3 unique states visited

3 strongly connected components in search stack

3 transitions explored

3 items max in DFS search stack

34 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,14.4239,258476,1,0,2818,1.41805e+06,242,3284,6144,1.96465e+06,6611

an accepting run exists (use option '-e' to print it)

Formula 1 is FALSE accepting run found.

FORMULA ResAllocation-PT-R050C002-LTLFireability-01 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 2 : !(((G(G(X("(((r_1_38>=1)&&(p_1_39>=1))&&(r_0_38>=1))"))))U(F(X(F("((p_0_43>=1)&&(r_0_44>=1))"))))))

Formula 2 simplified : !(GX"(((r_1_38>=1)&&(p_1_39>=1))&&(r_0_38>=1))" U FXF"((p_0_43>=1)&&(r_0_44>=1))")

Computing Next relation with stutter on 49 deadlock states

LTSmin run took 1510 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-02 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, <>((X((LTLAP6==true)))U([]([]((LTLAP6==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 649 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-03 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>(([]((LTLAP7==true)))U(<>((LTLAP8==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 851 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-04 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X((((LTLAP9==true))U((LTLAP10==true)))U(<>((LTLAP11==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 1114 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-05 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, ((LTLAP12==true))U(((LTLAP13==true))U([]((LTLAP14==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 615 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-06 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, (X(<>(<>((LTLAP15==true)))))U(<>(((LTLAP16==true))U((LTLAP17==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 1069 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-07 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>(X(<>(X((LTLAP18==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 1096 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-08 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, (LTLAP19==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 835 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-09 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, []((LTLAP20==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 765 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-10 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, <>([]((LTLAP21==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 695 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-11 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, ([]([]([]((LTLAP18==true)))))U(<>((LTLAP22==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 143 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-12 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, (([]((LTLAP23==true)))U([]((LTLAP8==true))))U([]((LTLAP12==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 352 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-13 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, ((LTLAP24==true))U(((LTLAP13==true))U([]((LTLAP25==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 718 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-14 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, <>([]((LTLAP26==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 619 ms.

FORMULA ResAllocation-PT-R050C002-LTLFireability-15 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1553108684607

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ LTLFireability = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution LTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination LTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 136 ms

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 200 places.

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 102 transitions.

Mar 20, 2019 7:04:13 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 29 ms

Mar 20, 2019 7:04:13 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 104 ms

Mar 20, 2019 7:04:13 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/LTLFireability.pnml.gal : 8 ms

Mar 20, 2019 7:04:13 PM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSLTLTools

INFO: Time to serialize properties into /home/mcc/execution/LTLFireability.ltl : 3 ms

Mar 20, 2019 7:04:14 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 102 transitions.

Mar 20, 2019 7:04:14 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 100 place invariants in 97 ms

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 200 variables to be positive in 747 ms

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 102 transitions.

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/102 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 14 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 102 transitions.

Mar 20, 2019 7:04:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 8 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 20, 2019 7:04:16 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 102 transitions.

Mar 20, 2019 7:04:18 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(65/102) took 1335 ms. Total solver calls (SAT/UNSAT): 165(150/15)

Mar 20, 2019 7:04:18 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 2014 ms. Total solver calls (SAT/UNSAT): 200(150/50)

Mar 20, 2019 7:04:18 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 102 transitions.

Mar 20, 2019 7:04:19 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 248 ms. Total solver calls (SAT/UNSAT): 151(0/151)

Mar 20, 2019 7:04:19 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 5099ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ResAllocation-PT-R050C002"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3954"

echo " Executing tool itstools"

echo " Input is ResAllocation-PT-R050C002, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r151-ebro-155286406200124"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ResAllocation-PT-R050C002.tgz

mv ResAllocation-PT-R050C002 execution

cd execution

if [ "LTLFireability" = "GlobalProperties" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

if [ "LTLFireability" = "UpperBounds" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;