About the Execution of ITS-Tools for ProductionCell-PT-none

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 696.190 | 14410.00 | 40479.00 | 147.90 | FFFFTFFFFFFFTFFF | normal |

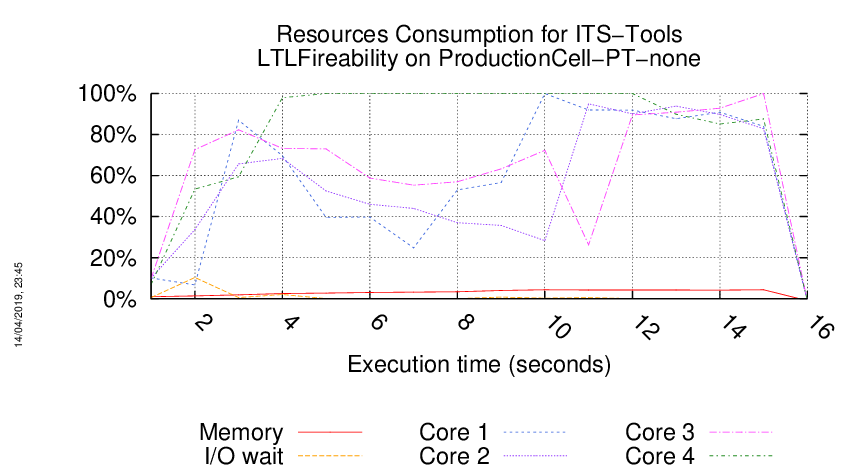

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fko/mcc2019-input.r129-oct2-155274856600187.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fko/mcc2019-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

....................

=====================================================================

Generated by BenchKit 2-3954

Executing tool itstools

Input is ProductionCell-PT-none, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r129-oct2-155274856600187

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 220K

-rw-r--r-- 1 mcc users 4.1K Feb 12 10:30 CTLCardinality.txt

-rw-r--r-- 1 mcc users 24K Feb 12 10:30 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.6K Feb 8 12:39 CTLFireability.txt

-rw-r--r-- 1 mcc users 18K Feb 8 12:39 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 10 17:31 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.8K Mar 10 17:31 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 109 Feb 24 15:05 GlobalProperties.txt

-rw-r--r-- 1 mcc users 347 Feb 24 15:05 GlobalProperties.xml

-rw-r--r-- 1 mcc users 2.3K Feb 5 00:43 LTLCardinality.txt

-rw-r--r-- 1 mcc users 9.8K Feb 5 00:43 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9K Feb 4 22:41 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.8K Feb 4 22:41 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Feb 4 13:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 21K Feb 4 13:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 2.6K Feb 1 10:17 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 15K Feb 1 10:17 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K Feb 4 22:26 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K Feb 4 22:26 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 Jan 29 09:34 equiv_col

-rw-r--r-- 1 mcc users 5 Jan 29 09:34 instance

-rw-r--r-- 1 mcc users 6 Jan 29 09:34 iscolored

-rw-r--r-- 1 mcc users 43K Mar 10 17:31 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ProductionCell-PT-none-LTLFireability-00

FORMULA_NAME ProductionCell-PT-none-LTLFireability-01

FORMULA_NAME ProductionCell-PT-none-LTLFireability-02

FORMULA_NAME ProductionCell-PT-none-LTLFireability-03

FORMULA_NAME ProductionCell-PT-none-LTLFireability-04

FORMULA_NAME ProductionCell-PT-none-LTLFireability-05

FORMULA_NAME ProductionCell-PT-none-LTLFireability-06

FORMULA_NAME ProductionCell-PT-none-LTLFireability-07

FORMULA_NAME ProductionCell-PT-none-LTLFireability-08

FORMULA_NAME ProductionCell-PT-none-LTLFireability-09

FORMULA_NAME ProductionCell-PT-none-LTLFireability-10

FORMULA_NAME ProductionCell-PT-none-LTLFireability-11

FORMULA_NAME ProductionCell-PT-none-LTLFireability-12

FORMULA_NAME ProductionCell-PT-none-LTLFireability-13

FORMULA_NAME ProductionCell-PT-none-LTLFireability-14

FORMULA_NAME ProductionCell-PT-none-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1553952803776

Working with output stream class java.io.PrintStream

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903171603/bin/its-ltl-linux64, --gc-threshold, 2000000, -i, /home/mcc/execution/LTLFireability.pnml.gal, -t, CGAL, -LTL, /home/mcc/execution/LTLFireability.ltl, -c, -stutter-deadlock], workingDir=/home/mcc/execution]

its-ltl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201903171603/bin/its-ltl-linux64 --gc-threshold 2000000 -i /home/mcc/execution/LTLFireability.pnml.gal -t CGAL -LTL /home/mcc/execution/LTLFireability.ltl -c -stutter-deadlock

Read 16 LTL properties

Checking formula 0 : !((F(X(("(u24.p121>=1)")U(G("((u11.p38>=1)&&(i24.u40.p148>=1))"))))))

Formula 0 simplified : !FX("(u24.p121>=1)" U G"((u11.p38>=1)&&(i24.u40.p148>=1))")

built 35 ordering constraints for composite.

built 10 ordering constraints for composite.

built 42 ordering constraints for composite.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 134 rows 176 cols

invariant :u18:p72 + u18:p73 + u18:p74 + u18:p93 + u18:p94 + u18:p95 + u18:p96 + u18:p97 + u18:p98 + u18:p99 + u18:p100 + u18:p101 + -1'u26:p141 + -1'u26:p142 + -1'u26:p143 + -1'u26:p144 = 0

invariant :u19:p102 + u19:p105 + -1'u22:p116 + -1'u22:p117 + -1'u22:p118 = 0

invariant :u22:p113 + u22:p114 + u22:p115 + u22:p116 + u22:p117 + u22:p118 + u38:p0 = 1

invariant :u20:p107 + u20:p108 + u20:p109 + u24:p121 + u24:p125 + u24:p126 + u24:p127 + u38:p0 = 1

invariant :u38:p0 + i1:u4:p8 + i1:u4:p9 + i1:u39:p3 + i1:u39:p4 + i1:u39:p5 = 1

invariant :i24:u28:p156 + i24:u28:p157 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u17:p66 + u17:p67 + u38:p0 = 1

invariant :u12:p39 + u12:p40 + u12:p41 + u12:p42 + u12:p43 + u12:p44 + u12:p45 + u38:p0 = 1

invariant :u19:p103 + u19:p104 + u22:p116 + u22:p117 + u22:p118 + u38:p0 = 1

invariant :i24:u29:p158 + i24:u29:p159 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u10:p33 + u10:p34 + u10:p35 + -1'u12:p42 = 0

invariant :i24:u30:p160 + i24:u30:p161 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u21:p111 + u21:p112 + u38:p0 = 1

invariant :i24:u31:p162 + i24:u31:p163 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u18:p81 + u18:p82 + u18:p83 + u18:p99 + u18:p100 + u18:p101 + -1'u26:p131 + -1'u26:p132 + -1'u26:p133 + -1'u26:p134 + -1'u26:p135 + -1'u26:p142 + -1'u26:p143 + -1'u26:p144 = 0

invariant :u38:p0 + i1:u3:p6 + i1:u3:p7 + i1:u39:p3 + i1:u39:p4 + i1:u39:p5 = 1

invariant :i24:u32:p164 + i24:u32:p165 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :i24:u36:p172 + i24:u36:p173 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u1:p1 + u1:p2 + u38:p0 = 1

invariant :i24:u35:p170 + i24:u35:p171 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :i24:u33:p166 + i24:u33:p167 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u6:p15 + u6:p16 + u6:p17 + u7:p19 + 2'u7:p20 + 3'u7:p21 + 4'u7:p22 + 5'u7:p23 + -1'u12:p42 + -1'u12:p43 + -1'u12:p44 + -1'u12:p45 + u16:p60 + u16:p61 + u16:p62 + u16:p63 + -1'u22:p116 + -1'u22:p117 + -1'u22:p118 + -1'u24:p121 + -1'u24:p125 + -1'u24:p126 + -1'u24:p127 + -1'u26:p137 + -1'u26:p138 + -1'u26:p139 + -1'u26:p140 + -1'u26:p141 + -1'u26:p142 + -1'u26:p143 + -1'u26:p144 + -1'i1:u3:p7 + i1:u4:p9 + -1'i1:u39:p5 = 0

invariant :i24:u34:p168 + i24:u34:p169 + -1'i24:u37:p174 + -1'i24:u37:p175 = 0

invariant :u18:p84 + u18:p85 + u18:p86 + -1'u26:p136 = 0

invariant :u8:p25 + u8:p26 + u12:p42 + u12:p43 + u12:p44 + u12:p45 + u38:p0 = 1

invariant :u18:p69 + u18:p70 + u18:p71 + u18:p90 + u18:p91 + u18:p92 + -1'u26:p138 + -1'u26:p139 + -1'u26:p140 = 0

invariant :u18:p68 + -1'u18:p90 + -1'u18:p91 + -1'u18:p92 + -1'u18:p93 + -1'u18:p94 + -1'u18:p95 + -1'u18:p96 + -1'u18:p97 + -1'u18:p98 + -1'u18:p99 + -1'u18:p100 + -1'u18:p101 + u22:p116 + u22:p117 + u22:p118 + u26:p138 + u26:p139 + u26:p140 + u26:p141 + u26:p142 + u26:p143 + u26:p144 + u38:p0 = 1

invariant :u10:p30 + u10:p31 + u10:p32 + u12:p42 + u12:p43 + u12:p44 + u12:p45 + u38:p0 = 1

invariant :u18:p78 + u18:p79 + u18:p80 + u18:p96 + u18:p97 + u18:p98 + -1'u24:p121 + -1'u24:p125 + -1'u24:p126 + -1'u24:p127 + u26:p131 + u26:p132 + u26:p133 + u26:p134 + u26:p135 + u26:p136 + u26:p142 + u26:p143 + u26:p144 = 0

invariant :u24:p121 + u24:p122 + u24:p123 + u24:p124 + u24:p125 + u24:p126 + u24:p127 + u38:p0 = 1

invariant :u6:p13 + u6:p14 + -1'u16:p63 = 0

invariant :u26:p130 + u26:p131 + u26:p132 + u26:p133 + u26:p134 + u26:p135 + u26:p136 + u26:p137 + u26:p138 + u26:p139 + u26:p140 + u26:p141 + u26:p142 + u26:p143 + u26:p144 + u38:p0 = 1

invariant :u10:p36 + -1'u12:p43 + -1'u12:p44 + -1'u12:p45 = 0

invariant :u16:p59 + u20:p107 + u24:p121 + u24:p125 + u24:p126 + u24:p127 + u38:p0 = 1

invariant :u20:p106 + u20:p110 + -1'u24:p121 + -1'u24:p125 + -1'u24:p126 + -1'u24:p127 = 0

invariant :u9:p28 + u9:p29 + u38:p0 = 1

invariant :u14:p50 + u14:p51 + u14:p52 + -1'u16:p60 + -1'u16:p61 + -1'u16:p62 = 0

invariant :u25:p128 + u25:p129 + u38:p0 = 1

invariant :u15:p55 + u15:p56 + u38:p0 = 1

invariant :u38:p0 + i24:u37:p174 + i24:u37:p175 + i24:u40:p145 + i24:u40:p146 + i24:u40:p147 + i24:u40:p148 + i24:u40:p149 + i24:u40:p150 + i24:u40:p151 + i24:u40:p152 + i24:u40:p153 + i24:u40:p154 + i24:u40:p155 = 1

invariant :u11:p37 + u11:p38 + u38:p0 = 1

invariant :u18:p87 + u18:p88 + u18:p89 + u18:p90 + u18:p91 + u18:p92 + u18:p93 + u18:p94 + u18:p95 + u18:p96 + u18:p97 + u18:p98 + u18:p99 + u18:p100 + u18:p101 + -1'u22:p116 + -1'u22:p117 + -1'u22:p118 + -1'u26:p137 + -1'u26:p138 + -1'u26:p139 + -1'u26:p140 + -1'u26:p141 + -1'u26:p142 + -1'u26:p143 + -1'u26:p144 + -1'u38:p0 = -1

invariant :u6:p12 + u6:p18 + -1'u7:p19 + -2'u7:p20 + -3'u7:p21 + -4'u7:p22 + -5'u7:p23 + u12:p42 + u12:p43 + u12:p44 + u12:p45 + -1'u16:p60 + -1'u16:p61 + -1'u16:p62 + u22:p116 + u22:p117 + u22:p118 + u24:p121 + u24:p125 + u24:p126 + u24:p127 + u26:p137 + u26:p138 + u26:p139 + u26:p140 + u26:p141 + u26:p142 + u26:p143 + u26:p144 + u38:p0 + i1:u3:p7 + -1'i1:u4:p9 + i1:u39:p5 = 1

invariant :u23:p119 + u23:p120 + u38:p0 = 1

invariant :u14:p48 + u14:p49 + u14:p53 + u14:p54 + u16:p60 + u16:p61 + u16:p62 + u16:p63 + -1'u20:p107 + -1'u24:p121 + -1'u24:p125 + -1'u24:p126 + -1'u24:p127 = 0

invariant :u8:p24 + u8:p27 + -1'u12:p42 + -1'u12:p43 + -1'u12:p44 + -1'u12:p45 = 0

invariant :u18:p75 + u18:p76 + u18:p77 + -1'u18:p96 + -1'u18:p97 + -1'u18:p98 + -1'u18:p99 + -1'u18:p100 + -1'u18:p101 + u24:p121 + u24:p125 + u24:p126 + u24:p127 + u26:p137 + u26:p138 + u26:p139 + u26:p140 + u26:p141 + u26:p142 + u26:p143 + u26:p144 + u38:p0 = 1

invariant :u13:p46 + u13:p47 + u38:p0 = 1

invariant :u16:p57 + u16:p58 + u16:p60 + u16:p61 + u16:p62 + u16:p63 + u16:p64 + u16:p65 + -1'u20:p107 + -1'u24:p121 + -1'u24:p125 + -1'u24:p126 + -1'u24:p127 = 0

invariant :u5:p10 + u5:p11 + u38:p0 = 1

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O2, model.c], workingDir=/home/mcc/execution]

Compilation finished in 1945 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 63 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, <>(X(((LTLAP0==true))U([]((LTLAP1==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 75 ms.

FORMULA ProductionCell-PT-none-LTLFireability-00 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, (<>(X(X((LTLAP2==true)))))U((<>((LTLAP3==true)))U([]((LTLAP4==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 302 ms.

FORMULA ProductionCell-PT-none-LTLFireability-01 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, false, --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 481 ms.

FORMULA ProductionCell-PT-none-LTLFireability-02 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, false, --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 220 ms.

FORMULA ProductionCell-PT-none-LTLFireability-03 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>(((LTLAP5==true))U((LTLAP6==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 326 ms.

FORMULA ProductionCell-PT-none-LTLFireability-04 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, <>(X(<>(<>([]((LTLAP7==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 349 ms.

FORMULA ProductionCell-PT-none-LTLFireability-05 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>([]((LTLAP8==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 225 ms.

FORMULA ProductionCell-PT-none-LTLFireability-06 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>(X([](X((LTLAP9==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 169 ms.

FORMULA ProductionCell-PT-none-LTLFireability-07 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(<>(<>(((LTLAP10==true))U((LTLAP11==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 244 ms.

FORMULA ProductionCell-PT-none-LTLFireability-08 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, <>([]((LTLAP12==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 418 ms.

FORMULA ProductionCell-PT-none-LTLFireability-09 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, X(X((LTLAP13==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 287 ms.

FORMULA ProductionCell-PT-none-LTLFireability-10 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, false, --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 241 ms.

FORMULA ProductionCell-PT-none-LTLFireability-11 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, -p, --pins-guards, --when, --ltl, <>((LTLAP14==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 262 ms.

FORMULA ProductionCell-PT-none-LTLFireability-12 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, ((X((LTLAP15==true)))U([]((LTLAP16==true))))U((LTLAP17==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 202 ms.

FORMULA ProductionCell-PT-none-LTLFireability-13 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, (([]((LTLAP18==true)))U(X((LTLAP19==true))))U([](X(X((LTLAP20==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 210 ms.

FORMULA ProductionCell-PT-none-LTLFireability-14 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=8, --when, --ltl, []([](X(X(X((LTLAP0==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 448 ms.

FORMULA ProductionCell-PT-none-LTLFireability-15 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1553952818186

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ LTLFireability = StateSpace ]]

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution LTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination LTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 41 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 176 places.

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 134 transitions.

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

Mar 30, 2019 1:33:25 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 9 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 46 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 24 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 9 events :t44,t45,t44,t45,t44,t45,t44,t45,t44,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t113,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t121,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t99,t33,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t100,t56,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t121,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t113,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t113,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 3 events :t98,t60,t60,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 3 events :t97,t28,t28,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t41,t101,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 4 events :t93,t14,t14,t14,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t95,t22,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 11 events :t96,t74,t74,t74,t74,t74,t74,t74,t74,t74,t74,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 4 events :t132,t130,t128,t124,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t113,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 2 events :t94,t90,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 3 events :t125,t124,t121,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 5 events :t52,t50,t48,t46,t44,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t102,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator dropEvents

INFO: Dropping 1 events :t1,

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 60 redundant transitions.

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 63 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/LTLFireability.pnml.gal : 5 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSLTLTools

INFO: Time to serialize properties into /home/mcc/execution/LTLFireability.ltl : 1 ms

Mar 30, 2019 1:33:25 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 134 transitions.

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 50 place invariants in 44 ms

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 176 variables to be positive in 267 ms

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 134 transitions.

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/134 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 3 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 134 transitions.

Mar 30, 2019 1:33:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 3 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Mar 30, 2019 1:33:27 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 134 transitions.

Mar 30, 2019 1:33:29 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(39/134) took 2247 ms. Total solver calls (SAT/UNSAT): 1171(761/410)

Mar 30, 2019 1:33:31 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 4146 ms. Total solver calls (SAT/UNSAT): 1976(1160/816)

Mar 30, 2019 1:33:31 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 134 transitions.

Mar 30, 2019 1:33:31 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 106 ms. Total solver calls (SAT/UNSAT): 89(0/89)

Mar 30, 2019 1:33:31 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 5566ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ProductionCell-PT-none"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3954"

echo " Executing tool itstools"

echo " Input is ProductionCell-PT-none, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r129-oct2-155274856600187"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/ProductionCell-PT-none.tgz

mv ProductionCell-PT-none execution

cd execution

if [ "LTLFireability" = "GlobalProperties" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

if [ "LTLFireability" = "UpperBounds" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;