About the Execution of 2018-Gold for PermAdmissibility-PT-05

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15910.220 | 348520.00 | 363663.00 | 424.50 | FFF??T??FFFFFFFF | normal |

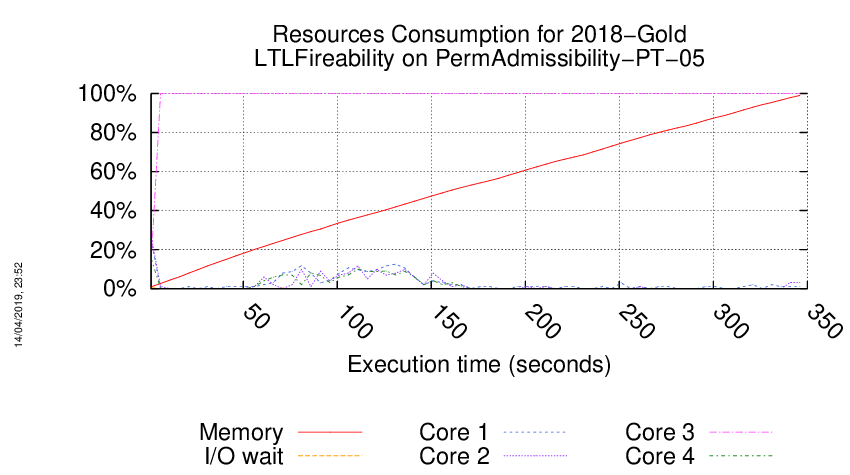

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Formatting '/data/fko/mcc2019-input.r110-oct2-155272242300147.qcow2', fmt=qcow2 size=4294967296 backing_file=/data/fko/mcc2019-input.qcow2 cluster_size=65536 lazy_refcounts=off refcount_bits=16

Waiting for the VM to be ready (probing ssh)

........................................

=====================================================================

Generated by BenchKit 2-3954

Executing tool win2018

Input is PermAdmissibility-PT-05, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r110-oct2-155272242300147

=====================================================================

--------------------

preparation of the directory to be used:

/home/mcc/execution

total 848K

-rw-r--r-- 1 mcc users 5.1K Feb 12 04:11 CTLCardinality.txt

-rw-r--r-- 1 mcc users 27K Feb 12 04:11 CTLCardinality.xml

-rw-r--r-- 1 mcc users 21K Feb 8 03:12 CTLFireability.txt

-rw-r--r-- 1 mcc users 81K Feb 8 03:12 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K Mar 10 17:31 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K Mar 10 17:31 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 110 Feb 24 15:05 GlobalProperties.txt

-rw-r--r-- 1 mcc users 348 Feb 24 15:05 GlobalProperties.xml

-rw-r--r-- 1 mcc users 3.2K Feb 5 00:23 LTLCardinality.txt

-rw-r--r-- 1 mcc users 13K Feb 5 00:23 LTLCardinality.xml

-rw-r--r-- 1 mcc users 9.5K Feb 4 22:37 LTLFireability.txt

-rw-r--r-- 1 mcc users 36K Feb 4 22:37 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.9K Feb 4 07:56 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 18K Feb 4 07:56 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 18K Feb 1 02:09 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 64K Feb 1 02:09 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.9K Feb 4 22:22 UpperBounds.txt

-rw-r--r-- 1 mcc users 4.1K Feb 4 22:22 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 Jan 29 09:34 equiv_col

-rw-r--r-- 1 mcc users 3 Jan 29 09:34 instance

-rw-r--r-- 1 mcc users 6 Jan 29 09:34 iscolored

-rw-r--r-- 1 mcc users 481K Mar 10 17:31 model.pnml

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-00

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-01

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-02

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-03

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-04

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-05

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-06

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-07

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-08

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-09

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-10

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-11

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-12

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-13

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-14

FORMULA_NAME PermAdmissibility-PT-05-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1553039083559

info: Time: 3600 - MCC

===========================================================================================

prep: translating PermAdmissibility-PT-05 Petri net model.pnml into LoLA format

===========================================================================================

prep: translating PT Petri net complete

prep: check for too many tokens

===========================================================================================

prep: translating PermAdmissibility-PT-05 formula LTLFireability into LoLA format

===========================================================================================

prep: translating PT formula complete

vrfy: Checking LTLFireability @ PermAdmissibility-PT-05 @ 3570 seconds

lola: LoLA will run for 3570 seconds at most (--timelimit)

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 760/65536 symbol table entries, 0 collisions

lola: preprocessing...

lola: Size of bit vector: 5376

lola: finding significant places

lola: 168 places, 592 transitions, 136 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 820 transition conflict sets

lola: TASK

lola: reading formula from PermAdmissibility-PT-05-LTLFireability.task

lola: A ((FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(switch6_0_2))) : A ((FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(switch6_0_2))) : A ((FIREABLE(switch5_5_2) OR FIREABLE(switch5_0_3) OR FIREABLE(switch5_1_2) OR FIREABLE(switch5_4_2) OR FIREABLE(switch5_0_2) OR FIREABLE(switch5_4_7) OR FIREABLE(switch5_1_7) OR FIREABLE(switch5_5_7) OR FIREABLE(switch5_4_6) OR FIREABLE(switch5_1_6) OR FIREABLE(switch5_0_7) OR FIREABLE(switch5_5_6) OR FIREABLE(switch5_4_3) OR FIREABLE(switch5_1_3) OR FIREABLE(switch5_0_6) OR FIREABLE(switch5_5_3))) : A ((((FIREABLE(switch8_1_7) OR FIREABLE(switch8_4_7) OR FIREABLE(switch8_5_7) OR FIREABLE(switch8_1_3) OR FIREABLE(switch8_4_3) OR FIREABLE(switch8_5_3) OR FIREABLE(switch8_0_6) OR FIREABLE(switch8_1_6) OR FIREABLE(switch8_4_6) OR FIREABLE(switch8_5_6) OR FIREABLE(switch8_0_7) OR FIREABLE(switch8_0_2) OR FIREABLE(switch8_4_2) OR FIREABLE(switch8_1_2) OR FIREABLE(switch8_0_3) OR FIREABLE(switch8_5_2)) U G ((FIREABLE(switch9_1_0) OR FIREABLE(switch9_2_0) OR FIREABLE(switch9_3_0) OR FIREABLE(switch9_4_0) OR FIREABLE(switch9_0_0) OR FIREABLE(switch9_3_5) OR FIREABLE(switch9_4_5) OR FIREABLE(switch9_1_5) OR FIREABLE(switch9_2_5) OR FIREABLE(switch9_7_4) OR FIREABLE(switch9_0_5) OR FIREABLE(switch9_5_4) OR FIREABLE(switch9_6_4) OR FIREABLE(switch9_3_6) OR FIREABLE(switch9_4_6) OR FIREABLE(switch9_1_6) OR FIREABLE(switch9_2_6) OR FIREABLE(switch9_7_5) OR FIREABLE(switch9_0_6) OR FIREABLE(switch9_5_5) OR FIREABLE(switch9_6_5) OR FIREABLE(switch9_4_7) OR FIREABLE(switch9_3_7) OR FIREABLE(switch9_2_7) OR FIREABLE(switch9_1_7) OR FIREABLE(switch9_0_7) OR FIREABLE(switch9_7_6) OR FIREABLE(switch9_6_6) OR FIREABLE(switch9_5_6) OR FIREABLE(switch9_7_7) OR FIREABLE(switch9_6_7) OR FIREABLE(switch9_5_7) OR FIREABLE(switch9_1_1) OR FIREABLE(switch9_2_1) OR FIREABLE(switch9_3_1) OR FIREABLE(switch9_4_1) OR FIREABLE(switch9_5_0) OR FIREABLE(switch9_6_0) OR FIREABLE(switch9_7_0) OR FIREABLE(switch9_0_1) OR FIREABLE(switch9_1_2) OR FIREABLE(switch9_2_2) OR FIREABLE(switch9_3_2) OR FIREABLE(switch9_4_2) OR FIREABLE(switch9_5_1) OR FIREABLE(switch9_6_1) OR FIREABLE(switch9_7_1) OR FIREABLE(switch9_0_2) OR FIREABLE(switch9_2_3) OR FIREABLE(switch9_1_3) OR FIREABLE(switch9_4_3) OR FIREABLE(switch9_3_3) OR FIREABLE(switch9_6_2) OR FIREABLE(switch9_5_2) OR FIREABLE(switch9_0_3) OR FIREABLE(switch9_7_2) OR FIREABLE(switch9_2_4) OR FIREABLE(switch9_1_4) OR FIREABLE(switch9_4_4) OR FIREABLE(switch9_3_4) OR FIREABLE(switch9_6_3) OR FIREABLE(switch9_5_3) OR FIREABLE(switch9_0_4) OR FIREABLE(switch9_7_3)))) U G (F (F ((FIREABLE(switch11_0_0) OR FIREABLE(switch11_4_0) OR FIREABLE(switch11_3_0) OR FIREABLE(switch11_2_0) OR FIREABLE(switch11_1_0) OR FIREABLE(switch11_4_6) OR FIREABLE(switch11_3_6) OR FIREABLE(switch11_2_6) OR FIREABLE(switch11_1_6) OR FIREABLE(switch11_0_6) OR FIREABLE(switch11_7_5) OR FIREABLE(switch11_6_5) OR FIREABLE(switch11_5_5) OR FIREABLE(switch11_4_5) OR FIREABLE(switch11_3_5) OR FIREABLE(switch11_2_5) OR FIREABLE(switch11_1_5) OR FIREABLE(switch11_0_5) OR FIREABLE(switch11_7_4) OR FIREABLE(switch11_6_4) OR FIREABLE(switch11_5_4) OR FIREABLE(switch11_7_7) OR FIREABLE(switch11_5_7) OR FIREABLE(switch11_6_7) OR FIREABLE(switch11_3_7) OR FIREABLE(switch11_4_7) OR FIREABLE(switch11_1_7) OR FIREABLE(switch11_2_7) OR FIREABLE(switch11_7_6) OR FIREABLE(switch11_0_7) OR FIREABLE(switch11_5_6) OR FIREABLE(switch11_6_6) OR FIREABLE(switch11_2_2) OR FIREABLE(switch11_1_2) OR FIREABLE(switch11_4_2) OR FIREABLE(switch11_3_2) OR FIREABLE(switch11_6_1) OR FIREABLE(switch11_5_1) OR FIREABLE(switch11_0_2) OR FIREABLE(switch11_7_1) OR FIREABLE(switch11_2_1) OR FIREABLE(switch11_1_1) OR FIREABLE(switch11_4_1) OR FIREABLE(switch11_3_1) OR FIREABLE(switch11_6_0) OR FIREABLE(switch11_5_0) OR FIREABLE(switch11_0_1) OR FIREABLE(switch11_7_0) OR FIREABLE(switch11_1_4) OR FIREABLE(switch11_2_4) OR FIREABLE(switch11_3_4) OR FIREABLE(switch11_4_4) OR FIREABLE(switch11_5_3) OR FIREABLE(switch11_6_3) OR FIREABLE(switch11_7_3) OR FIREABLE(switch11_0_4) OR FIREABLE(switch11_1_3) OR FIREABLE(switch11_2_3) OR FIREABLE(switch11_3_3) OR FIREABLE(switch11_4_3) OR FIREABLE(switch11_5_2) OR FIREABLE(switch11_6_2) OR FIREABLE(switch11_7_2) OR FIREABLE(switch11_0_3))))))) : A (G ((G (F ((FIREABLE(switch2_1_4) OR FIREABLE(switch2_0_5) OR FIREABLE(switch2_1_5) OR FIREABLE(switch2_0_4)))) U F (F ((FIREABLE(switch9_1_0) OR FIREABLE(switch9_2_0) OR FIREABLE(switch9_3_0) OR FIREABLE(switch9_4_0) OR FIREABLE(switch9_0_0) OR FIREABLE(switch9_3_5) OR FIREABLE(switch9_4_5) OR FIREABLE(switch9_1_5) OR FIREABLE(switch9_2_5) OR FIREABLE(switch9_7_4) OR FIREABLE(switch9_0_5) OR FIREABLE(switch9_5_4) OR FIREABLE(switch9_6_4) OR FIREABLE(switch9_3_6) OR FIREABLE(switch9_4_6) OR FIREABLE(switch9_1_6) OR FIREABLE(switch9_2_6) OR FIREABLE(switch9_7_5) OR FIREABLE(switch9_0_6) OR FIREABLE(switch9_5_5) OR FIREABLE(switch9_6_5) OR FIREABLE(switch9_4_7) OR FIREABLE(switch9_3_7) OR FIREABLE(switch9_2_7) OR FIREABLE(switch9_1_7) OR FIREABLE(switch9_0_7) OR FIREABLE(switch9_7_6) OR FIREABLE(switch9_6_6) OR FIREABLE(switch9_5_6) OR FIREABLE(switch9_7_7) OR FIREABLE(switch9_6_7) OR FIREABLE(switch9_5_7) OR FIREABLE(switch9_1_1) OR FIREABLE(switch9_2_1) OR FIREABLE(switch9_3_1) OR FIREABLE(switch9_4_1) OR FIREABLE(switch9_5_0) OR FIREABLE(switch9_6_0) OR FIREABLE(switch9_7_0) OR FIREABLE(switch9_0_1) OR FIREABLE(switch9_1_2) OR FIREABLE(switch9_2_2) OR FIREABLE(switch9_3_2) OR FIREABLE(switch9_4_2) OR FIREABLE(switch9_5_1) OR FIREABLE(switch9_6_1) OR FIREABLE(switch9_7_1) OR FIREABLE(switch9_0_2) OR FIREABLE(switch9_2_3) OR FIREABLE(switch9_1_3) OR FIREABLE(switch9_4_3) OR FIREABLE(switch9_3_3) OR FIREABLE(switch9_6_2) OR FIREABLE(switch9_5_2) OR FIREABLE(switch9_0_3) OR FIREABLE(switch9_7_2) OR FIREABLE(switch9_2_4) OR FIREABLE(switch9_1_4) OR FIREABLE(switch9_4_4) OR FIREABLE(switch9_3_4) OR FIREABLE(switch9_6_3) OR FIREABLE(switch9_5_3) OR FIREABLE(switch9_0_4) OR FIREABLE(switch9_7_3))))))) : A (F ((F (F ((FIREABLE(switch11_0_0) OR FIREABLE(switch11_4_0) OR FIREABLE(switch11_3_0) OR FIREABLE(switch11_2_0) OR FIREABLE(switch11_1_0) OR FIREABLE(switch11_4_6) OR FIREABLE(switch11_3_6) OR FIREABLE(switch11_2_6) OR FIREABLE(switch11_1_6) OR FIREABLE(switch11_0_6) OR FIREABLE(switch11_7_5) OR FIREABLE(switch11_6_5) OR FIREABLE(switch11_5_5) OR FIREABLE(switch11_4_5) OR FIREABLE(switch11_3_5) OR FIREABLE(switch11_2_5) OR FIREABLE(switch11_1_5) OR FIREABLE(switch11_0_5) OR FIREABLE(switch11_7_4) OR FIREABLE(switch11_6_4) OR FIREABLE(switch11_5_4) OR FIREABLE(switch11_7_7) OR FIREABLE(switch11_5_7) OR FIREABLE(switch11_6_7) OR FIREABLE(switch11_3_7) OR FIREABLE(switch11_4_7) OR FIREABLE(switch11_1_7) OR FIREABLE(switch11_2_7) OR FIREABLE(switch11_7_6) OR FIREABLE(switch11_0_7) OR FIREABLE(switch11_5_6) OR FIREABLE(switch11_6_6) OR FIREABLE(switch11_2_2) OR FIREABLE(switch11_1_2) OR FIREABLE(switch11_4_2) OR FIREABLE(switch11_3_2) OR FIREABLE(switch11_6_1) OR FIREABLE(switch11_5_1) OR FIREABLE(switch11_0_2) OR FIREABLE(switch11_7_1) OR FIREABLE(switch11_2_1) OR FIREABLE(switch11_1_1) OR FIREABLE(switch11_4_1) OR FIREABLE(switch11_3_1) OR FIREABLE(switch11_6_0) OR FIREABLE(switch11_5_0) OR FIREABLE(switch11_0_1) OR FIREABLE(switch11_7_0) OR FIREABLE(switch11_1_4) OR FIREABLE(switch11_2_4) OR FIREABLE(switch11_3_4) OR FIREABLE(switch11_4_4) OR FIREABLE(switch11_5_3) OR FIREABLE(switch11_6_3) OR FIREABLE(switch11_7_3) OR FIREABLE(switch11_0_4) OR FIREABLE(switch11_1_3) OR FIREABLE(switch11_2_3) OR FIREABLE(switch11_3_3) OR FIREABLE(switch11_4_3) OR FIREABLE(switch11_5_2) OR FIREABLE(switch11_6_2) OR FIREABLE(switch11_7_2) OR FIREABLE(switch11_0_3)))) U X ((FIREABLE(switch2_1_4) OR FIREABLE(switch2_0_5) OR FIREABLE(switch2_1_5) OR FIREABLE(switch2_0_4)))))) : A (((FIREABLE(switch8_1_7) OR FIREABLE(switch8_4_7) OR FIREABLE(switch8_5_7) OR FIREABLE(switch8_1_3) OR FIREABLE(switch8_4_3) OR FIREABLE(switch8_5_3) OR FIREABLE(switch8_0_6) OR FIREABLE(switch8_1_6) OR FIREABLE(switch8_4_6) OR FIREABLE(switch8_5_6) OR FIREABLE(switch8_0_7) OR FIREABLE(switch8_0_2) OR FIREABLE(switch8_4_2) OR FIREABLE(switch8_1_2) OR FIREABLE(switch8_0_3) OR FIREABLE(switch8_5_2)) U F (G (F ((FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(switch6_0_2))))))) : A ((G (((FIREABLE(switch2_1_4) OR FIREABLE(switch2_0_5) OR FIREABLE(switch2_1_5) OR FIREABLE(switch2_0_4)) U (FIREABLE(display1_2_1) OR FIREABLE(display1_1_1) OR FIREABLE(display1_4_1) OR FIREABLE(display1_3_1) OR FIREABLE(display1_6_0) OR FIREABLE(display1_5_0) OR FIREABLE(display1_0_1) OR FIREABLE(display1_7_0) OR FIREABLE(display1_2_2) OR FIREABLE(display1_1_2) OR FIREABLE(display1_4_2) OR FIREABLE(display1_3_2) OR FIREABLE(display1_6_1) OR FIREABLE(display1_5_1) OR FIREABLE(display1_0_2) OR FIREABLE(display1_7_1) OR FIREABLE(display1_1_0) OR FIREABLE(display1_2_0) OR FIREABLE(display1_3_0) OR FIREABLE(display1_4_0) OR FIREABLE(display1_0_0) OR FIREABLE(display1_7_5) OR FIREABLE(display1_0_6) OR FIREABLE(display1_5_5) OR FIREABLE(display1_6_5) OR FIREABLE(display1_3_6) OR FIREABLE(display1_4_6) OR FIREABLE(display1_1_6) OR FIREABLE(display1_2_6) OR FIREABLE(display1_7_4) OR FIREABLE(display1_0_5) OR FIREABLE(display1_5_4) OR FIREABLE(display1_6_4) OR FIREABLE(display1_3_5) OR FIREABLE(display1_4_5) OR FIREABLE(display1_1_5) OR FIREABLE(display1_2_5) OR FIREABLE(display1_0_4) OR FIREABLE(display1_7_3) OR FIREABLE(display1_6_3) OR FIREABLE(display1_5_3) OR FIREABLE(display1_4_4) OR FIREABLE(display1_3_4) OR FIREABLE(display1_2_4) OR FIREABLE(display1_1_4) OR FIREABLE(display1_0_3) OR FIREABLE(display1_7_2) OR FIREABLE(display1_6_2) OR FIREABLE(display1_5_2) OR FIREABLE(display1_4_3) OR FIREABLE(display1_3_3) OR FIREABLE(display1_2_3) OR FIREABLE(display1_1_3) OR FIREABLE(display1_6_7) OR FIREABLE(display1_5_7) OR FIREABLE(display1_7_7) OR FIREABLE(display1_6_6) OR FIREABLE(display1_5_6) OR FIREABLE(display1_0_7) OR FIREABLE(display1_7_6) OR FIREABLE(display1_2_7) OR FIREABLE(display1_1_7) OR FIREABLE(display1_4_7) OR FIREABLE(display1_3_7)))) U F ((FIREABLE(switch12_3_0) OR FIREABLE(switch12_4_0) OR FIREABLE(switch12_1_0) OR FIREABLE(switch12_2_0) OR FIREABLE(switch12_0_0) OR FIREABLE(switch12_0_6) OR FIREABLE(switch12_7_5) OR FIREABLE(switch12_6_5) OR FIREABLE(switch12_5_5) OR FIREABLE(switch12_4_6) OR FIREABLE(switch12_3_6) OR FIREABLE(switch12_2_6) OR FIREABLE(switch12_1_6) OR FIREABLE(switch12_0_5) OR FIREABLE(switch12_7_4) OR FIREABLE(switch12_6_4) OR FIREABLE(switch12_5_4) OR FIREABLE(switch12_4_5) OR FIREABLE(switch12_3_5) OR FIREABLE(switch12_2_5) OR FIREABLE(switch12_1_5) OR FIREABLE(switch12_7_7) OR FIREABLE(switch12_5_7) OR FIREABLE(switch12_6_7) OR FIREABLE(switch12_7_6) OR FIREABLE(switch12_0_7) OR FIREABLE(switch12_5_6) OR FIREABLE(switch12_6_6) OR FIREABLE(switch12_3_7) OR FIREABLE(switch12_4_7) OR FIREABLE(switch12_1_7) OR FIREABLE(switch12_2_7) OR FIREABLE(switch12_6_1) OR FIREABLE(switch12_5_1) OR FIREABLE(switch12_0_2) OR FIREABLE(switch12_7_1) OR FIREABLE(switch12_2_2) OR FIREABLE(switch12_1_2) OR FIREABLE(switch12_4_2) OR FIREABLE(switch12_3_2) OR FIREABLE(switch12_6_0) OR FIREABLE(switch12_5_0) OR FIREABLE(switch12_0_1) OR FIREABLE(switch12_7_0) OR FIREABLE(switch12_2_1) OR FIREABLE(switch12_1_1) OR FIREABLE(switch12_4_1) OR FIREABLE(switch12_3_1) OR FIREABLE(switch12_5_3) OR FIREABLE(switch12_6_3) OR FIREABLE(switch12_7_3) OR FIREABLE(switch12_0_4) OR FIREABLE(switch12_1_4) OR FIREABLE(switch12_2_4) OR FIREABLE(switch12_3_4) OR FIREABLE(switch12_4_4) OR FIREABLE(switch12_5_2) OR FIREABLE(switch12_6_2) OR FIREABLE(switch12_7_2) OR FIREABLE(switch12_0_3) OR FIREABLE(switch12_1_3) OR FIREABLE(switch12_2_3) OR FIREABLE(switch12_3_3) OR FIREABLE(switch12_4_3))))) : A (G (G (F (FIREABLE(display1_2_1))))) : A (X (FIREABLE(display4_7_6))) : A (((FIREABLE(switch7_0_6) U FIREABLE(switch11_4_4)) U F (X (G (FIREABLE(display4_6_2)))))) : A ((G (F (F (FIREABLE(switch12_3_0)))) U G (FIREABLE(display4_0_1)))) : A ((G (G (X (FIREABLE(switch9_3_0)))) U F (F (G (FIREABLE(display4_5_1)))))) : A (X (((FIREABLE(switch5_1_7) U FIREABLE(switch6_4_2)) U G (F (FIREABLE(switch9_7_3)))))) : A (FIREABLE(display2_2_6)) : A (G (X (FIREABLE(switch5_0_3))))

lola: rewrite Frontend/Parser/formula_rewrite.k:151

lola: rewrite Frontend/Parser/formula_rewrite.k:151

lola: rewrite Frontend/Parser/formula_rewrite.k:151

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:425

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:431

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:434

lola: rewrite Frontend/Parser/formula_rewrite.k:356

lola: rewrite Frontend/Parser/formula_rewrite.k:371

lola: rewrite Frontend/Parser/formula_rewrite.k:425

lola: rewrite Frontend/Parser/formula_rewrite.k:437

lola: rewrite Frontend/Parser/formula_rewrite.k:522

lola: rewrite Frontend/Parser/formula_rewrite.k:431

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:350

lola: rewrite Frontend/Parser/formula_rewrite.k:356

lola: rewrite Frontend/Parser/formula_rewrite.k:380

lola: rewrite Frontend/Parser/formula_rewrite.k:422

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:431

lola: rewrite Frontend/Parser/formula_rewrite.k:353

lola: rewrite Frontend/Parser/formula_rewrite.k:353

lola: rewrite Frontend/Parser/formula_rewrite.k:350

lola: rewrite Frontend/Parser/formula_rewrite.k:347

lola: rewrite Frontend/Parser/formula_rewrite.k:422

lola: rewrite Frontend/Parser/formula_rewrite.k:425

lola: rewrite Frontend/Parser/formula_rewrite.k:377

lola: rewrite Frontend/Parser/formula_rewrite.k:151

lola: rewrite Frontend/Parser/formula_rewrite.k:353

lola: computing a collection of formulas

lola: RUNNING

lola: subprocess 0 will run for 223 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: (FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking initial satisfaction

lola: processed formula: (FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(... (shortened)

lola: processed formula length: 413

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: processed formula with 0 atomic propositions

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: preprocessing

lola: The net violates the given property already in its initial state.

lola: 0 markings, 0 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-0 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 1 will run for 238 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: (FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking initial satisfaction

lola: processed formula: (FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR FIREABLE(... (shortened)

lola: processed formula length: 413

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: processed formula with 0 atomic propositions

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: preprocessing

lola: The net violates the given property already in its initial state.

lola: 0 markings, 0 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-1 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 2 will run for 255 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: (FIREABLE(switch5_5_2) OR FIREABLE(switch5_0_3) OR FIREABLE(switch5_1_2) OR FIREABLE(switch5_4_2) OR FIREABLE(switch5_0_2) OR FIREABLE(switch5_4_7) OR FIREABLE(switch5_1_7) OR FIREABLE(switch5_5_7) OR FIREABLE(switch5_4_6) OR FIREABLE(switch5_1_6) OR FIREABLE(switch5_0_7) OR FIREABLE(switch5_5_6) OR FIREABLE(switch5_4_3) OR FIREABLE(switch5_1_3) OR FIREABLE(switch5_0_6) OR FIREABLE(... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking initial satisfaction

lola: processed formula: (FIREABLE(switch5_5_2) OR FIREABLE(switch5_0_3) OR FIREABLE(switch5_1_2) OR FIREABLE(switch5_4_2) OR FIREABLE(switch5_0_2) OR FIREABLE(switch5_4_7) OR FIREABLE(switch5_1_7) OR FIREABLE(switch5_5_7) OR FIREABLE(switch5_4_6) OR FIREABLE(switch5_1_6) OR FIREABLE(switch5_0_7) OR FIREABLE(switch5_5_6) OR FIREABLE(switch5_4_3) OR FIREABLE(switch5_1_3) OR FIREABLE(switch5_0_6) OR FIREABLE(... (shortened)

lola: processed formula length: 413

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: processed formula with 0 atomic propositions

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: preprocessing

lola: The net violates the given property already in its initial state.

lola: 0 markings, 0 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-2 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 3 will run for 274 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: FIREABLE(display2_2_6)

lola: ========================================

lola: SUBTASK

lola: checking initial satisfaction

lola: processed formula: FIREABLE(display2_2_6)

lola: processed formula length: 22

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: processed formula with 0 atomic propositions

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: preprocessing

lola: The net violates the given property already in its initial state.

lola: 0 markings, 0 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-14 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 4 will run for 297 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (X (FIREABLE(display4_7_6)))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (X (FIREABLE(display4_7_6)))

lola: processed formula length: 30

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 3 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: Formula contains X operator; stubborn sets not applicable

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 81 markings, 81 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-9 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 5 will run for 324 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (X (F ((FIREABLE(switch2_1_4) OR FIREABLE(switch2_0_5) OR FIREABLE(switch2_1_5) OR FIREABLE(switch2_0_4)))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (X (F ((FIREABLE(switch2_1_4) OR FIREABLE(switch2_0_5) OR FIREABLE(switch2_1_5) OR FIREABLE(switch2_0_4)))))

lola: processed formula length: 113

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: Formula contains X operator; stubborn sets not applicable

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: yes

lola: produced by: LTL model checker

lola: The net satisfies the given formula (language of the product automaton is empty).

lola: 5 markings, 4 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-5 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 6 will run for 357 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (X (G (FIREABLE(switch5_0_3))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (X (G (FIREABLE(switch5_0_3))))

lola: processed formula length: 33

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 3 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: Formula contains X operator; stubborn sets not applicable

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 81 markings, 81 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-15 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 7 will run for 396 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (F (G (FIREABLE(display4_5_1))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (F (G (FIREABLE(display4_5_1))))

lola: processed formula length: 34

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 82 markings, 83 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-12 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 8 will run for 446 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (G (F (FIREABLE(switch9_7_3))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (G (F (FIREABLE(switch9_7_3))))

lola: processed formula length: 33

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 81 markings, 81 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-13 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 9 will run for 510 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (G (F (FIREABLE(display1_2_1))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (G (F (FIREABLE(display1_2_1))))

lola: processed formula length: 34

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 81 markings, 81 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-8 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 10 will run for 595 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (F (G (FIREABLE(display4_6_2))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (F (G (FIREABLE(display4_6_2))))

lola: processed formula length: 34

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 82 markings, 83 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-10 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 11 will run for 714 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A ((G (FIREABLE(display4_0_1)) OR (G (F (FIREABLE(switch12_3_0))) AND F (G (FIREABLE(display4_0_1))))))

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A ((G (FIREABLE(display4_0_1)) OR (G (F (FIREABLE(switch12_3_0))) AND F (G (FIREABLE(display4_0_1))))))

lola: processed formula length: 103

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 8 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: LTL model checker

lola: The net does not satisfy the given formula (language of the product automaton is nonempty).

lola: 81 markings, 81 edges

lola: ========================================

FORMULA PermAdmissibility-PT-05-LTLFireability-11 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT TOPOLOGICAL STATE_COMPRESSION STUBBORN_SETS USE_NUPN UNFOLDING_TO_PT

lola: subprocess 12 will run for 892 seconds at most (--localtimelimit=0)

lola: ========================================

lola: ...considering subproblem: A (G (F ((FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR ... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking LTL

lola: transforming LTL-Formula into a Büchi-Automaton

lola: processed formula: A (G (F ((FIREABLE(switch6_5_7) OR FIREABLE(switch6_1_7) OR FIREABLE(switch6_4_7) OR FIREABLE(switch6_5_6) OR FIREABLE(switch6_0_7) OR FIREABLE(switch6_1_6) OR FIREABLE(switch6_4_6) OR FIREABLE(switch6_5_3) OR FIREABLE(switch6_0_6) OR FIREABLE(switch6_1_3) OR FIREABLE(switch6_4_3) OR FIREABLE(switch6_0_3) OR FIREABLE(switch6_5_2) OR FIREABLE(switch6_4_2) OR FIREABLE(switch6_1_2) OR ... (shortened)

lola: processed formula length: 425

lola: 32 rewrites

lola: closed formula file PermAdmissibility-PT-05-LTLFireability.task

lola: the resulting Büchi automaton has 2 states

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: using ltl preserving stubborn set method (--stubborn)

lola: SEARCH

lola: RUNNING

lola: 1399594 markings, 1970998 edges, 279919 markings/sec, 0 secs

lola: 2796826 markings, 3990879 edges, 279446 markings/sec, 5 secs

lola: 4161027 markings, 6073798 edges, 272840 markings/sec, 10 secs

lola: 5633514 markings, 7777392 edges, 294497 markings/sec, 15 secs

lola: 7065172 markings, 9425784 edges, 286332 markings/sec, 20 secs

lola: 8446959 markings, 11126890 edges, 276357 markings/sec, 25 secs

lola: 9828118 markings, 12756322 edges, 276232 markings/sec, 30 secs

lola: 11102001 markings, 14423141 edges, 254777 markings/sec, 35 secs

lola: 12523250 markings, 16044549 edges, 284250 markings/sec, 40 secs

lola: 13801055 markings, 17753865 edges, 255561 markings/sec, 45 secs

lola: 15123421 markings, 19395608 edges, 264473 markings/sec, 50 secs

lola: 16383697 markings, 21077692 edges, 252055 markings/sec, 55 secs

lola: 17601418 markings, 22778123 edges, 243544 markings/sec, 60 secs

lola: 18869005 markings, 24529564 edges, 253517 markings/sec, 65 secs

lola: 20174929 markings, 26208930 edges, 261185 markings/sec, 70 secs

lola: 21448422 markings, 27867371 edges, 254699 markings/sec, 75 secs

lola: 22660376 markings, 29579791 edges, 242391 markings/sec, 80 secs

lola: 23812718 markings, 31368688 edges, 230468 markings/sec, 85 secs

lola: 25195410 markings, 33024944 edges, 276538 markings/sec, 90 secs

lola: 26469261 markings, 34738579 edges, 254770 markings/sec, 95 secs

lola: 27695190 markings, 36413215 edges, 245186 markings/sec, 100 secs

lola: 28871598 markings, 38169692 edges, 235282 markings/sec, 105 secs

lola: 30058653 markings, 39900149 edges, 237411 markings/sec, 110 secs

lola: 31228885 markings, 41569499 edges, 234046 markings/sec, 115 secs

lola: 32448633 markings, 43065522 edges, 243950 markings/sec, 120 secs

lola: 33690452 markings, 44498097 edges, 248364 markings/sec, 125 secs

lola: 34912142 markings, 45879400 edges, 244338 markings/sec, 130 secs

lola: 36121518 markings, 47263333 edges, 241875 markings/sec, 135 secs

lola: 37336854 markings, 48684571 edges, 243067 markings/sec, 140 secs

lola: 38587982 markings, 50165478 edges, 250226 markings/sec, 145 secs

lola: 39781065 markings, 51601734 edges, 238617 markings/sec, 150 secs

lola: 40991318 markings, 53077113 edges, 242051 markings/sec, 155 secs

lola: 42194209 markings, 54577888 edges, 240578 markings/sec, 160 secs

lola: 43370154 markings, 56080498 edges, 235189 markings/sec, 165 secs

lola: 44554077 markings, 57650763 edges, 236785 markings/sec, 170 secs

lola: 45737678 markings, 59262609 edges, 236720 markings/sec, 175 secs

lola: 46954257 markings, 60719552 edges, 243316 markings/sec, 180 secs

lola: 48190543 markings, 62102848 edges, 247257 markings/sec, 185 secs

lola: 49400957 markings, 63464372 edges, 242083 markings/sec, 190 secs

lola: 50647115 markings, 64878573 edges, 249232 markings/sec, 195 secs

lola: 51864697 markings, 66316816 edges, 243516 markings/sec, 200 secs

lola: 53073504 markings, 67751926 edges, 241761 markings/sec, 205 secs

lola: 54276820 markings, 69207344 edges, 240663 markings/sec, 210 secs

lola: 55445134 markings, 70672952 edges, 233663 markings/sec, 215 secs

lola: 56618614 markings, 72185351 edges, 234696 markings/sec, 220 secs

lola: 57809993 markings, 73750343 edges, 238276 markings/sec, 225 secs

lola: 59039114 markings, 75116314 edges, 245824 markings/sec, 230 secs

lola: 60279128 markings, 76493824 edges, 248003 markings/sec, 235 secs

lola: 61535940 markings, 77890731 edges, 251362 markings/sec, 240 secs

lola: 62791135 markings, 79324833 edges, 251039 markings/sec, 245 secs

lola: 64002203 markings, 80743844 edges, 242214 markings/sec, 250 secs

lola: 65222654 markings, 82178929 edges, 244090 markings/sec, 255 secs

lola: 66472459 markings, 83643024 edges, 249961 markings/sec, 260 secs

lola: 67657693 markings, 85093206 edges, 237047 markings/sec, 265 secs

lola: 68835141 markings, 86552253 edges, 235490 markings/sec, 270 secs

lola: 70010618 markings, 88053930 edges, 235095 markings/sec, 275 secs

lola: 71191263 markings, 89611596 edges, 236129 markings/sec, 280 secs

lola: 72375537 markings, 90982038 edges, 236855 markings/sec, 285 secs

lola: 73591777 markings, 92374882 edges, 243248 markings/sec, 290 secs

lola: 74779159 markings, 93803260 edges, 237476 markings/sec, 295 secs

lola: 75942608 markings, 95323275 edges, 232690 markings/sec, 300 secs

lola: 77133985 markings, 96701255 edges, 238275 markings/sec, 305 secs

lola: 78353514 markings, 98076320 edges, 243906 markings/sec, 310 secs

lola: 79538699 markings, 99483975 edges, 237037 markings/sec, 315 secs

lola: 80721067 markings, 100922329 edges, 236474 markings/sec, 320 secs

lola: 81866948 markings, 102424655 edges, 229176 markings/sec, 325 secs

lola: 83047976 markings, 103841093 edges, 236206 markings/sec, 330 secs

lola: 84200946 markings, 105216095 edges, 230594 markings/sec, 335 secs

lola: 85387166 markings, 106557790 edges, 237244 markings/sec, 340 secs

BK_STOP 1553039432079

--------------------

content from stderr:

Killed

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="PermAdmissibility-PT-05"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="win2018"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3954"

echo " Executing tool win2018"

echo " Input is PermAdmissibility-PT-05, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r110-oct2-155272242300147"

echo "====================================================================="

echo

echo "--------------------"

echo "preparation of the directory to be used:"

tar xzf /home/mcc/BenchKit/INPUTS/PermAdmissibility-PT-05.tgz

mv PermAdmissibility-PT-05 execution

cd execution

if [ "LTLFireability" = "GlobalProperties" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

if [ "LTLFireability" = "UpperBounds" ] ; then

rm -f GenericPropertiesVerdict.xml

fi

pwd

ls -lh

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;