About the Execution of ITS-Tools.L for ASLink-PT-09a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15751.780 | 91582.00 | 190454.00 | 490.90 | T | normal |

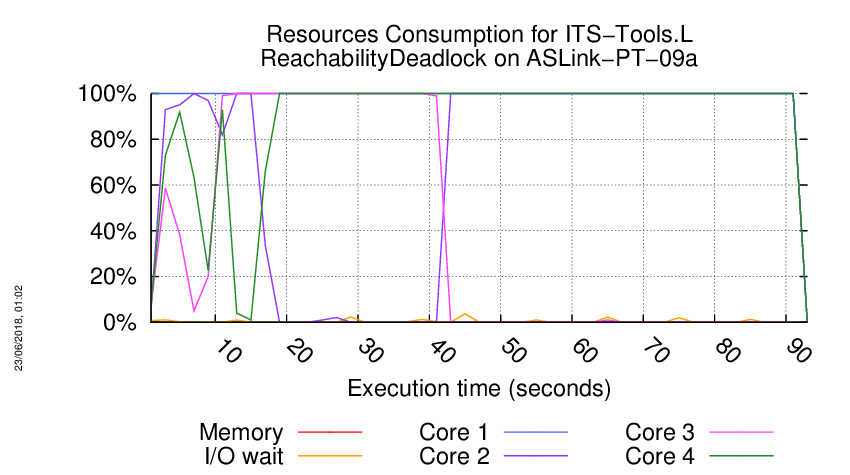

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

...................

/home/mcc/execution

total 1004K

-rw-r--r-- 1 mcc users 3.0K May 29 16:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 17K May 29 16:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.7K May 28 11:15 CTLFireability.txt

-rw-r--r-- 1 mcc users 19K May 28 11:15 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 24 11:17 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.6K May 24 11:17 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 28 09:24 LTLCardinality.txt

-rw-r--r-- 1 mcc users 11K May 28 09:24 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.7K May 28 07:38 LTLFireability.txt

-rw-r--r-- 1 mcc users 7.6K May 28 07:38 LTLFireability.xml

-rw-r--r-- 1 mcc users 1 May 24 11:17 NewModel

-rw-r--r-- 1 mcc users 2.9K May 27 05:08 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 14K May 27 05:08 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 104 May 26 06:29 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 342 May 26 06:29 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.7K May 26 06:35 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K May 26 06:35 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 28 07:31 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 28 07:31 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 24 11:17 equiv_col

-rw-r--r-- 1 mcc users 4 May 24 11:17 instance

-rw-r--r-- 1 mcc users 6 May 24 11:17 iscolored

-rw-r--r-- 1 mcc users 839K May 24 11:17 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstoolsl

Input is ASLink-PT-09a, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r273-smll-152749149600152

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ASLink-PT-09a-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1527870724668

Flatten gal took : 684 ms

Constant places removed 37 places and 1 transitions.

Reduce isomorphic transitions removed 31 transitions.

Implicit places reduction removed 18 places :[p1848, p1781, p1586, p1574, p1391, p1379, p1196, p1184, p1001, p989, p806, p794, p611, p599, p416, p404, p221, p209]

Performed 381 Post agglomeration using F-continuation condition.

Iterating post reduction 0 with 467 rules applied. Total rules applied 467 place count 1936 transition count 2506

Constant places removed 474 places and 0 transitions.

Performed 29 Post agglomeration using F-continuation condition.

Iterating post reduction 1 with 503 rules applied. Total rules applied 970 place count 1462 transition count 2477

Constant places removed 30 places and 0 transitions.

Implicit places reduction removed 10 places :[p1758, p1563, p1368, p1173, p978, p783, p588, p393, p206, p199]

Performed 10 Post agglomeration using F-continuation condition.

Iterating post reduction 2 with 50 rules applied. Total rules applied 1020 place count 1422 transition count 2467

Constant places removed 10 places and 0 transitions.

Iterating post reduction 3 with 10 rules applied. Total rules applied 1030 place count 1412 transition count 2467

Performed 36 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 4 with 36 Pre rules applied. Total rules applied 1030 place count 1412 transition count 2431

Constant places removed 36 places and 0 transitions.

Iterating post reduction 4 with 36 rules applied. Total rules applied 1066 place count 1376 transition count 2431

Symmetric choice reduction at 5 with 21 rule applications. Total rules 1087 place count 1376 transition count 2431

Constant places removed 21 places and 74 transitions.

Reduce isomorphic transitions removed 2 transitions.

Implicit places reduction removed 12 places :[p1990, p1851, p1749, p1554, p1359, p1164, p969, p774, p579, p384, p190, p23]

Performed 13 Post agglomeration using F-continuation condition.

Iterating post reduction 5 with 48 rules applied. Total rules applied 1135 place count 1343 transition count 2342

Constant places removed 13 places and 0 transitions.

Iterating post reduction 6 with 13 rules applied. Total rules applied 1148 place count 1330 transition count 2342

Symmetric choice reduction at 7 with 10 rule applications. Total rules 1158 place count 1330 transition count 2342

Constant places removed 10 places and 17 transitions.

Iterating post reduction 7 with 10 rules applied. Total rules applied 1168 place count 1320 transition count 2325

Symmetric choice reduction at 8 with 1 rule applications. Total rules 1169 place count 1320 transition count 2325

Constant places removed 1 places and 8 transitions.

Iterating post reduction 8 with 1 rules applied. Total rules applied 1170 place count 1319 transition count 2317

Symmetric choice reduction at 9 with 1 rule applications. Total rules 1171 place count 1319 transition count 2317

Constant places removed 1 places and 8 transitions.

Iterating post reduction 9 with 1 rules applied. Total rules applied 1172 place count 1318 transition count 2309

Symmetric choice reduction at 10 with 1 rule applications. Total rules 1173 place count 1318 transition count 2309

Constant places removed 1 places and 8 transitions.

Iterating post reduction 10 with 1 rules applied. Total rules applied 1174 place count 1317 transition count 2301

Symmetric choice reduction at 11 with 1 rule applications. Total rules 1175 place count 1317 transition count 2301

Constant places removed 1 places and 8 transitions.

Iterating post reduction 11 with 1 rules applied. Total rules applied 1176 place count 1316 transition count 2293

Symmetric choice reduction at 12 with 1 rule applications. Total rules 1177 place count 1316 transition count 2293

Constant places removed 1 places and 8 transitions.

Iterating post reduction 12 with 1 rules applied. Total rules applied 1178 place count 1315 transition count 2285

Symmetric choice reduction at 13 with 1 rule applications. Total rules 1179 place count 1315 transition count 2285

Constant places removed 1 places and 8 transitions.

Iterating post reduction 13 with 1 rules applied. Total rules applied 1180 place count 1314 transition count 2277

Symmetric choice reduction at 14 with 1 rule applications. Total rules 1181 place count 1314 transition count 2277

Constant places removed 1 places and 8 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 1182 place count 1313 transition count 2269

Symmetric choice reduction at 15 with 1 rule applications. Total rules 1183 place count 1313 transition count 2269

Constant places removed 1 places and 8 transitions.

Iterating post reduction 15 with 1 rules applied. Total rules applied 1184 place count 1312 transition count 2261

Symmetric choice reduction at 16 with 1 rule applications. Total rules 1185 place count 1312 transition count 2261

Constant places removed 1 places and 8 transitions.

Iterating post reduction 16 with 1 rules applied. Total rules applied 1186 place count 1311 transition count 2253

Symmetric choice reduction at 17 with 1 rule applications. Total rules 1187 place count 1311 transition count 2253

Constant places removed 1 places and 8 transitions.

Iterating post reduction 17 with 1 rules applied. Total rules applied 1188 place count 1310 transition count 2245

Symmetric choice reduction at 18 with 1 rule applications. Total rules 1189 place count 1310 transition count 2245

Constant places removed 1 places and 8 transitions.

Iterating post reduction 18 with 1 rules applied. Total rules applied 1190 place count 1309 transition count 2237

Symmetric choice reduction at 19 with 1 rule applications. Total rules 1191 place count 1309 transition count 2237

Constant places removed 1 places and 8 transitions.

Iterating post reduction 19 with 1 rules applied. Total rules applied 1192 place count 1308 transition count 2229

Symmetric choice reduction at 20 with 1 rule applications. Total rules 1193 place count 1308 transition count 2229

Constant places removed 1 places and 8 transitions.

Iterating post reduction 20 with 1 rules applied. Total rules applied 1194 place count 1307 transition count 2221

Symmetric choice reduction at 21 with 1 rule applications. Total rules 1195 place count 1307 transition count 2221

Constant places removed 1 places and 8 transitions.

Iterating post reduction 21 with 1 rules applied. Total rules applied 1196 place count 1306 transition count 2213

Symmetric choice reduction at 22 with 1 rule applications. Total rules 1197 place count 1306 transition count 2213

Constant places removed 1 places and 8 transitions.

Iterating post reduction 22 with 1 rules applied. Total rules applied 1198 place count 1305 transition count 2205

Performed 28 Post agglomeration using F-continuation condition.

Constant places removed 28 places and 0 transitions.

Iterating post reduction 23 with 28 rules applied. Total rules applied 1226 place count 1277 transition count 2177

Applied a total of 1226 rules in 2277 ms. Remains 1277 /1991 variables (removed 714) and now considering 2177/2919 (removed 742) transitions.

// Phase 1: matrix 2177 rows 1277 cols

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK

No direction supplied, using forward translation only.

built 107 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 8 ordering constraints for composite.

built 58 ordering constraints for composite.

built 12 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 4 ordering constraints for composite.

built 100 ordering constraints for composite.

Compilation finished in 31160 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 80 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,6.36884e+33,78.5218,1439732,6601,586,2.73397e+06,1874,3635,3.6067e+06,150,12144,0

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

dead,1.79874e+23,80.1151,1439732,1564,232,2.73397e+06,7042,10812,3.6067e+06,824,18798,263693

System contains 1.79874e+23 deadlocks (shown below if less than --print-limit option) !

FORMULA ASLink-PT-09a-ReachabilityDeadlock-0 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL USE_NUPN

[ u322={[ p1852=1 ]

} u320={[ p1824=1 ]

} i70={[ u359={[ p1983=1 ]

} u358={[ p1979=1 ]

} u357={[ ]

} u356={[ ]

} u352={[ ]

} u351={[ ]

} u350={[ ]

} u349={[ ]

} u348={[ ]

} u346={[ ]

} u347={[ ]

} u345={[ ]

} u344={[ ]

} u386={[ ]

} u343={[ ]

} u342={[ ]

} u341={[ ]

} u340={[ ]

} u339={[ ]

} u337={[ ]

} u338={[ ]

} u336={[ ]

} u335={[ ]

} u334={[ ]

} u325={[ ]

} u324={[ ]

} u333={[ ]

} u332={[ ]

} u331={[ ]

} u327={[ ]

} u330={[ ]

} u326={[ ]

} u329={[ ]

} u328={[ ]

} ]

[ u359={[ ]

} u358={[ ]

} u357={[ p1977=1 ]

} u356={[ p1972=1 ]

} u352={[ ]

} u351={[ ]

} u350={[ ]

} u349={[ ]

} u348={[ ]

} u346={[ ]

} u347={[ ]

} u345={[ ]

} u344={[ ]

} u386={[ ]

} u343={[ ]

} u342={[ ]

} u341={[ ]

} u340={[ ]

} u339={[ ]

} u337={[ ]

} u338={[ ]

} u336={[ ]

} u335={[ ]

} u334={[ ]

} u325={[ ]

} u324={[ ]

} u333={[ ]

} u332={[ ]

} u331={[ ]

} u327={[ ]

} u330={[ ]

} u326={[ ]

} u329={[ ]

} u328={[ ]

} ]

[ u359={[ ]

} u358={[ ]

} u357={[ ]

} u356={[ ]

} u352={[ p1964=1 ]

} u351={[ p1960=1 ]

} u350={[ ]

} u349={[ ]

} u348={[ ]

} u346={[ ]

} u347={[ ]

} u345={[ ]

} u344={[ ]

} u386={[ ]

} u343={[ ]

} u342={[ ]

} u341={[ ]

} u340={[ ]

} u339={[ ]

} u337={[ ]

} u338={[ ]

} u336={[ ]

} u335={[ ]

} u334={[ ]

} u325={[ ]

} u324={[ ]

} u333={[ ]

} u332={[ ]

} u331={[ ]

} u327={[ ]

} u330={[ ]

} u326={[ ]

} u329={[ ]

} u328={[ ]

} ]

[ u359={[ ]

} u358={[ ]

} u357={[ ]

} u356={[ ]

} u352={[ ]

} u351={[ ]

} u350={[ p1958=1 ]

} u349={[ p1954=1 ]

} u348={[ ]

} u346={[ ]

} u347={[ ]

} u345={[ ]

} u344={[ ]

} u386={[ ]

} u343={[ ]

} u342={[ ]

} u341={[ ]

} u340={[ ]

} u339={[ ]

} u337={[ ]

} u338={[ ]

} u336={[ ]

} u335={[ ]

} u334={[ ]

} u325={[ ]

} u324={[ ]

} u333={[ ]

} u332={[ ]

} u331={[ ]

} u327={[ ]

} u330={[ ]

} u326={[ ]

} u329={[ ]

} u328={[ ]

} ]

[ u359={[ ]

} u358={[ ]

} u357={[ ]

} u356={[ ]

} u352={[ ]

} u351={[ ]

} u350={[ ]

} u349={[ ]

} u348={[ p1952=1 ]

} u346={[ p1945=1 ]

} u347={[ p1948=1 ]

} u345={[ ]

} u344={[ ]

} u386={[ ]

} u343={[ ]

} u342={[ ]

} u341={[ ]

} u340={[ ]

} u339={[ ]

} u337={[ ]

} u338={[ ]

} u336={[ ]

} u335={[ ]

} u334={[ ]

} u325={[ ]

} u324={[ ]

} u333={[ ]

} u332={[ ]

} u331={[ ]

} u327={[ ]

} u330={[ ]

} u326={[ ]

} u329={[ ]

} u328={[ ]

} ]

} u319={[ p1806=1 ]

} u321={[ p1849=1 ]

} u284={[ p1596=1 ]

} u315={[ p1779=1 ]

} u285={[ p1613=1 ]

} i62={[ u311={[ ]

} u309={[ ]

} u303={[ ]

} u368={[ ]

} u298={[ ]

} i7={[ u384={[ ]

} u307={[ ]

} ]

} i5={[ u364={[ ]

} u302={[ ]

} ]

} u293={[ p1693=1 ]

} u288={[ ]

} i3={[ u365={[ p1696=1 ]

} u297={[ ]

} ]

} i1={[ u369={[ ]

} u292={[ ]

} ]

} ]

[ u311={[ ]

} u309={[ ]

} u303={[ ]

} u368={[ ]

} u298={[ ]

} i7={[ u384={[ ]

} u307={[ ]

} ]

} i5={[ u364={[ ]

} u302={[ ]

} ]

} u293={[ ]

} u288={[ p1659=1 ]

} i3={[ u365={[ ]

} u297={[ ]

} ]

} i1={[ u369={[ p1662=1 ]

} u292={[ ]

} ]

} ]

[ u311={[ ]

} u309={[ ]

} u303={[ ]

} u368={[ ]

} u298={[ p1715=1 ]

} i7={[ u384={[ ]

} u307={[ ]

} ]

} i5={[ u364={[ p1718=1 ]

} u302={[ ]

} ]

} u293={[ ]

} u288={[ ]

} i3={[ u365={[ ]

} u297={[ ]

} ]

} i1={[ u369={[ ]

} u292={[ ]

} ]

} ]

[ u311={[ ]

} u309={[ ]

} u303={[ p1735=1 ]

} u368={[ ]

} u298={[ ]

} i7={[ u384={[ p1738=1 ]

} u307={[ ]

} ]

} i5={[ u364={[ ]

} u302={[ ]

} ]

} u293={[ ]

} u288={[ ]

} i3={[ u365={[ ]

} u297={[ ]

} ]

} i1={[ u369={[ ]

} u292={[ ]

} ]

} ]

} u318={[ p1788=1 ]

} u286={[ p1631=1 ]

} u249={[ p1401=1 ]

} i63={[ u383={[ ]

} u314={[ p1767=1 ]

} u313={[ p1764=1 ]

} ]

} u250={[ p1418=1 ]

} i55={[ u276={[ ]

} u274={[ ]

} u268={[ p1541=1 ]

} u399={[ ]

} u263={[ ]

} i7={[ u412={[ p1543=1 ]

} u272={[ ]

} ]

} i5={[ u415={[ ]

} u267={[ ]

} ]

} u258={[ ]

} u253={[ ]

} i3={[ u416={[ ]

} u262={[ ]

} ]

} i1={[ u398={[ ]

} u257={[ ]

} ]

} ]

[ u276={[ ]

} u274={[ ]

} u268={[ ]

} u399={[ ]

} u263={[ ]

} i7={[ u412={[ ]

} u272={[ ]

} ]

} i5={[ u415={[ ]

} u267={[ ]

} ]

} u258={[ p1499=1 ]

} u253={[ ]

} i3={[ u416={[ p1501=1 ]

} u262={[ ]

} ]

} i1={[ u398={[ ]

} u257={[ ]

} ]

} ]

[ u276={[ ]

} u274={[ ]

} u268={[ ]

} u399={[ ]

} u263={[ ]

} i7={[ u412={[ ]

} u272={[ ]

} ]

} i5={[ u415={[ ]

} u267={[ ]

} ]

} u258={[ ]

} u253={[ p1465=1 ]

} i3={[ u416={[ ]

} u262={[ ]

} ]

} i1={[ u398={[ p1467=1 ]

} u257={[ ]

} ]

} ]

[ u276={[ ]

} u274={[ ]

} u268={[ ]

} u399={[ ]

} u263={[ p1521=1 ]

} i7={[ u412={[ ]

} u272={[ ]

} ]

} i5={[ u415={[ p1523=1 ]

} u267={[ ]

} ]

} u258={[ ]

} u253={[ ]

} i3={[ u416={[ ]

} u262={[ ]

} ]

} i1={[ u398={[ ]

} u257={[ ]

} ]

} ]

} u280={[ p1577=1 ]

} u283={[ p1593=1 ]

} u251={[ p1436=1 ]

} u214={[ p1206=1 ]

} i56={[ u408={[ ]

} u279={[ ]

} u278={[ p1569=1 ]

} ]

} u215={[ p1223=1 ]

} i48={[ u241={[ ]

} u239={[ ]

} u233={[ p1346=1 ]

} u396={[ ]

} u228={[ ]

} i7={[ u389={[ p1348=1 ]

} u237={[ ]

} ]

} i5={[ u390={[ ]

} u232={[ ]

} ]

} u223={[ ]

} u218={[ ]

} i3={[ u393={[ ]

} u227={[ ]

} ]

} i1={[ u395={[ ]

} u222={[ ]

} ]

} ]

[ u241={[ ]

} u239={[ ]

} u233={[ ]

} u396={[ ]

} u228={[ ]

} i7={[ u389={[ ]

} u237={[ ]

} ]

} i5={[ u390={[ ]

} u232={[ ]

} ]

} u223={[ p1304=1 ]

} u218={[ ]

} i3={[ u393={[ p1306=1 ]

} u227={[ ]

} ]

} i1={[ u395={[ ]

} u222={[ ]

} ]

} ]

[ u241={[ ]

} u239={[ ]

} u233={[ ]

} u396={[ ]

} u228={[ ]

} i7={[ u389={[ ]

} u237={[ ]

} ]

} i5={[ u390={[ ]

} u232={[ ]

} ]

} u223={[ ]

} u218={[ p1270=1 ]

} i3={[ u393={[ ]

} u227={[ ]

} ]

} i1={[ u395={[ p1272=1 ]

} u222={[ ]

} ]

} ]

[ u241={[ ]

} u239={[ ]

} u233={[ ]

} u396={[ ]

} u228={[ p1326=1 ]

} i7={[ u389={[ ]

} u237={[ ]

} ]

} i5={[ u390={[ p1328=1 ]

} u232={[ ]

} ]

} u223={[ ]

} u218={[ ]

} i3={[ u393={[ ]

} u227={[ ]

} ]

} i1={[ u395={[ ]

} u222={[ ]

} ]

} ]

} u245={[ p1382=1 ]

} u248={[ p1398=1 ]

} u216={[ p1241=1 ]

} i49={[ u403={[ ]

} u244={[ ]

} u243={[ p1374=1 ]

} ]

} u179={[ p1011=1 ]

} u180={[ p1028=1 ]

} u210={[ p1193=1 ]

} i41={[ u206={[ ]

} u204={[ ]

} u198={[ ]

} u379={[ ]

} u193={[ ]

} i7={[ u375={[ ]

} u202={[ ]

} ]

} i5={[ u374={[ ]

} u197={[ ]

} ]

} u188={[ p1108=1 ]

} u183={[ ]

} i3={[ u381={[ p1111=1 ]

} u192={[ ]

} ]

} i1={[ u382={[ ]

} u187={[ ]

} ]

} ]

[ u206={[ ]

} u204={[ ]

} u198={[ ]

} u379={[ ]

} u193={[ ]

} i7={[ u375={[ ]

} u202={[ ]

} ]

} i5={[ u374={[ ]

} u197={[ ]

} ]

} u188={[ ]

} u183={[ p1074=1 ]

} i3={[ u381={[ ]

} u192={[ ]

} ]

} i1={[ u382={[ p1077=1 ]

} u187={[ ]

} ]

} ]

[ u206={[ ]

} u204={[ ]

} u198={[ ]

} u379={[ ]

} u193={[ p1130=1 ]

} i7={[ u375={[ ]

} u202={[ ]

} ]

} i5={[ u374={[ p1133=1 ]

} u197={[ ]

} ]

} u188={[ ]

} u183={[ ]

} i3={[ u381={[ ]

} u192={[ ]

} ]

} i1={[ u382={[ ]

} u187={[ ]

} ]

} ]

[ u206={[ ]

} u204={[ ]

} u198={[ p1150=1 ]

} u379={[ ]

} u193={[ ]

} i7={[ u375={[ p1153=1 ]

} u202={[ ]

} ]

} i5={[ u374={[ ]

} u197={[ ]

} ]

} u188={[ ]

} u183={[ ]

} i3={[ u381={[ ]

} u192={[ ]

} ]

} i1={[ u382={[ ]

} u187={[ ]

} ]

} ]

} u213={[ p1203=1 ]

} u181={[ p1046=1 ]

} i42={[ u385={[ ]

} u209={[ p1182=1 ]

} u208={[ p1179=1 ]

} ]

} u144={[ p816=1 ]

} u145={[ p833=1 ]

} u175={[ p998=1 ]

} i34={[ u171={[ ]

} u169={[ ]

} u163={[ ]

} u414={[ ]

} u158={[ ]

} i7={[ u370={[ ]

} u167={[ ]

} ]

} i5={[ u372={[ ]

} u162={[ ]

} ]

} u153={[ p913=1 ]

} u148={[ ]

} i3={[ u409={[ p916=1 ]

} u157={[ ]

} ]

} i1={[ u410={[ ]

} u152={[ ]

} ]

} ]

[ u171={[ ]

} u169={[ ]

} u163={[ ]

} u414={[ ]

} u158={[ ]

} i7={[ u370={[ ]

} u167={[ ]

} ]

} i5={[ u372={[ ]

} u162={[ ]

} ]

} u153={[ ]

} u148={[ p879=1 ]

} i3={[ u409={[ ]

} u157={[ ]

} ]

} i1={[ u410={[ p882=1 ]

} u152={[ ]

} ]

} ]

[ u171={[ ]

} u169={[ ]

} u163={[ ]

} u414={[ ]

} u158={[ p935=1 ]

} i7={[ u370={[ ]

} u167={[ ]

} ]

} i5={[ u372={[ p938=1 ]

} u162={[ ]

} ]

} u153={[ ]

} u148={[ ]

} i3={[ u409={[ ]

} u157={[ ]

} ]

} i1={[ u410={[ ]

} u152={[ ]

} ]

} ]

[ u171={[ ]

} u169={[ ]

} u163={[ p955=1 ]

} u414={[ ]

} u158={[ ]

} i7={[ u370={[ p958=1 ]

} u167={[ ]

} ]

} i5={[ u372={[ ]

} u162={[ ]

} ]

} u153={[ ]

} u148={[ ]

} i3={[ u409={[ ]

} u157={[ ]

} ]

} i1={[ u410={[ ]

} u152={[ ]

} ]

} ]

} u178={[ p1008=1 ]

} u146={[ p851=1 ]

} i35={[ u363={[ ]

} u174={[ p987=1 ]

} u173={[ p984=1 ]

} ]

} u109={[ p621=1 ]

} u110={[ p638=1 ]

} u140={[ p803=1 ]

} i27={[ u136={[ ]

} u134={[ ]

} u128={[ ]

} u387={[ ]

} u123={[ ]

} i7={[ u401={[ ]

} u132={[ ]

} ]

} i5={[ u402={[ ]

} u127={[ ]

} ]

} u118={[ p718=1 ]

} u113={[ ]

} i3={[ u404={[ p721=1 ]

} u122={[ ]

} ]

} i1={[ u388={[ ]

} u117={[ ]

} ]

} ]

[ u136={[ ]

} u134={[ ]

} u128={[ ]

} u387={[ ]

} u123={[ ]

} i7={[ u401={[ ]

} u132={[ ]

} ]

} i5={[ u402={[ ]

} u127={[ ]

} ]

} u118={[ ]

} u113={[ p684=1 ]

} i3={[ u404={[ ]

} u122={[ ]

} ]

} i1={[ u388={[ p687=1 ]

} u117={[ ]

} ]

} ]

[ u136={[ ]

} u134={[ ]

} u128={[ ]

} u387={[ ]

} u123={[ p740=1 ]

} i7={[ u401={[ ]

} u132={[ ]

} ]

} i5={[ u402={[ p743=1 ]

} u127={[ ]

} ]

} u118={[ ]

} u113={[ ]

} i3={[ u404={[ ]

} u122={[ ]

} ]

} i1={[ u388={[ ]

} u117={[ ]

} ]

} ]

[ u136={[ ]

} u134={[ ]

} u128={[ p760=1 ]

} u387={[ ]

} u123={[ ]

} i7={[ u401={[ p763=1 ]

} u132={[ ]

} ]

} i5={[ u402={[ ]

} u127={[ ]

} ]

} u118={[ ]

} u113={[ ]

} i3={[ u404={[ ]

} u122={[ ]

} ]

} i1={[ u388={[ ]

} u117={[ ]

} ]

} ]

} u143={[ p813=1 ]

} u111={[ p656=1 ]

} i28={[ u417={[ ]

} u139={[ p792=1 ]

} u138={[ p789=1 ]

} ]

} u74={[ p426=1 ]

} u75={[ p443=1 ]

} u105={[ p608=1 ]

} i20={[ u101={[ ]

} u99={[ ]

} u93={[ ]

} u366={[ ]

} u88={[ ]

} i7={[ u376={[ ]

} u97={[ ]

} ]

} i5={[ u373={[ ]

} u92={[ ]

} ]

} u83={[ p523=1 ]

} u78={[ ]

} i3={[ u371={[ p526=1 ]

} u87={[ ]

} ]

} i1={[ u367={[ ]

} u82={[ ]

} ]

} ]

[ u101={[ ]

} u99={[ ]

} u93={[ ]

} u366={[ ]

} u88={[ ]

} i7={[ u376={[ ]

} u97={[ ]

} ]

} i5={[ u373={[ ]

} u92={[ ]

} ]

} u83={[ ]

} u78={[ p489=1 ]

} i3={[ u371={[ ]

} u87={[ ]

} ]

} i1={[ u367={[ p492=1 ]

} u82={[ ]

} ]

} ]

[ u101={[ ]

} u99={[ ]

} u93={[ ]

} u366={[ ]

} u88={[ p545=1 ]

} i7={[ u376={[ ]

} u97={[ ]

} ]

} i5={[ u373={[ p548=1 ]

} u92={[ ]

} ]

} u83={[ ]

} u78={[ ]

} i3={[ u371={[ ]

} u87={[ ]

} ]

} i1={[ u367={[ ]

} u82={[ ]

} ]

} ]

[ u101={[ ]

} u99={[ ]

} u93={[ p565=1 ]

} u366={[ ]

} u88={[ ]

} i7={[ u376={[ p568=1 ]

} u97={[ ]

} ]

} i5={[ u373={[ ]

} u92={[ ]

} ]

} u83={[ ]

} u78={[ ]

} i3={[ u371={[ ]

} u87={[ ]

} ]

} i1={[ u367={[ ]

} u82={[ ]

} ]

} ]

} u108={[ p618=1 ]

} i21={[ u394={[ ]

} u104={[ p597=1 ]

} u103={[ p594=1 ]

} ]

} u76={[ p461=1 ]

} u70={[ p413=1 ]

} u39={[ p231=1 ]

} u40={[ p248=1 ]

} i14={[ u418={[ ]

} u69={[ p402=1 ]

} u68={[ p399=1 ]

} ]

} i13={[ u66={[ ]

} u64={[ ]

} u58={[ ]

} u405={[ ]

} u53={[ ]

} i7={[ u413={[ ]

} u62={[ ]

} ]

} i5={[ u411={[ ]

} u57={[ ]

} ]

} u48={[ p328=1 ]

} u43={[ ]

} i3={[ u407={[ p331=1 ]

} u52={[ ]

} ]

} i1={[ u406={[ ]

} u47={[ ]

} ]

} ]

[ u66={[ ]

} u64={[ ]

} u58={[ ]

} u405={[ ]

} u53={[ ]

} i7={[ u413={[ ]

} u62={[ ]

} ]

} i5={[ u411={[ ]

} u57={[ ]

} ]

} u48={[ ]

} u43={[ p294=1 ]

} i3={[ u407={[ ]

} u52={[ ]

} ]

} i1={[ u406={[ p297=1 ]

} u47={[ ]

} ]

} ]

[ u66={[ ]

} u64={[ ]

} u58={[ ]

} u405={[ ]

} u53={[ p350=1 ]

} i7={[ u413={[ ]

} u62={[ ]

} ]

} i5={[ u411={[ p353=1 ]

} u57={[ ]

} ]

} u48={[ ]

} u43={[ ]

} i3={[ u407={[ ]

} u52={[ ]

} ]

} i1={[ u406={[ ]

} u47={[ ]

} ]

} ]

[ u66={[ ]

} u64={[ ]

} u58={[ p370=1 ]

} u405={[ ]

} u53={[ ]

} i7={[ u413={[ p373=1 ]

} u62={[ ]

} ]

} i5={[ u411={[ ]

} u57={[ ]

} ]

} u48={[ ]

} u43={[ ]

} i3={[ u407={[ ]

} u52={[ ]

} ]

} i1={[ u406={[ ]

} u47={[ ]

} ]

} ]

} u73={[ p423=1 ]

} u400={[ p204=1 ]

} u35={[ p218=1 ]

} u3={[ p25=1 ]

} u41={[ p266=1 ]

} u2={[ p21=1 ]

} u5={[ p54=1 ]

} u4={[ p37=1 ]

} i6={[ u31={[ ]

} u29={[ ]

} u23={[ ]

} u378={[ ]

} u18={[ ]

} i7={[ u397={[ ]

} u27={[ ]

} ]

} i5={[ u392={[ ]

} u22={[ ]

} ]

} u13={[ p134=1 ]

} u8={[ ]

} i3={[ u391={[ p137=1 ]

} u17={[ ]

} ]

} i1={[ u380={[ ]

} u12={[ ]

} ]

} ]

[ u31={[ ]

} u29={[ ]

} u23={[ ]

} u378={[ ]

} u18={[ ]

} i7={[ u397={[ ]

} u27={[ ]

} ]

} i5={[ u392={[ ]

} u22={[ ]

} ]

} u13={[ ]

} u8={[ p100=1 ]

} i3={[ u391={[ ]

} u17={[ ]

} ]

} i1={[ u380={[ p103=1 ]

} u12={[ ]

} ]

} ]

[ u31={[ ]

} u29={[ ]

} u23={[ ]

} u378={[ ]

} u18={[ p156=1 ]

} i7={[ u397={[ ]

} u27={[ ]

} ]

} i5={[ u392={[ p159=1 ]

} u22={[ ]

} ]

} u13={[ ]

} u8={[ ]

} i3={[ u391={[ ]

} u17={[ ]

} ]

} i1={[ u380={[ ]

} u12={[ ]

} ]

} ]

[ u31={[ ]

} u29={[ ]

} u23={[ p176=1 ]

} u378={[ ]

} u18={[ ]

} i7={[ u397={[ p179=1 ]

} u27={[ ]

} ]

} i5={[ u392={[ ]

} u22={[ ]

} ]

} u13={[ ]

} u8={[ ]

} i3={[ u391={[ ]

} u17={[ ]

} ]

} i1={[ u380={[ ]

} u12={[ ]

} ]

} ]

} u38={[ p228=1 ]

} u1={[ p2=1 ]

[ p18=1 ]

} u6={[ p72=1 ]

} ]

WARNING : LTS min runner thread was asked to interrupt. Dying gracefully.

BK_STOP 1527870816250

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityDeadlock -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityDeadlock -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Jun 01, 2018 4:32:06 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityDeadlock, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -louvain, -smt]

Jun 01, 2018 4:32:06 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Jun 01, 2018 4:32:06 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 315 ms

Jun 01, 2018 4:32:06 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1991 places.

Jun 01, 2018 4:32:07 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 2919 transitions.

Jun 01, 2018 4:32:07 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

Jun 01, 2018 4:32:07 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 66 ms

Jun 01, 2018 4:32:07 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 679 ms

Jun 01, 2018 4:32:07 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.simple.gal : 22 ms

Jun 01, 2018 4:32:08 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 2919 transitions.

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 2177 transitions.

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Too many transitions (2177) to apply POR reductions. Disabling POR matrices.

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 314 ms

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 413ms conformant to PINS in folder :/home/mcc/execution

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 301 ms

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

Jun 01, 2018 4:32:13 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 209 ms

Jun 01, 2018 4:32:14 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

Jun 01, 2018 4:32:14 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 3034 redundant transitions.

Jun 01, 2018 4:32:14 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 50 ms

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ASLink-PT-09a"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="itstoolsl"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/ASLink-PT-09a.tgz

mv ASLink-PT-09a execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstoolsl"

echo " Input is ASLink-PT-09a, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r273-smll-152749149600152"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;