About the Execution of ITS-Tools for ASLink-PT-04b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15752.260 | 169049.00 | 359930.00 | 686.10 | T | normal |

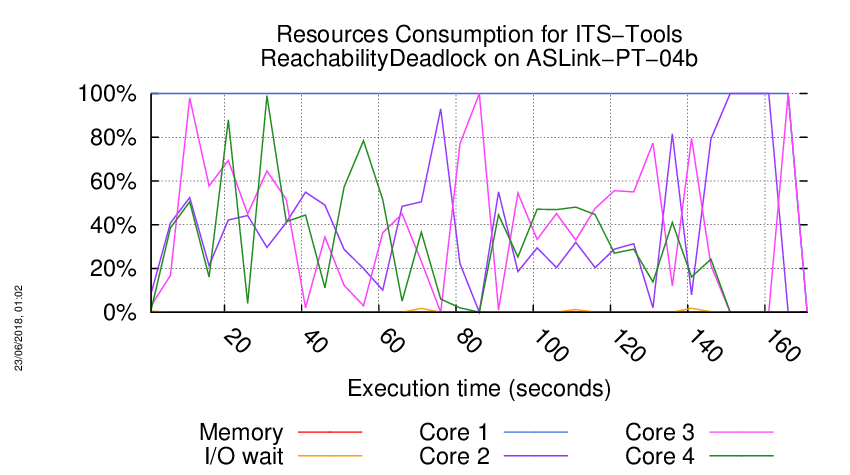

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

...................

/home/mcc/execution

total 844K

-rw-r--r-- 1 mcc users 3.6K May 29 16:53 CTLCardinality.txt

-rw-r--r-- 1 mcc users 20K May 29 16:53 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K May 28 11:14 CTLFireability.txt

-rw-r--r-- 1 mcc users 17K May 28 11:14 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 24 11:17 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.6K May 24 11:17 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 28 09:22 LTLCardinality.txt

-rw-r--r-- 1 mcc users 11K May 28 09:22 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 28 07:37 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.1K May 28 07:37 LTLFireability.xml

-rw-r--r-- 1 mcc users 1 May 24 11:17 NewModel

-rw-r--r-- 1 mcc users 3.5K May 27 05:07 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 18K May 27 05:07 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 104 May 26 06:29 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 342 May 26 06:29 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.7K May 26 06:34 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K May 26 06:34 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 28 07:31 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 28 07:31 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 24 11:17 equiv_col

-rw-r--r-- 1 mcc users 4 May 24 11:17 instance

-rw-r--r-- 1 mcc users 6 May 24 11:17 iscolored

-rw-r--r-- 1 mcc users 669K May 24 11:17 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstools

Input is ASLink-PT-04b, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r272-smll-152749148700071

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ASLink-PT-04b-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1527787395630

Flatten gal took : 616 ms

Constant places removed 1 places and 1 transitions.

Performed 928 Post agglomeration using F-continuation condition.

Iterating post reduction 0 with 929 rules applied. Total rules applied 929 place count 2033 transition count 1638

Constant places removed 986 places and 2 transitions.

Reduce isomorphic transitions removed 16 transitions.

Implicit places reduction removed 8 places :[p1763, p1635, p1240, p1214, p845, p819, p450, p424]

Performed 56 Post agglomeration using F-continuation condition.

Iterating post reduction 1 with 1066 rules applied. Total rules applied 1995 place count 1039 transition count 1564

Constant places removed 64 places and 0 transitions.

Performed 20 Post agglomeration using F-continuation condition.

Iterating post reduction 2 with 84 rules applied. Total rules applied 2079 place count 975 transition count 1544

Constant places removed 20 places and 0 transitions.

Implicit places reduction removed 7 places :[p1604, p1590, p1209, p1195, p814, p800, p405]

Performed 7 Post agglomeration using F-continuation condition.

Iterating post reduction 3 with 34 rules applied. Total rules applied 2113 place count 948 transition count 1537

Constant places removed 7 places and 0 transitions.

Iterating post reduction 4 with 7 rules applied. Total rules applied 2120 place count 941 transition count 1537

Performed 149 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 5 with 149 Pre rules applied. Total rules applied 2120 place count 941 transition count 1388

Constant places removed 150 places and 0 transitions.

Implicit places reduction removed 1 places :[p419]

Performed 1 Post agglomeration using F-continuation condition.

Iterating post reduction 5 with 152 rules applied. Total rules applied 2272 place count 790 transition count 1387

Constant places removed 1 places and 0 transitions.

Iterating post reduction 6 with 1 rules applied. Total rules applied 2273 place count 789 transition count 1387

Performed 1 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 7 with 1 Pre rules applied. Total rules applied 2273 place count 789 transition count 1386

Constant places removed 1 places and 0 transitions.

Iterating post reduction 7 with 1 rules applied. Total rules applied 2274 place count 788 transition count 1386

Symmetric choice reduction at 8 with 17 rule applications. Total rules 2291 place count 788 transition count 1386

Constant places removed 17 places and 17 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 1 places :[p2033]

Performed 7 Post agglomeration using F-continuation condition.

Iterating post reduction 8 with 26 rules applied. Total rules applied 2317 place count 770 transition count 1361

Constant places removed 8 places and 0 transitions.

Iterating post reduction 9 with 8 rules applied. Total rules applied 2325 place count 762 transition count 1361

Symmetric choice reduction at 10 with 10 rule applications. Total rules 2335 place count 762 transition count 1361

Constant places removed 10 places and 38 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 5 places :[p1772, p1576, p1181, p786, p391]

Performed 11 Post agglomeration using F-continuation condition.

Iterating post reduction 10 with 27 rules applied. Total rules applied 2362 place count 747 transition count 1311

Constant places removed 11 places and 0 transitions.

Iterating post reduction 11 with 11 rules applied. Total rules applied 2373 place count 736 transition count 1311

Symmetric choice reduction at 12 with 5 rule applications. Total rules 2378 place count 736 transition count 1311

Constant places removed 5 places and 12 transitions.

Iterating post reduction 12 with 5 rules applied. Total rules applied 2383 place count 731 transition count 1299

Symmetric choice reduction at 13 with 1 rule applications. Total rules 2384 place count 731 transition count 1299

Constant places removed 1 places and 8 transitions.

Iterating post reduction 13 with 1 rules applied. Total rules applied 2385 place count 730 transition count 1291

Symmetric choice reduction at 14 with 1 rule applications. Total rules 2386 place count 730 transition count 1291

Constant places removed 1 places and 8 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 2387 place count 729 transition count 1283

Symmetric choice reduction at 15 with 1 rule applications. Total rules 2388 place count 729 transition count 1283

Constant places removed 1 places and 8 transitions.

Iterating post reduction 15 with 1 rules applied. Total rules applied 2389 place count 728 transition count 1275

Symmetric choice reduction at 16 with 1 rule applications. Total rules 2390 place count 728 transition count 1275

Constant places removed 1 places and 8 transitions.

Iterating post reduction 16 with 1 rules applied. Total rules applied 2391 place count 727 transition count 1267

Symmetric choice reduction at 17 with 1 rule applications. Total rules 2392 place count 727 transition count 1267

Constant places removed 1 places and 8 transitions.

Iterating post reduction 17 with 1 rules applied. Total rules applied 2393 place count 726 transition count 1259

Symmetric choice reduction at 18 with 1 rule applications. Total rules 2394 place count 726 transition count 1259

Constant places removed 1 places and 8 transitions.

Iterating post reduction 18 with 1 rules applied. Total rules applied 2395 place count 725 transition count 1251

Symmetric choice reduction at 19 with 1 rule applications. Total rules 2396 place count 725 transition count 1251

Constant places removed 1 places and 8 transitions.

Iterating post reduction 19 with 1 rules applied. Total rules applied 2397 place count 724 transition count 1243

Symmetric choice reduction at 20 with 1 rule applications. Total rules 2398 place count 724 transition count 1243

Constant places removed 1 places and 8 transitions.

Iterating post reduction 20 with 1 rules applied. Total rules applied 2399 place count 723 transition count 1235

Symmetric choice reduction at 21 with 1 rule applications. Total rules 2400 place count 723 transition count 1235

Constant places removed 1 places and 8 transitions.

Iterating post reduction 21 with 1 rules applied. Total rules applied 2401 place count 722 transition count 1227

Symmetric choice reduction at 22 with 1 rule applications. Total rules 2402 place count 722 transition count 1227

Constant places removed 1 places and 8 transitions.

Iterating post reduction 22 with 1 rules applied. Total rules applied 2403 place count 721 transition count 1219

Symmetric choice reduction at 23 with 1 rule applications. Total rules 2404 place count 721 transition count 1219

Constant places removed 1 places and 8 transitions.

Iterating post reduction 23 with 1 rules applied. Total rules applied 2405 place count 720 transition count 1211

Symmetric choice reduction at 24 with 1 rule applications. Total rules 2406 place count 720 transition count 1211

Constant places removed 1 places and 8 transitions.

Iterating post reduction 24 with 1 rules applied. Total rules applied 2407 place count 719 transition count 1203

Symmetric choice reduction at 25 with 1 rule applications. Total rules 2408 place count 719 transition count 1203

Constant places removed 1 places and 8 transitions.

Iterating post reduction 25 with 1 rules applied. Total rules applied 2409 place count 718 transition count 1195

Symmetric choice reduction at 26 with 1 rule applications. Total rules 2410 place count 718 transition count 1195

Constant places removed 1 places and 8 transitions.

Iterating post reduction 26 with 1 rules applied. Total rules applied 2411 place count 717 transition count 1187

Symmetric choice reduction at 27 with 1 rule applications. Total rules 2412 place count 717 transition count 1187

Constant places removed 1 places and 8 transitions.

Iterating post reduction 27 with 1 rules applied. Total rules applied 2413 place count 716 transition count 1179

Performed 49 Post agglomeration using F-continuation condition.

Constant places removed 49 places and 0 transitions.

Iterating post reduction 28 with 49 rules applied. Total rules applied 2462 place count 667 transition count 1126

Performed 1 Post agglomeration using F-continuation condition.

Constant places removed 1 places and 0 transitions.

Iterating post reduction 29 with 1 rules applied. Total rules applied 2463 place count 666 transition count 1135

Applied a total of 2463 rules in 1561 ms. Remains 666 /2034 variables (removed 1368) and now considering 1135/2567 (removed 1432) transitions.

// Phase 1: matrix 1135 rows 666 cols

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK

No direction supplied, using forward translation only.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 1135 rows 666 cols

invariant :p52 + -1'p54 + -1'p58 + -1'p63 + -1'p70 + -1'p71 + -1'p73 + -1'p75 + -1'p432 + p436 + p442 + p808 = 1

invariant :p1502 + p1506 + p1508 + p1509 + p1511 + p1514 + p1516 + -1'p1517 + -1'p1518 + -1'p1519 = 0

invariant :p1318 + p1321 + p1324 + p1327 + p1330 + p1333 + p1336 + p1339 + p1416 + p1477 + p1514 + p1548 + p1609 + p1611 = 1

invariant :p11 + p15 + p19 + p23 + p27 + p31 + p35 + p39 + p43 + p58 + p66 + p71 + p75 + p162 + p165 + p168 + p171 + p174 + p177 + p180 + p183 = 1

invariant :p1026 + p1087 + p1124 + p1158 + p1263 = 1

invariant :p1616 + p1622 + p1628 + -1'p1725 + p1729 + -1'p1734 + -1'p1737 + -1'p1740 + -1'p1743 + -1'p1746 + -1'p1749 + -1'p1752 + -1'p1755 + -1'p1860 + -1'p1861 + p1867 + -1'p1871 + p1878 + -1'p1882 + p1886 + -1'p1890 + p1894 + -1'p1898 + p1902 + p1905 + -1'p1909 + -1'p1911 + -1'p1914 + p1921 + -1'p1925 + p1929 + p1932 + -1'p1936 + -1'p1938 + -1'p1941 + p1948 + p1951 + -1'p1955 + -1'p1957 = 0

invariant :p885 + p889 + p893 + p897 + p901 + p905 + p909 + p913 + p917 + -1'p1012 + -1'p1013 + -1'p1024 + -1'p1025 + -1'p1029 + -1'p1034 + -1'p1038 + -1'p1043 + -1'p1085 + -1'p1086 + -1'p1122 + -1'p1123 + -1'p1156 + -1'p1157 + -1'p1187 + p1263 + p1347 + p1350 + p1353 + p1356 + p1359 + p1362 + p1365 + p1368 = 1

invariant :p1664 + p1782 + p1785 + p1788 + p1791 + p1970 + p1978 + p1986 + p2016 + p2024 = 1

invariant :p1964 + p1965 + p1966 + -1'p1968 + -1'p1969 + -1'p1970 = 0

invariant :p1657 + p1658 = 1

invariant :p1725 + p1726 + p1732 + p1734 + p1735 + p1737 + p1738 + p1740 + p1741 + p1743 + p1744 + p1746 + p1747 + p1749 + p1750 + p1752 + p1753 + p1755 + p1756 + p1860 + p1861 + -1'p1867 + -1'p1868 + p1871 + p1872 + -1'p1878 + -1'p1879 + p1882 + p1883 + -1'p1886 + -1'p1887 + p1890 + p1891 + -1'p1894 + -1'p1895 + p1898 + p1899 + -1'p1902 + -1'p1903 + -1'p1905 + p1909 + p1914 + p1915 + -1'p1921 + -1'p1922 + p1925 + p1926 + -1'p1929 + -1'p1930 + -1'p1932 + p1936 + p1941 + p1942 + -1'p1948 + -1'p1949 + -1'p1951 + p1955 = 0

invariant :p1345 + p1347 + p1348 + p1350 + p1351 + p1353 + p1354 + p1356 + p1357 + p1359 + p1360 + p1362 + p1363 + p1365 + p1366 + p1368 + p1369 + -1'p1400 = 0

invariant :p1144 + p1148 + p1150 + p1153 + p1155 + -1'p1156 + -1'p1157 + -1'p1158 = 0

invariant :p1018 + p1021 + p1023 + -1'p1024 + -1'p1025 + -1'p1029 + -1'p1030 + -1'p1034 + -1'p1035 + -1'p1038 + -1'p1039 + -1'p1043 + -1'p1044 + p1087 + p1124 + p1158 + p1263 = 1

invariant :-1'p923 + -1'p926 + -1'p929 + -1'p932 + -1'p935 + -1'p938 + -1'p941 + -1'p944 + p1224 + p1226 + p1228 = 0

invariant :p950 + p952 + p953 + p955 + p956 + p958 + p959 + p961 + p962 + p964 + p965 + p967 + p968 + p970 + p971 + p973 + p974 + -1'p1005 = 0

invariant :p90 + p222 + p223 + p234 + p235 + p239 + p244 + p248 + p253 + p295 + p296 + p332 + p333 + p366 + p367 + p397 + -1'p473 = 0

invariant :-1'p1897 + -1'p1898 + -1'p1899 + p1901 + p1902 + p1903 = 0

invariant :p1203 + p1205 + p1207 + p1222 + -1'p1226 + -1'p1232 + -1'p1598 = 0

invariant :-1'p528 + -1'p531 + -1'p534 + -1'p537 + -1'p540 + -1'p543 + -1'p546 + -1'p549 + -1'p626 + p669 + p673 + p675 + p676 + p678 + p679 + p681 + p682 + p684 + p689 + -1'p690 + -1'p691 + -1'p692 + -1'p724 + -1'p758 + -1'p821 + -1'p827 + p831 + p837 + p1203 = 0

invariant :-1'p1609 + p1614 + p1617 + -1'p1622 + -1'p1628 + p1725 + -1'p1729 + p1734 + p1737 + p1740 + p1743 + p1746 + p1749 + p1752 + p1755 + p1860 + p1861 + -1'p1867 + p1871 + -1'p1878 + p1882 + -1'p1886 + p1890 + -1'p1894 + p1898 + -1'p1902 + -1'p1905 + p1909 + p1911 + p1914 + -1'p1921 + p1925 + -1'p1929 + -1'p1932 + p1936 + p1938 + p1941 + -1'p1948 + -1'p1951 + p1955 + p1957 = 0

invariant :p1719 + p1868 + p1879 + p1887 + p1895 + p1903 + p1911 + p1922 + p1930 + p1938 + p1949 + p1957 = 1

invariant :p1960 + p1961 + -1'p1968 + -1'p1969 + -1'p1970 = 0

invariant :p526 + p528 + p530 + p531 + p533 + p534 + p536 + p537 + p539 + p540 + p542 + p543 + p545 + p546 + p548 + p549 + p551 + -1'p673 + -1'p676 + -1'p679 + -1'p682 + -1'p716 + -1'p719 + -1'p753 = 0

invariant :p1421 + p1482 + p1519 + p1553 + p1658 = 1

invariant :p10 + -1'p58 + -1'p66 + -1'p71 + -1'p75 = 0

invariant :-1'p1859 + -1'p1860 + -1'p1861 + p1866 + p1867 + p1868 = 0

invariant :p1539 + p1543 + p1545 + p1548 + p1550 + -1'p1551 + -1'p1552 + -1'p1553 = 0

invariant :-1'p1318 + -1'p1321 + -1'p1324 + -1'p1327 + -1'p1330 + -1'p1333 + -1'p1336 + -1'p1339 + -1'p1416 + p1459 + p1463 + p1465 + p1466 + p1468 + p1469 + p1471 + p1472 + p1474 + p1479 + -1'p1480 + -1'p1481 + -1'p1482 + -1'p1514 + -1'p1548 + -1'p1609 + -1'p1611 = -1

invariant :p131 + p133 + p135 + p136 + p138 + p139 + p141 + p142 + p144 + p145 + p147 + p148 + p150 + p151 + p153 + p154 + p156 + -1'p278 + -1'p281 + -1'p284 + -1'p287 + -1'p321 + -1'p324 + -1'p358 = 0

invariant :p1731 + -1'p1872 + -1'p1883 + -1'p1891 + -1'p1899 + -1'p1915 + -1'p1926 + -1'p1942 = 0

invariant :p317 + p321 + p323 + p324 + p326 + p329 + p331 + -1'p332 + -1'p333 + -1'p334 = 0

invariant :p1314 + p1463 + p1466 + p1469 + p1472 + p1506 + p1509 + p1543 = 1

invariant :p1972 + p1973 + p1974 + -1'p1976 + -1'p1977 + -1'p1978 = 0

invariant :p98 + p102 + p106 + p110 + p114 + p118 + p122 + p126 + -1'p557 + -1'p560 + -1'p563 + -1'p566 + -1'p569 + -1'p572 + -1'p575 + -1'p578 = 0

invariant :p133 + p136 + p139 + p142 + p145 + p148 + p151 + p154 + p426 + p432 + -1'p436 + p440 + p444 + -1'p808 = 0

invariant :p1598 + p1600 + p1602 + p1609 = 1

invariant :p14 + p18 + p22 + p26 + p30 + p34 + p38 + p42 + -1'p162 + -1'p165 + -1'p168 + -1'p171 + -1'p174 + -1'p177 + -1'p180 + -1'p183 = 0

invariant :p1318 + p1321 + p1324 + p1327 + p1330 + p1333 + p1336 + p1339 + p1609 + p1611 + p1626 + p1628 + p1629 = 1

invariant :p1107 + p1111 + p1113 + p1114 + p1116 + p1119 + p1121 + -1'p1122 + -1'p1123 + -1'p1124 = 0

invariant :p1905 + p1906 + p1907 + -1'p1909 + -1'p1910 + -1'p1911 = 0

invariant :-1'p1318 + -1'p1321 + -1'p1324 + -1'p1327 + -1'p1330 + -1'p1333 + -1'p1336 + -1'p1339 + p1620 + p1622 + p1623 = 0

invariant :p354 + p358 + p360 + p363 + p365 + -1'p366 + -1'p367 + -1'p368 = 0

invariant :p1980 + p1981 + p1982 + -1'p1984 + -1'p1985 + -1'p1986 = 0

invariant :p54 + p58 + p63 + p65 + p66 + p68 + p70 + p71 + p73 + p75 + p432 + -1'p436 + -1'p442 + -1'p808 = 0

invariant :p1316 + p1318 + p1320 + p1321 + p1323 + p1324 + p1326 + p1327 + p1329 + p1330 + p1332 + p1333 + p1335 + p1336 + p1338 + p1339 + p1341 + -1'p1463 + -1'p1466 + -1'p1469 + -1'p1472 + -1'p1506 + -1'p1509 + -1'p1543 = 0

invariant :p157 + p215 = 1

invariant :p1774 + p1782 + p1784 + p1785 + p1787 + p1788 + p1790 + p1791 + p1793 = 1

invariant :-1'p1913 + -1'p1914 + -1'p1915 + p1920 + p1921 + p1922 = 0

invariant :p2018 + p2019 + p2020 + -1'p2022 + -1'p2023 + -1'p2024 = 0

invariant :p1724 + -1'p1861 + -1'p1907 + -1'p1934 + -1'p1953 = 0

invariant :p472 + p473 = 1

invariant :p1397 + p1400 + p1402 + p1407 + p1408 + p1419 + p1420 + p1424 + p1425 + p1429 + p1430 + p1433 + p1434 + p1438 + p1439 + p1480 + p1481 + p1517 + p1518 + p1551 + p1552 + p1582 + p1588 + -1'p1658 = 0

invariant :-1'p133 + -1'p136 + -1'p139 + -1'p142 + -1'p145 + -1'p148 + -1'p151 + -1'p154 + p434 + p436 + p438 = 0

invariant :p712 + p716 + p718 + p719 + p721 + p724 + p726 + -1'p727 + -1'p728 + -1'p729 = 0

invariant :p236 + p297 + p334 + p368 + p473 = 1

invariant :p524 + p673 + p676 + p679 + p682 + p716 + p719 + p753 = 1

invariant :p1275 + p1407 + p1408 + p1419 + p1420 + p1424 + p1429 + p1433 + p1438 + p1480 + p1481 + p1517 + p1518 + p1551 + p1552 + p1582 + -1'p1658 = 0

invariant :-1'p1940 + -1'p1941 + -1'p1942 + p1947 + p1948 + p1949 = 0

invariant :p1262 + p1263 = 1

invariant :p528 + p531 + p534 + p537 + p540 + p543 + p546 + p549 + p821 + p827 + -1'p831 + p835 + p839 + -1'p1203 = 0

invariant :p1413 + p1416 + p1418 + -1'p1419 + -1'p1420 + -1'p1424 + -1'p1425 + -1'p1429 + -1'p1430 + -1'p1433 + -1'p1434 + -1'p1438 + -1'p1439 + p1482 + p1519 + p1553 + p1658 = 1

invariant :p607 + p610 + p612 + p617 + p618 + p629 + p630 + p634 + p635 + p639 + p640 + p643 + p644 + p648 + p649 + p690 + p691 + p727 + p728 + p761 + p762 + p792 + p798 + -1'p868 = 0

invariant :p1002 + p1005 + p1007 + p1012 + p1013 + p1024 + p1025 + p1029 + p1030 + p1034 + p1035 + p1038 + p1039 + p1043 + p1044 + p1085 + p1086 + p1122 + p1123 + p1156 + p1157 + p1187 + p1193 + -1'p1263 = 0

invariant :p1998 + p2006 + -1'p2014 + -1'p2015 + -1'p2016 = 0

invariant :p888 + p892 + p896 + p900 + p904 + p908 + p912 + p916 + -1'p1347 + -1'p1350 + -1'p1353 + -1'p1356 + -1'p1359 + -1'p1362 + -1'p1365 + -1'p1368 = 0

invariant :p623 + p626 + p628 + -1'p629 + -1'p630 + -1'p634 + -1'p635 + -1'p639 + -1'p640 + -1'p643 + -1'p644 + -1'p648 + -1'p649 + p692 + p729 + p763 + p868 = 1

invariant :p808 + p810 + p812 + p827 + -1'p831 + -1'p837 + -1'p1203 = 0

invariant :-1'p1283 + -1'p1287 + -1'p1291 + -1'p1295 + -1'p1299 + -1'p1303 + -1'p1307 + -1'p1311 + p1669 + p1672 + p1675 + p1678 + p1681 + p1684 + p1687 + p1690 = 0

invariant :p1761 + -1'p1966 + -1'p1974 + -1'p1982 + -1'p2020 = 0

invariant :p1932 + p1933 + p1934 + -1'p1936 + -1'p1937 + -1'p1938 = 0

invariant :p552 + p610 = 1

invariant :p919 + p1068 + p1071 + p1074 + p1077 + p1111 + p1114 + p1148 = 1

invariant :p825 + p831 + p837 + p1203 = 1

invariant :p1782 + p1784 + p1785 + p1787 + p1788 + p1790 + p1791 + p1793 + p1794 + p1855 + p1859 + p1860 + p1861 + p1870 + p1871 + p1872 + p1881 + p1882 + p1883 + p1889 + p1890 + p1891 + p1897 + p1898 + p1899 + p1909 + p1910 + p1911 + p1913 + p1914 + p1915 + p1924 + p1925 + p1926 + p1936 + p1937 + p1938 + p1940 + p1941 + p1942 + p1955 + p1956 + p1957 + p1968 + p1969 + p1970 + p1976 + p1977 + p1978 + p1984 + p1985 + p1986 + p2014 + p2015 + p2016 + p2022 + p2023 + p2024 = 1

invariant :p1722 + p1729 + -1'p1860 + p1867 + -1'p1871 + p1878 + -1'p1882 + p1886 + -1'p1890 + p1894 + -1'p1898 + p1902 + p1905 + p1907 + -1'p1909 + -1'p1911 + -1'p1914 + p1921 + -1'p1925 + p1929 + p1932 + p1934 + -1'p1936 + -1'p1938 + -1'p1941 + p1948 + p1951 + p1953 + -1'p1955 + -1'p1957 = 0

invariant :p1342 + p1400 = 1

invariant :p749 + p753 + p755 + p758 + p760 + -1'p761 + -1'p762 + -1'p763 = 0

invariant :p1951 + p1952 + p1953 + -1'p1955 + -1'p1956 + -1'p1957 = 0

invariant :p1765 + p1966 + p1974 + p1982 + p2020 = 1

invariant :p129 + p278 + p281 + p284 + p287 + p321 + p324 + p358 = 1

invariant :p413 + p432 + -1'p436 + -1'p442 + -1'p808 = 0

invariant :p493 + p497 + p501 + p505 + p509 + p513 + p517 + p521 + -1'p952 + -1'p955 + -1'p958 + -1'p961 + -1'p964 + -1'p967 + -1'p970 + -1'p973 = 0

invariant :-1'p923 + -1'p926 + -1'p929 + -1'p932 + -1'p935 + -1'p938 + -1'p941 + -1'p944 + -1'p1021 + p1064 + p1068 + p1070 + p1071 + p1073 + p1074 + p1076 + p1077 + p1079 + p1084 + -1'p1085 + -1'p1086 + -1'p1087 + -1'p1119 + -1'p1153 + -1'p1216 + -1'p1222 + p1226 + p1232 + p1598 = 0

invariant :p490 + p494 + p498 + p502 + p506 + p510 + p514 + p518 + p522 + -1'p617 + -1'p618 + -1'p629 + -1'p630 + -1'p634 + -1'p639 + -1'p643 + -1'p648 + -1'p690 + -1'p691 + -1'p727 + -1'p728 + -1'p761 + -1'p762 + -1'p792 + p868 + p952 + p955 + p958 + p961 + p964 + p967 + p970 + p973 = 1

invariant :p133 + p136 + p139 + p142 + p145 + p148 + p151 + p154 + p231 + p292 + p329 + p363 + p426 + p432 + -1'p436 + -1'p442 + -1'p808 = 0

invariant :p921 + p923 + p925 + p926 + p928 + p929 + p931 + p932 + p934 + p935 + p937 + p938 + p940 + p941 + p943 + p944 + p946 + -1'p1068 + -1'p1071 + -1'p1074 + -1'p1077 + -1'p1111 + -1'p1114 + -1'p1148 = 0

invariant :p528 + p531 + p534 + p537 + p540 + p543 + p546 + p549 + p626 + p687 + p724 + p758 + p821 + p827 + -1'p831 + -1'p837 + -1'p1203 = 0

invariant :-1'p1889 + -1'p1890 + -1'p1891 + p1893 + p1894 + p1895 = 0

invariant :p923 + p926 + p929 + p932 + p935 + p938 + p941 + p944 + p1216 + p1222 + -1'p1226 + p1230 + p1234 + -1'p1598 = 0

invariant :p555 + p557 + p558 + p560 + p561 + p563 + p564 + p566 + p567 + p569 + p570 + p572 + p573 + p575 + p576 + p578 + p579 + -1'p610 = 0

invariant :-1'p1881 + -1'p1882 + -1'p1883 + p1885 + p1886 + p1887 = 0

invariant :p430 + p436 + p442 + p808 = 1

invariant :-1'p528 + -1'p531 + -1'p534 + -1'p537 + -1'p540 + -1'p543 + -1'p546 + -1'p549 + p829 + p831 + p833 = 0

invariant :p1283 + p1287 + p1291 + p1295 + p1299 + p1303 + p1307 + p1311 + p1667 + p1670 + p1673 + p1676 + p1679 + p1682 + p1685 + p1688 + p1691 + -1'p1782 + -1'p1785 + -1'p1788 + -1'p1791 + -1'p1970 + -1'p1978 + -1'p1986 + -1'p2016 + -1'p2024 = 0

invariant :p1280 + p1283 + p1284 + p1287 + p1288 + p1291 + p1292 + p1295 + p1296 + p1299 + p1300 + p1303 + p1304 + p1307 + p1308 + p1311 + p1312 + -1'p1407 + -1'p1408 + -1'p1419 + -1'p1420 + -1'p1424 + -1'p1429 + -1'p1433 + -1'p1438 + -1'p1480 + -1'p1481 + -1'p1517 + -1'p1518 + -1'p1551 + -1'p1552 + -1'p1582 + p1658 = 1

invariant :-1'p133 + -1'p136 + -1'p139 + -1'p142 + -1'p145 + -1'p148 + -1'p151 + -1'p154 + -1'p231 + p274 + p278 + p280 + p281 + p283 + p284 + p286 + p287 + p289 + p294 + -1'p295 + -1'p296 + -1'p297 + -1'p329 + -1'p363 + -1'p426 + -1'p432 + p436 + p442 + p808 = 0

invariant :p95 + p99 + p103 + p107 + p111 + p115 + p119 + p123 + p127 + -1'p222 + -1'p223 + -1'p234 + -1'p235 + -1'p239 + -1'p244 + -1'p248 + -1'p253 + -1'p295 + -1'p296 + -1'p332 + -1'p333 + -1'p366 + -1'p367 + -1'p397 + p473 + p557 + p560 + p563 + p566 + p569 + p572 + p575 + p578 = 1

invariant :p50 + p54 + p58 + p63 + p70 + p71 + p73 + p75 + p432 + -1'p436 + -1'p442 + -1'p808 = 0

invariant :p867 + p868 = 1

invariant :p160 + p162 + p163 + p165 + p166 + p168 + p169 + p171 + p172 + p174 + p175 + p177 + p178 + p180 + p181 + p183 + p184 + -1'p215 = 0

invariant :p923 + p926 + p929 + p932 + p935 + p938 + p941 + p944 + p1021 + p1082 + p1119 + p1153 + p1216 + p1222 + -1'p1226 + -1'p1232 + -1'p1598 = 0

invariant :-1'p1924 + -1'p1925 + -1'p1926 + p1928 + p1929 + p1930 = 0

invariant :-1'p1870 + -1'p1871 + -1'p1872 + p1877 + p1878 + p1879 = 0

invariant :p880 + p1012 + p1013 + p1024 + p1025 + p1029 + p1034 + p1038 + p1043 + p1085 + p1086 + p1122 + p1123 + p1156 + p1157 + p1187 + -1'p1263 = 0

invariant :p485 + p617 + p618 + p629 + p630 + p634 + p639 + p643 + p648 + p690 + p691 + p727 + p728 + p761 + p762 + p792 + -1'p868 = 0

invariant :p947 + p1005 = 1

invariant :p228 + p231 + p233 + -1'p234 + -1'p235 + -1'p239 + -1'p240 + -1'p244 + -1'p245 + -1'p248 + -1'p249 + -1'p253 + -1'p254 + p297 + p334 + p368 + p473 = 1

invariant :p631 + p692 + p729 + p763 + p868 = 1

invariant :p1220 + p1226 + p1232 + p1598 = 1

invariant :p212 + p215 + p217 + p222 + p223 + p234 + p235 + p239 + p240 + p244 + p245 + p248 + p249 + p253 + p254 + p295 + p296 + p332 + p333 + p366 + p367 + p397 + p403 + -1'p473 = 0

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Compilation finished in 17673 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 82 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

LTSmin run took 4892 ms.

FORMULA ASLink-PT-04b-ReachabilityDeadlock-0 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1527787564679

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityDeadlock -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityDeadlock -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

May 31, 2018 5:23:17 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityDeadlock, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

May 31, 2018 5:23:17 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

May 31, 2018 5:23:18 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 285 ms

May 31, 2018 5:23:18 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 2034 places.

May 31, 2018 5:23:18 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 2567 transitions.

May 31, 2018 5:23:18 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

May 31, 2018 5:23:18 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 64 ms

May 31, 2018 5:23:19 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 609 ms

May 31, 2018 5:23:19 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.simple.gal : 19 ms

May 31, 2018 5:23:19 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 2567 transitions.

May 31, 2018 5:23:22 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 9 ms

May 31, 2018 5:23:22 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 1135 transitions.

May 31, 2018 5:23:23 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 111 place invariants in 497 ms

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 666 variables to be positive in 1907 ms

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 1135 transitions.

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/1135 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 189 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 1135 transitions.

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 128 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 5:23:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 1135 transitions.

May 31, 2018 5:23:28 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(4/1135) took 3114 ms. Total solver calls (SAT/UNSAT): 695(632/63)

May 31, 2018 5:23:31 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(28/1135) took 6207 ms. Total solver calls (SAT/UNSAT): 3995(3932/63)

May 31, 2018 5:23:34 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(56/1135) took 9246 ms. Total solver calls (SAT/UNSAT): 7117(7054/63)

May 31, 2018 5:23:37 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(83/1135) took 12258 ms. Total solver calls (SAT/UNSAT): 10345(10282/63)

May 31, 2018 5:23:40 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(109/1135) took 15294 ms. Total solver calls (SAT/UNSAT): 13504(13441/63)

May 31, 2018 5:23:43 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(141/1135) took 18336 ms. Total solver calls (SAT/UNSAT): 16914(15743/1171)

May 31, 2018 5:23:46 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(184/1135) took 21343 ms. Total solver calls (SAT/UNSAT): 21429(15944/5485)

May 31, 2018 5:23:49 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(216/1135) took 24412 ms. Total solver calls (SAT/UNSAT): 25149(18750/6399)

May 31, 2018 5:23:52 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(244/1135) took 27514 ms. Total solver calls (SAT/UNSAT): 28383(21984/6399)

May 31, 2018 5:23:56 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(269/1135) took 30718 ms. Total solver calls (SAT/UNSAT): 30797(24284/6513)

May 31, 2018 5:23:59 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(290/1135) took 33756 ms. Total solver calls (SAT/UNSAT): 32858(26117/6741)

May 31, 2018 5:24:02 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(312/1135) took 36828 ms. Total solver calls (SAT/UNSAT): 36015(29274/6741)

May 31, 2018 5:24:05 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(338/1135) took 39927 ms. Total solver calls (SAT/UNSAT): 39122(32381/6741)

May 31, 2018 5:24:08 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(368/1135) took 43122 ms. Total solver calls (SAT/UNSAT): 41491(34303/7188)

May 31, 2018 5:24:11 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(398/1135) took 46593 ms. Total solver calls (SAT/UNSAT): 42986(35376/7610)

May 31, 2018 5:24:14 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(418/1135) took 49596 ms. Total solver calls (SAT/UNSAT): 44036(36092/7944)

May 31, 2018 5:24:18 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(448/1135) took 52743 ms. Total solver calls (SAT/UNSAT): 45584(37229/8355)

May 31, 2018 5:24:22 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(484/1135) took 56735 ms. Total solver calls (SAT/UNSAT): 47438(38194/9244)

May 31, 2018 5:24:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(492/1135) took 59880 ms. Total solver calls (SAT/UNSAT): 48090(38276/9814)

May 31, 2018 5:24:29 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(496/1135) took 64309 ms. Total solver calls (SAT/UNSAT): 48409(38353/10056)

May 31, 2018 5:24:33 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(498/1135) took 67682 ms. Total solver calls (SAT/UNSAT): 48594(38427/10167)

May 31, 2018 5:24:37 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(500/1135) took 71936 ms. Total solver calls (SAT/UNSAT): 48775(38501/10274)

May 31, 2018 5:24:40 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(503/1135) took 75395 ms. Total solver calls (SAT/UNSAT): 49016(38639/10377)

May 31, 2018 5:24:43 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(517/1135) took 78524 ms. Total solver calls (SAT/UNSAT): 49692(38974/10718)

May 31, 2018 5:24:46 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(526/1135) took 81539 ms. Total solver calls (SAT/UNSAT): 50471(39457/11014)

May 31, 2018 5:24:50 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(534/1135) took 84743 ms. Total solver calls (SAT/UNSAT): 51186(39957/11229)

May 31, 2018 5:24:53 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(590/1135) took 87749 ms. Total solver calls (SAT/UNSAT): 53795(40317/13478)

May 31, 2018 5:24:56 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(633/1135) took 90754 ms. Total solver calls (SAT/UNSAT): 55547(41848/13699)

May 31, 2018 5:24:59 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(684/1135) took 93808 ms. Total solver calls (SAT/UNSAT): 57145(43446/13699)

May 31, 2018 5:25:02 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(743/1135) took 96934 ms. Total solver calls (SAT/UNSAT): 59067(45368/13699)

May 31, 2018 5:25:05 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(786/1135) took 99967 ms. Total solver calls (SAT/UNSAT): 61106(47407/13699)

May 31, 2018 5:25:08 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(835/1135) took 102970 ms. Total solver calls (SAT/UNSAT): 63095(49341/13754)

May 31, 2018 5:25:11 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(884/1135) took 106069 ms. Total solver calls (SAT/UNSAT): 64762(50923/13839)

May 31, 2018 5:25:14 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(890/1135) took 109290 ms. Total solver calls (SAT/UNSAT): 65197(51127/14070)

May 31, 2018 5:25:17 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(956/1135) took 112298 ms. Total solver calls (SAT/UNSAT): 66703(52291/14412)

May 31, 2018 5:25:20 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(1074/1135) took 115340 ms. Total solver calls (SAT/UNSAT): 67801(52878/14923)

May 31, 2018 5:25:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 118337 ms. Total solver calls (SAT/UNSAT): 68802(53198/15604)

May 31, 2018 5:25:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 1135 transitions.

May 31, 2018 5:25:40 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 16577 ms. Total solver calls (SAT/UNSAT): 9149(0/9149)

May 31, 2018 5:25:40 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 138246ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ASLink-PT-04b"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/ASLink-PT-04b.tgz

mv ASLink-PT-04b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstools"

echo " Input is ASLink-PT-04b, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r272-smll-152749148700071"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;