About the Execution of ITS-Tools.L for QuasiCertifProtocol-PT-06

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15743.650 | 91271.00 | 202566.00 | 615.40 | FFFFFFFFFFFFFFFT | normal |

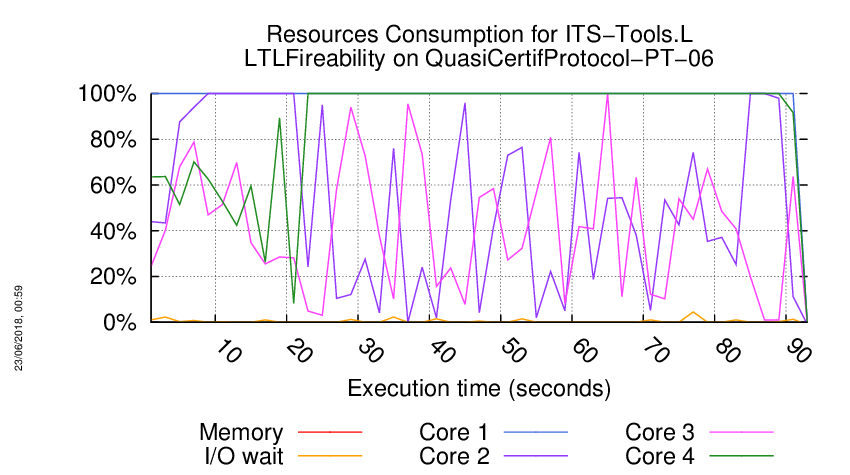

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

............................

/home/mcc/execution

total 400K

-rw-r--r-- 1 mcc users 5.9K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 30K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 5.4K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 31K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 3.2K May 26 09:27 LTLCardinality.txt

-rw-r--r-- 1 mcc users 14K May 26 09:27 LTLCardinality.xml

-rw-r--r-- 1 mcc users 3.1K May 26 09:27 LTLFireability.txt

-rw-r--r-- 1 mcc users 15K May 26 09:27 LTLFireability.xml

-rw-r--r-- 1 mcc users 7.1K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 33K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 116 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 354 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 5.0K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 26K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 2.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 6.3K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 3 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 153K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstoolsl

Input is QuasiCertifProtocol-PT-06, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r189-qhx2-152732140800058

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-00

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-01

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-02

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-03

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-04

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-05

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-06

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-07

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-08

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-09

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-10

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-11

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-12

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-13

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-14

FORMULA_NAME QuasiCertifProtocol-PT-06-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1528316060171

Converted graph to binary with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.201805241334/bin/convert-linux64, -i, /tmp/graph7283376773731977730.txt, -o, /tmp/graph7283376773731977730.bin, -w, /tmp/graph7283376773731977730.weights], workingDir=null]

Built communities with : CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.louvain.binaries_1.0.0.201805241334/bin/louvain-linux64, /tmp/graph7283376773731977730.bin, -l, -1, -v, -w, /tmp/graph7283376773731977730.weights, -q, 0, -e, 0.001], workingDir=null]

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ltl-linux64, --gc-threshold, 2000000, -i, /home/mcc/execution/LTLFireability.pnml.gal, -t, CGAL, -LTL, /home/mcc/execution/LTLFireability.ltl, -c, -stutter-deadlock], workingDir=/home/mcc/execution]

its-ltl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ltl-linux64 --gc-threshold 2000000 -i /home/mcc/execution/LTLFireability.pnml.gal -t CGAL -LTL /home/mcc/execution/LTLFireability.ltl -c -stutter-deadlock

Read 16 LTL properties

Checking formula 0 : !((X(G((G("((((((((((((((i1.u5.n8_4_6>=1)&&(i1.u5.n8_4_5>=1))&&(i1.u5.n8_4_4>=1))&&(i1.u5.n8_4_3>=1))&&(i1.u5.n8_4_2>=1))&&(i1.u5.n8_4_1>=1))&&(i1.u5.n8_4_0>=1))&&(u6.s5_4>=1))||((((((((i1.u3.n8_3_3>=1)&&(i1.u3.n8_3_4>=1))&&(i1.u3.n8_3_5>=1))&&(i1.u3.n8_3_6>=1))&&(u6.s5_3>=1))&&(i1.u3.n8_3_0>=1))&&(i1.u3.n8_3_1>=1))&&(i1.u3.n8_3_2>=1)))||((((((((i1.u7.n8_6_6>=1)&&(i1.u7.n8_6_4>=1))&&(i1.u7.n8_6_5>=1))&&(i1.u7.n8_6_2>=1))&&(i1.u7.n8_6_3>=1))&&(i1.u7.n8_6_0>=1))&&(i1.u7.n8_6_1>=1))&&(u6.s5_6>=1)))||((((((((i1.u4.n8_5_4>=1)&&(i1.u4.n8_5_3>=1))&&(i1.u4.n8_5_2>=1))&&(i1.u4.n8_5_1>=1))&&(i1.u4.n8_5_0>=1))&&(u6.s5_5>=1))&&(i1.u4.n8_5_5>=1))&&(i1.u4.n8_5_6>=1)))||((((((((i1.u44.n8_0_1>=1)&&(i1.u44.n8_0_0>=1))&&(u6.s5_0>=1))&&(i1.u44.n8_0_6>=1))&&(i1.u44.n8_0_3>=1))&&(i1.u44.n8_0_2>=1))&&(i1.u44.n8_0_5>=1))&&(i1.u44.n8_0_4>=1)))||((((((((u6.s5_2>=1)&&(i1.u2.n8_2_4>=1))&&(i1.u2.n8_2_5>=1))&&(i1.u2.n8_2_6>=1))&&(i1.u2.n8_2_0>=1))&&(i1.u2.n8_2_1>=1))&&(i1.u2.n8_2_2>=1))&&(i1.u2.n8_2_3>=1)))||((((((((i1.u1.n8_1_6>=1)&&(i1.u1.n8_1_5>=1))&&(i1.u1.n8_1_2>=1))&&(i1.u1.n8_1_1>=1))&&(i1.u1.n8_1_4>=1))&&(i1.u1.n8_1_3>=1))&&(i1.u1.n8_1_0>=1))&&(u6.s5_1>=1)))"))U(F("((((((((u6.malicious_reservoir>=1)&&(i1.u3.s6_3>=1))||((u6.malicious_reservoir>=1)&&(i1.u2.s6_2>=1)))||((i1.u1.s6_1>=1)&&(u6.malicious_reservoir>=1)))||((u6.malicious_reservoir>=1)&&(i1.u44.s6_0>=1)))||((u6.malicious_reservoir>=1)&&(i1.u7.s6_6>=1)))||((u6.malicious_reservoir>=1)&&(i1.u4.s6_5>=1)))||((u6.malicious_reservoir>=1)&&(i1.u5.s6_4>=1)))"))))))

Formula 0 simplified : !XG(G"((((((((((((((i1.u5.n8_4_6>=1)&&(i1.u5.n8_4_5>=1))&&(i1.u5.n8_4_4>=1))&&(i1.u5.n8_4_3>=1))&&(i1.u5.n8_4_2>=1))&&(i1.u5.n8_4_1>=1))&&(i1.u5.n8_4_0>=1))&&(u6.s5_4>=1))||((((((((i1.u3.n8_3_3>=1)&&(i1.u3.n8_3_4>=1))&&(i1.u3.n8_3_5>=1))&&(i1.u3.n8_3_6>=1))&&(u6.s5_3>=1))&&(i1.u3.n8_3_0>=1))&&(i1.u3.n8_3_1>=1))&&(i1.u3.n8_3_2>=1)))||((((((((i1.u7.n8_6_6>=1)&&(i1.u7.n8_6_4>=1))&&(i1.u7.n8_6_5>=1))&&(i1.u7.n8_6_2>=1))&&(i1.u7.n8_6_3>=1))&&(i1.u7.n8_6_0>=1))&&(i1.u7.n8_6_1>=1))&&(u6.s5_6>=1)))||((((((((i1.u4.n8_5_4>=1)&&(i1.u4.n8_5_3>=1))&&(i1.u4.n8_5_2>=1))&&(i1.u4.n8_5_1>=1))&&(i1.u4.n8_5_0>=1))&&(u6.s5_5>=1))&&(i1.u4.n8_5_5>=1))&&(i1.u4.n8_5_6>=1)))||((((((((i1.u44.n8_0_1>=1)&&(i1.u44.n8_0_0>=1))&&(u6.s5_0>=1))&&(i1.u44.n8_0_6>=1))&&(i1.u44.n8_0_3>=1))&&(i1.u44.n8_0_2>=1))&&(i1.u44.n8_0_5>=1))&&(i1.u44.n8_0_4>=1)))||((((((((u6.s5_2>=1)&&(i1.u2.n8_2_4>=1))&&(i1.u2.n8_2_5>=1))&&(i1.u2.n8_2_6>=1))&&(i1.u2.n8_2_0>=1))&&(i1.u2.n8_2_1>=1))&&(i1.u2.n8_2_2>=1))&&(i1.u2.n8_2_3>=1)))||((((((((i1.u1.n8_1_6>=1)&&(i1.u1.n8_1_5>=1))&&(i1.u1.n8_1_2>=1))&&(i1.u1.n8_1_1>=1))&&(i1.u1.n8_1_4>=1))&&(i1.u1.n8_1_3>=1))&&(i1.u1.n8_1_0>=1))&&(u6.s5_1>=1)))" U F"((((((((u6.malicious_reservoir>=1)&&(i1.u3.s6_3>=1))||((u6.malicious_reservoir>=1)&&(i1.u2.s6_2>=1)))||((i1.u1.s6_1>=1)&&(u6.malicious_reservoir>=1)))||((u6.malicious_reservoir>=1)&&(i1.u44.s6_0>=1)))||((u6.malicious_reservoir>=1)&&(i1.u7.s6_6>=1)))||((u6.malicious_reservoir>=1)&&(i1.u4.s6_5>=1)))||((u6.malicious_reservoir>=1)&&(i1.u5.s6_4>=1)))")

built 21 ordering constraints for composite.

built 35 ordering constraints for composite.

built 20 ordering constraints for composite.

built 12 ordering constraints for composite.

built 20 ordering constraints for composite.

built 20 ordering constraints for composite.

built 8 ordering constraints for composite.

built 20 ordering constraints for composite.

built 20 ordering constraints for composite.

built 20 ordering constraints for composite.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 116 rows 270 cols

invariant :i6:u31:n7_2_1 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_6 = 0

invariant :i1:u5:n8_4_2 + -1'i1:u5:n8_4_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i6:u31:n7_2_5 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u2:n8_2_3 + -1'i1:u2:n8_2_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u2:n8_2_2 + -1'i1:u2:n8_2_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i2:u11:n7_3_0 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_6 = 0

invariant :i6:u31:n7_2_2 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_6 = 0

invariant :i4:u41:n7_6_4 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_4 + i10:u10:n7_4_6 = 0

invariant :i1:u44:Cstart_2 + -1'i1:u7:Cstart_1 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_2 = 0

invariant :i2:u11:n7_3_3 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_6 = 0

invariant :i1:u2:n8_2_0 + -1'i1:u2:n8_2_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i3:u23:n1_1 + i3:u23:n2_1 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :i1:u18:n9_0_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i8:u33:n4_5 + i8:u33:n3_5 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i4:u41:n7_6_0 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_6 = 0

invariant :i4:u41:n7_6_2 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_6 = 0

invariant :i2:u11:n7_3_4 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_4 + i10:u10:n7_4_6 = 0

invariant :i1:u4:Cstart_5 + -1'i1:u7:Cstart_1 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u17:n9_6_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u17:n9_1_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u19:n9_0_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u4:SstopOK_5 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u5:Cstart_4 + -1'i1:u7:Cstart_1 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_4 = 0

invariant :i1:u1:n8_1_2 + -1'i1:u1:n8_1_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u17:n9_2_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u5:SstopOK_4 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i6:u29:n2_2 + i6:u29:n1_2 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :u0:CstopAbort + u6:malicious_reservoir + -1'u6:s5_1 + -1'u6:s5_0 + -1'u6:s5_3 + -1'u6:s5_2 + -1'u6:s5_5 + -1'u6:s5_4 + -1'u6:s5_6 + -1'u6:s3_3 + -1'u6:s2_3 + -1'u6:Sstart_3 + -1'i1:u1:s6_1 + -1'i1:u3:s6_3 + -1'i1:u2:s6_2 + -1'i1:u5:s6_4 + -1'i1:u4:s6_5 + -1'i1:u44:s6_0 + -1'i1:u7:s6_6 + -1'i1:u22:n9_1_2 + -1'i1:u22:n9_2_2 + -1'i1:u22:n9_3_2 + -1'i1:u22:n9_4_2 + -1'i1:u22:n9_0_2 + -1'i1:u22:n9_6_2 + -1'i1:u22:n9_5_2 + -7'i1:u22:CstopOK_2 + -1'i2:u11:s4_3 + -1'i3:u9:s4_1 + -1'i3:u23:s2_1 + -1'i3:u23:Sstart_1 + -1'i3:u35:s3_1 + -1'i4:u25:Sstart_6 + -1'i4:u30:s2_6 + -1'i4:u41:s4_6 + -1'i4:u41:s3_6 + -1'i6:u29:s2_2 + -1'i6:u29:Sstart_2 + -1'i6:u13:s3_2 + -1'i6:u31:s4_2 + -1'i7:u14:s2_0 + -1'i7:u14:Sstart_0 + -1'i7:u37:s3_0 + -1'i7:u8:s4_0 + -1'i8:u12:s4_5 + -1'i8:u26:s2_5 + -1'i8:u26:Sstart_5 + -1'i8:u33:s3_5 + -1'i10:u27:s2_4 + -1'i10:u27:Sstart_4 + -1'i10:u38:s3_4 + -1'i10:u10:s4_4 = -4

invariant :i1:u1:n8_1_1 + -1'i1:u1:n8_1_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u3:Cstart_3 + -1'i1:u7:Cstart_1 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_1 = 0

invariant :i1:u7:n8_6_0 + -1'i1:u7:n8_6_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i8:u12:n7_5_4 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_4 + i10:u10:n7_4_6 = 0

invariant :i3:u39:AstopOK + i5:u15:a5 + i5:u15:a2 + i5:u15:a4 + i5:u15:a3 + i5:u15:AstopAbort + i5:u15:a1 + i5:u28:Astart = 1

invariant :i7:u37:n3_0 + i7:u37:n4_0 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i3:u9:n7_1_1 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_6 = 0

invariant :i1:u44:n8_0_6 + -1'i1:u44:n8_0_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u3:n8_3_4 + -1'i1:u3:n8_3_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i1:u20:n9_1_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i4:u41:n7_6_5 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u18:n9_5_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i2:u42:n5_3 + i2:u42:n6_3 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i1:u7:SstopOK_6 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i6:u24:n3_2 + i6:u24:n4_2 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i5:u34:n3_3 + i5:u34:n4_3 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i7:u14:n1_0 + i7:u14:n2_0 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :i5:u28:n2_3 + i5:u28:n1_3 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :i1:u18:n9_6_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u1:SstopOK_1 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u16:n9_2_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u4:n8_5_6 + -1'i1:u4:n8_5_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u2:SstopOK_2 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u19:n9_6_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u4:n8_5_1 + -1'i1:u4:n8_5_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u7:n8_6_4 + -1'i1:u7:n8_6_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i1:u1:n8_1_3 + -1'i1:u1:n8_1_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i8:u12:n7_5_0 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_6 = 0

invariant :i8:u12:n7_5_1 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_6 = 0

invariant :i4:u41:n7_6_3 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_6 = 0

invariant :i1:u3:SstopOK_3 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i3:u35:n3_1 + i3:u35:n4_1 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i6:u31:n7_2_0 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_6 = 0

invariant :i1:u21:n9_2_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u44:n8_0_2 + -1'i1:u44:n8_0_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u7:n8_6_3 + -1'i1:u7:n8_6_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i2:u11:n7_3_1 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_6 = 0

invariant :i1:u18:n9_2_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u21:n9_3_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i8:u12:n7_5_5 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u17:n9_4_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u4:n8_5_0 + -1'i1:u4:n8_5_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i8:u40:n5_5 + i8:u40:n6_5 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i8:u12:n7_5_3 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_6 = 0

invariant :i1:u16:n9_0_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i7:u8:n7_0_3 + -1'i7:u8:n7_0_4 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_4 = 0

invariant :i1:u18:n9_4_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u3:n8_3_6 + -1'i1:u3:n8_3_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u18:n9_1_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u44:n8_0_4 + -1'i1:u44:n8_0_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i4:u41:n5_6 + i4:u41:n6_6 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i1:u19:n9_3_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i7:u8:n7_0_5 + -1'i7:u8:n7_0_4 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i1:u21:n9_4_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u19:n9_2_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i6:u13:n5_2 + i6:u13:n6_2 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i7:u8:n7_0_2 + -1'i7:u8:n7_0_4 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_4 = 0

invariant :i4:u36:n4_6 + i4:u36:n3_6 + -1'i10:u38:n4_4 + -1'i10:u38:n3_4 = 0

invariant :i1:u4:n8_5_4 + -1'i1:u4:n8_5_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :u0:c1_0 + u0:c1_1 + u0:c1_2 + u0:c1_3 + u0:c1_4 + u0:c1_5 + u0:c1_6 + u0:CstopAbort + i1:u18:CstopOK_6 + i1:u16:CstopOK_1 + i1:u17:CstopOK_0 + i1:u19:CstopOK_5 + i1:u20:CstopOK_4 + i1:u21:CstopOK_3 + 7'i1:u7:Cstart_1 + i1:u22:CstopOK_2 + i10:u10:n7_4_0 + i10:u10:n7_4_3 + -6'i10:u10:n7_4_1 + i10:u10:n7_4_2 + i10:u10:n7_4_5 + i10:u10:n7_4_4 + i10:u10:n7_4_6 = 7

invariant :i1:u18:n9_3_6 + i1:u18:CstopOK_6 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u7:n8_6_1 + -1'i1:u7:n8_6_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u5:n8_4_4 + -1'i1:u5:n8_4_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i3:u9:n7_1_5 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u17:n9_0_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u16:n9_4_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i6:u31:n7_2_4 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_4 + i10:u10:n7_4_6 = 0

invariant :i7:u8:n7_0_0 + -1'i7:u8:n7_0_4 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_4 = 0

invariant :i8:u12:n7_5_2 + -1'i8:u12:n7_5_6 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_6 = 0

invariant :i1:u16:n9_1_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u20:n9_0_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u44:n8_0_3 + -1'i1:u44:n8_0_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u19:n9_5_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u19:n9_1_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u7:n8_6_6 + -1'i1:u7:n8_6_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u16:n9_6_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u20:n9_2_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_2_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u20:n9_5_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u3:n8_3_3 + -1'i1:u3:n8_3_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u2:n8_2_4 + -1'i1:u2:n8_2_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i1:u17:n9_3_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u2:n8_2_6 + -1'i1:u2:n8_2_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u5:n8_4_0 + -1'i1:u5:n8_4_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u1:Cstart_6 + -1'i1:u7:Cstart_1 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_6 = 0

invariant :i2:u11:n7_3_2 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_6 = 0

invariant :i3:u9:n7_1_2 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_2 + i10:u10:n7_4_6 = 0

invariant :i1:u1:n8_1_4 + -1'i1:u1:n8_1_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_4 = 0

invariant :i1:u7:n8_6_2 + -1'i1:u7:n8_6_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u20:n9_3_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :u6:SstopAbort + u6:s5_1 + u6:s5_0 + u6:s5_3 + u6:s5_2 + u6:s5_5 + u6:s5_4 + u6:s5_6 + u6:s3_3 + u6:s2_3 + u6:Sstart_3 + i1:u1:s6_1 + i1:u3:s6_3 + i1:u2:s6_2 + i1:u5:s6_4 + i1:u4:s6_5 + i1:u44:s6_0 + i1:u7:s6_6 + i1:u22:n9_1_2 + i1:u22:n9_2_2 + i1:u22:n9_3_2 + i1:u22:n9_4_2 + i1:u22:n9_0_2 + i1:u22:n9_6_2 + i1:u22:n9_5_2 + 7'i1:u22:CstopOK_2 + i2:u11:s4_3 + i3:u9:s4_1 + i3:u23:s2_1 + i3:u23:Sstart_1 + i3:u35:s3_1 + i4:u25:Sstart_6 + i4:u30:s2_6 + i4:u41:s4_6 + i4:u41:s3_6 + i6:u29:s2_2 + i6:u29:Sstart_2 + i6:u13:s3_2 + i6:u31:s4_2 + i7:u14:s2_0 + i7:u14:Sstart_0 + i7:u37:s3_0 + i7:u8:s4_0 + i8:u12:s4_5 + i8:u26:s2_5 + i8:u26:Sstart_5 + i8:u33:s3_5 + i10:u27:s2_4 + i10:u27:Sstart_4 + i10:u38:s3_4 + i10:u10:s4_4 = 7

invariant :i8:u26:n2_5 + i8:u26:n1_5 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :i1:u2:Cstart_0 + -1'i1:u7:Cstart_1 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_1 = 0

invariant :i1:u20:n9_6_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u2:n8_2_1 + -1'i1:u2:n8_2_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i7:u8:n7_0_1 + -1'i7:u8:n7_0_4 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_4 = 0

invariant :i1:u3:n8_3_0 + -1'i1:u3:n8_3_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u3:n8_3_2 + -1'i1:u3:n8_3_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u1:n8_1_6 + -1'i1:u1:n8_1_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u17:n9_5_0 + i1:u17:CstopOK_0 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u21:n9_1_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_1_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u5:n8_4_6 + -1'i1:u5:n8_4_5 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u4:n8_5_2 + -1'i1:u4:n8_5_5 + i10:u10:n7_4_2 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u44:n8_0_0 + -1'i1:u44:n8_0_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i6:u31:n7_2_3 + -1'i6:u31:n7_2_6 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_6 = 0

invariant :i1:u16:n9_3_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_3_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u16:n9_5_1 + i1:u16:CstopOK_1 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u20:n9_4_4 + i1:u20:CstopOK_4 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u1:n8_1_0 + -1'i1:u1:n8_1_5 + i10:u10:n7_4_0 + -1'i10:u10:n7_4_5 = 0

invariant :i7:u8:n7_0_6 + -1'i7:u8:n7_0_4 + i10:u10:n7_4_4 + -1'i10:u10:n7_4_6 = 0

invariant :i1:u5:n8_4_3 + -1'i1:u5:n8_4_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i3:u39:n5_1 + i3:u39:n6_1 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i1:u5:n8_4_1 + -1'i1:u5:n8_4_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i3:u9:n7_1_3 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_3 + i10:u10:n7_4_6 = 0

invariant :i1:u19:n9_4_5 + i1:u19:CstopOK_5 + -1'i1:u22:n9_4_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u21:n9_0_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i3:u9:n7_1_4 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_4 + i10:u10:n7_4_6 = 0

invariant :i3:u9:n7_1_0 + -1'i3:u9:n7_1_6 + -1'i10:u10:n7_4_0 + i10:u10:n7_4_6 = 0

invariant :i4:u41:n7_6_1 + -1'i4:u41:n7_6_6 + -1'i10:u10:n7_4_1 + i10:u10:n7_4_6 = 0

invariant :i2:u11:n7_3_5 + -1'i2:u11:n7_3_6 + -1'i10:u10:n7_4_5 + i10:u10:n7_4_6 = 0

invariant :i1:u21:n9_5_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_5_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u21:n9_6_3 + i1:u21:CstopOK_3 + -1'i1:u22:n9_6_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i1:u4:n8_5_3 + -1'i1:u4:n8_5_5 + i10:u10:n7_4_3 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u44:SstopOK_0 + -1'i1:u22:n9_0_2 + -1'i1:u22:CstopOK_2 = 0

invariant :i7:u32:n5_0 + i7:u32:n6_0 + -1'i10:u43:n5_4 + -1'i10:u43:n6_4 = 0

invariant :i4:u25:n2_6 + i4:u30:n1_6 + -1'i10:u27:n2_4 + -1'i10:u27:n1_4 = 0

invariant :i1:u3:n8_3_1 + -1'i1:u3:n8_3_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

invariant :i1:u44:n8_0_1 + -1'i1:u44:n8_0_5 + i10:u10:n7_4_1 + -1'i10:u10:n7_4_5 = 0

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Compilation finished in 4715 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 80 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X([](([]((LTLAP0==true)))U(<>((LTLAP1==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 88 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-00 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(<>((<>((LTLAP2==true)))U((LTLAP3==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 65 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-01 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, ((LTLAP4==true))U(X(((LTLAP5==true))U((LTLAP6==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 83 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-02 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, <>(X((LTLAP7==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 59 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-03 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, ((LTLAP0==true))U(X((LTLAP3==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 65 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-04 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, ([](((LTLAP0==true))U((LTLAP2==true))))U([](X([]((LTLAP8==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 83 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-05 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (LTLAP9==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 149 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-06 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, <>(([](<>((LTLAP7==true))))U((LTLAP10==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 148 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-07 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, (<>([](<>((LTLAP11==true)))))U(X(X([]((LTLAP12==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 85 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-08 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, (X(((LTLAP13==true))U((LTLAP14==true))))U(([]((LTLAP15==true)))U([]((LTLAP16==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 85 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-09 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, ((LTLAP17==true))U([]((LTLAP18==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 138 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-10 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, [](<>(<>(X([]((LTLAP17==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 68 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-11 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X([]([](X([]((LTLAP19==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 93 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-12 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, (X(X(<>((LTLAP20==true)))))U(<>(<>((LTLAP21==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 62 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-13 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, <>(((LTLAP12==true))U(X(X((LTLAP3==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 65 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-14 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (LTLAP22==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 127 ms.

FORMULA QuasiCertifProtocol-PT-06-LTLFireability-15 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1528316151442

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution LTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination LTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Jun 06, 2018 8:14:23 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -louvain, -smt]

Jun 06, 2018 8:14:23 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Jun 06, 2018 8:14:23 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 102 ms

Jun 06, 2018 8:14:23 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 270 places.

Jun 06, 2018 8:14:23 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 116 transitions.

Jun 06, 2018 8:14:23 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 24 ms

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 98 ms

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 56 ms

Begin: Wed Jun 6 20:14:24 2018

Computation of communities with the Newman-Girvan Modularity quality function

level 0:

start computation: Wed Jun 6 20:14:24 2018

network size: 270 nodes, 1720 links, 232 weight

quality increased from -0.0485634 to 0.450123

end computation: Wed Jun 6 20:14:24 2018

level 1:

start computation: Wed Jun 6 20:14:24 2018

network size: 45 nodes, 501 links, 232 weight

quality increased from 0.450123 to 0.500485

end computation: Wed Jun 6 20:14:24 2018

level 2:

start computation: Wed Jun 6 20:14:24 2018

network size: 21 nodes, 271 links, 232 weight

quality increased from 0.500485 to 0.522555

end computation: Wed Jun 6 20:14:24 2018

level 3:

start computation: Wed Jun 6 20:14:24 2018

network size: 11 nodes, 87 links, 232 weight

quality increased from 0.522555 to 0.522555

end computation: Wed Jun 6 20:14:24 2018

End: Wed Jun 6 20:14:24 2018

Total duration: 0 sec

0.522555

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 40 ms

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

Jun 06, 2018 8:14:24 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 47 redundant transitions.

Jun 06, 2018 8:14:24 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/LTLFireability.pnml.gal : 14 ms

Jun 06, 2018 8:14:24 PM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSLTLTools

INFO: Time to serialize properties into /home/mcc/execution/LTLFireability.ltl : 6 ms

Jun 06, 2018 8:14:25 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 116 transitions.

Jun 06, 2018 8:14:25 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 155 place invariants in 90 ms

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 270 variables to be positive in 1086 ms

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 116 transitions.

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/116 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 10 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 116 transitions.

Jun 06, 2018 8:14:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 10 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 06, 2018 8:14:31 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 116 transitions.

Jun 06, 2018 8:14:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(0/116) took 463 ms. Total solver calls (SAT/UNSAT): 104(104/0)

Jun 06, 2018 8:14:35 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(6/116) took 3572 ms. Total solver calls (SAT/UNSAT): 707(707/0)

Jun 06, 2018 8:14:38 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(8/116) took 6974 ms. Total solver calls (SAT/UNSAT): 874(872/2)

Jun 06, 2018 8:14:42 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(10/116) took 10119 ms. Total solver calls (SAT/UNSAT): 1037(1033/4)

Jun 06, 2018 8:14:45 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(13/116) took 13581 ms. Total solver calls (SAT/UNSAT): 1274(1267/7)

Jun 06, 2018 8:14:49 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(21/116) took 17562 ms. Total solver calls (SAT/UNSAT): 1556(1510/46)

Jun 06, 2018 8:14:53 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(24/116) took 21156 ms. Total solver calls (SAT/UNSAT): 1775(1726/49)

Jun 06, 2018 8:14:56 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(27/116) took 24816 ms. Total solver calls (SAT/UNSAT): 1985(1933/52)

Jun 06, 2018 8:15:00 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(30/116) took 28485 ms. Total solver calls (SAT/UNSAT): 2186(2131/55)

Jun 06, 2018 8:15:03 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(33/116) took 31817 ms. Total solver calls (SAT/UNSAT): 2378(2320/58)

Jun 06, 2018 8:15:07 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(37/116) took 35773 ms. Total solver calls (SAT/UNSAT): 2620(2558/62)

Jun 06, 2018 8:15:11 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(40/116) took 39069 ms. Total solver calls (SAT/UNSAT): 2791(2726/65)

Jun 06, 2018 8:15:14 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(48/116) took 42547 ms. Total solver calls (SAT/UNSAT): 3043(2975/68)

Jun 06, 2018 8:15:17 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(52/116) took 46003 ms. Total solver calls (SAT/UNSAT): 3245(3173/72)

Jun 06, 2018 8:15:21 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(64/116) took 50003 ms. Total solver calls (SAT/UNSAT): 3481(3361/120)

Jun 06, 2018 8:15:25 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(67/116) took 53880 ms. Total solver calls (SAT/UNSAT): 3610(3490/120)

Jun 06, 2018 8:15:29 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(72/116) took 57649 ms. Total solver calls (SAT/UNSAT): 3805(3685/120)

Jun 06, 2018 8:15:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(79/116) took 60925 ms. Total solver calls (SAT/UNSAT): 4018(3894/124)

Jun 06, 2018 8:15:36 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(86/116) took 64124 ms. Total solver calls (SAT/UNSAT): 4207(4083/124)

Jun 06, 2018 8:15:39 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(93/116) took 67366 ms. Total solver calls (SAT/UNSAT): 4347(4223/124)

Jun 06, 2018 8:15:42 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(109/116) took 70391 ms. Total solver calls (SAT/UNSAT): 4486(4353/133)

Jun 06, 2018 8:15:42 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 70674 ms. Total solver calls (SAT/UNSAT): 4493(4359/134)

Jun 06, 2018 8:15:42 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 116 transitions.

Jun 06, 2018 8:15:42 PM fr.lip6.move.gal.gal2smt.bmc.NextBMCSolver checkSat

WARNING: SMT solver unexpectedly returned 'unknown' answer, retrying.

Jun 06, 2018 8:15:43 PM fr.lip6.move.gal.gal2smt.bmc.NextBMCSolver checkSat

WARNING: SMT solver unexpectedly returned 'unknown' answer, retrying.

Skipping mayMatrices nes/nds SMT solver raised an error :unknown

java.lang.RuntimeException: SMT solver raised an error :unknown

at fr.lip6.move.gal.gal2smt.bmc.NextBMCSolver.checkSat(NextBMCSolver.java:318)

at fr.lip6.move.gal.gal2smt.bmc.NextBMCSolver.checkSat(NextBMCSolver.java:305)

at fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver.computeDoNotAccord(NecessaryEnablingsolver.java:628)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.printLabels(Gal2PinsTransformerNext.java:538)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.printDependencyMatrix(Gal2PinsTransformerNext.java:209)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.buildBodyFile(Gal2PinsTransformerNext.java:85)

at fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext.transform(Gal2PinsTransformerNext.java:830)

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:71)

at java.lang.Thread.run(Thread.java:748)

Jun 06, 2018 8:15:43 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 78590ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="QuasiCertifProtocol-PT-06"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="itstoolsl"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/QuasiCertifProtocol-PT-06.tgz

mv QuasiCertifProtocol-PT-06 execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstoolsl"

echo " Input is QuasiCertifProtocol-PT-06, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r189-qhx2-152732140800058"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;