About the Execution of LoLA for SimpleLoadBal-PT-10

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 215.590 | 72124.00 | 146134.00 | 242.70 | F | normal |

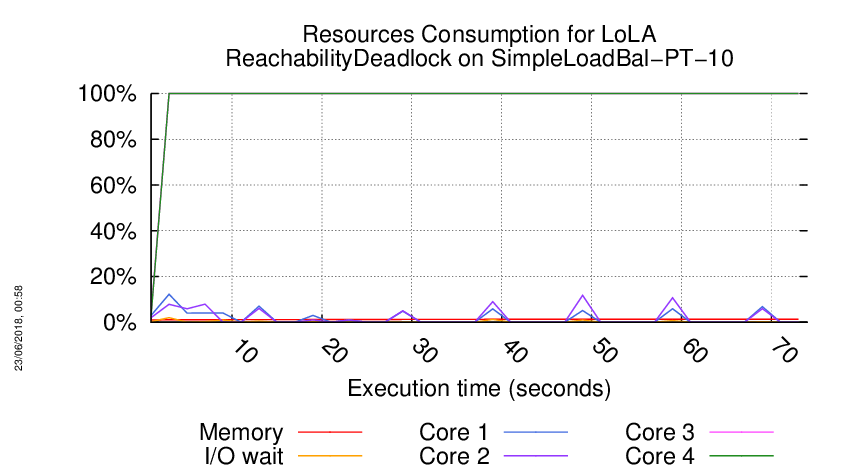

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

..................

/home/mcc/execution

total 700K

-rw-r--r-- 1 mcc users 3.9K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 18K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.8K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 15K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.4K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.7K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 12K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.2K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.6K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.9K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 23K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 110 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 348 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 3.4K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 15K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.9K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 3 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 530K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool lola

Input is SimpleLoadBal-PT-10, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r172-smll-152708743000160

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SimpleLoadBal-PT-10-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1527211087288

info: Time: 3600 - MCC

===========================================================================================

prep: translating SimpleLoadBal-PT-10 Petri net model.pnml into LoLA format

===========================================================================================

prep: translating PT Petri net complete

prep: added safe information to the net based on GenericPropertiesVerdict

prep: check for too many tokens

===========================================================================================

prep: translating SimpleLoadBal-PT-10 formula ReachabilityDeadlock into LoLA format

===========================================================================================

prep: translating PT formula complete

vrfy: Checking ReachabilityDeadlock @ SimpleLoadBal-PT-10 @ 3570 seconds

lola: LoLA will run for 3570 seconds at most (--timelimit)

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 709/65536 symbol table entries, 1 collisions

lola: preprocessing...

lola: Size of bit vector: 104

lola: finding significant places

lola: 104 places, 605 transitions, 75 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 991 transition conflict sets

lola: TASK

lola: reading formula from SimpleLoadBal-PT-10-ReachabilityDeadlock.task

lola: E (F (DEADLOCK))

lola: rewrite Frontend/Parser/formula_rewrite.k:106

lola: checking reachability of deadlocks

lola: Planning: workflow for deadlock check: siphon||findpath||search) (--findpath=par,--siphontrap=par)

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: SEARCH (state space)

lola: state space: using reachability graph (--search=depth)

lola: state space: using deadlock preserving stubborn set method with insertion algorithm(--stubborn=tarjan)

lola: SEARCH (findpath)

lola: findpath: using deadlock preserving stubborn set method with insertion algorithm (--stubborn=tarjan)

lola: RUNNING

lola: computing symmetries (--symmetry)

lola: time limit for symmetry computation of 300 seconds given (--symmtimelimit)

lola: findpath: starting randomized, memory-less exploration (--search=findpath)

lola: findpath: searching for paths with maximal depth 1000000 (--depthlimit)

lola: findpath: no retry limit given (--retrylimit)

lola: findpath: transitions are chosen randomly

lola: computed 45 generators (10 in search tree, 35 by composition)

lola: representing 3.6288E+06 symmetries

lola: 0 dead branches visited in search tree

lola: STP: formula with 9011 variables and 58012 clauses shipped to Minisat

lola: stp: The siphon/trap property is inconclusive since the generated formula is too short

lola: STP completed || 1 tries, 55217 fired transitions, 0 secs || 67143 markings, 90354 edges, 13429 markings/sec, 0 secs

lola: STP completed || 1 tries, 110472 fired transitions, 5 secs || 135854 markings, 189364 edges, 13742 markings/sec, 5 secs

lola: STP completed || 1 tries, 165763 fired transitions, 10 secs || 206922 markings, 297740 edges, 14214 markings/sec, 10 secs

lola: STP completed || 1 tries, 221100 fired transitions, 15 secs || 282091 markings, 416802 edges, 15034 markings/sec, 15 secs

lola: STP completed || 1 tries, 276400 fired transitions, 20 secs || 361995 markings, 550407 edges, 15981 markings/sec, 20 secs

lola: STP completed || 1 tries, 331663 fired transitions, 25 secs || 447246 markings, 702067 edges, 17050 markings/sec, 25 secs

lola: STP completed || 1 tries, 386920 fired transitions, 30 secs || 536197 markings, 872917 edges, 17790 markings/sec, 30 secs

lola: STP completed || 1 tries, 442103 fired transitions, 35 secs || 624214 markings, 1081785 edges, 17603 markings/sec, 35 secs

lola: STP completed || 1 tries, 497220 fired transitions, 40 secs || 698113 markings, 1308625 edges, 14780 markings/sec, 40 secs

lola: STP completed || 1 tries, 552346 fired transitions, 45 secs || 761541 markings, 1524905 edges, 12686 markings/sec, 45 secs

lola: STP completed || 1 tries, 607446 fired transitions, 50 secs || 813469 markings, 1721120 edges, 10386 markings/sec, 50 secs

lola: STP completed || 1 tries, 662582 fired transitions, 55 secs || 862760 markings, 1902124 edges, 9858 markings/sec, 55 secs

lola: STP completed || 1 tries, 717631 fired transitions, 60 secs || 910076 markings, 2069631 edges, 9463 markings/sec, 60 secs

lola: STP completed || 1 tries, 772647 fired transitions, 65 secs || 950491 markings, 2214739 edges, 8083 markings/sec, 65 secs

FORMULA SimpleLoadBal-PT-10-ReachabilityDeadlock-0 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT SAT_SMT STATE_COMPRESSION STUBBORN_SETS SYMMETRIES TOPOLOGICAL USE_NUPN UNFOLDING_TO_PT

lola: RESULT

lola: result: no

lola: produced by: state space

lola: The net does not have deadlocks.

lola: 963183 markings, 2260347 edges

lola: memory consumption: 59856 KB

lola: time consumption: 72 seconds

BK_STOP 1527211159412

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="SimpleLoadBal-PT-10"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="lola"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/SimpleLoadBal-PT-10.tgz

mv SimpleLoadBal-PT-10 execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool lola"

echo " Input is SimpleLoadBal-PT-10, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r172-smll-152708743000160"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;