About the Execution of M4M.struct for Peterson-PT-4

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 3260.180 | 224576.00 | 457170.00 | 163.90 | ???????????????? | normal |

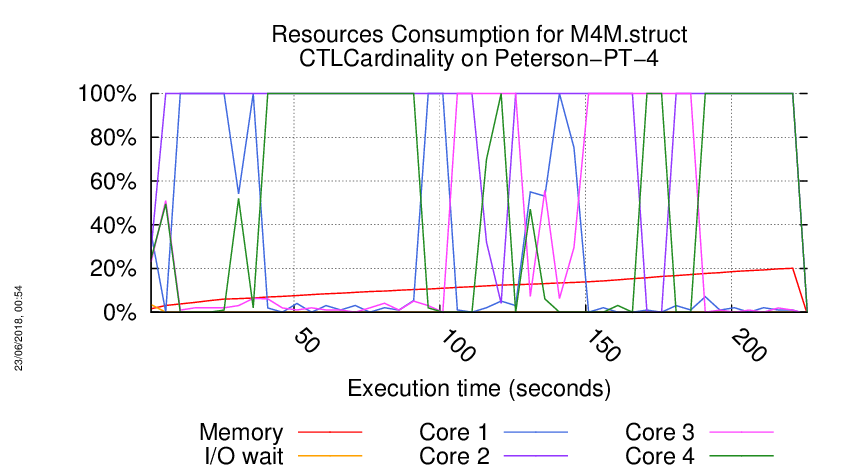

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

...................................

/home/mcc/execution

total 1.3M

-rw-r--r-- 1 mcc users 40K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 114K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 24K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 82K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 20K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 56K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 9.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 32K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 37K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 106K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 104 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 342 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 29K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 100K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 12K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 25K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 5 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 2 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 511K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool mcc4mcc-structural

Input is Peterson-PT-4, examination is CTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r119-csrt-152666480100570

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME Peterson-PT-4-CTLCardinality-00

FORMULA_NAME Peterson-PT-4-CTLCardinality-01

FORMULA_NAME Peterson-PT-4-CTLCardinality-02

FORMULA_NAME Peterson-PT-4-CTLCardinality-03

FORMULA_NAME Peterson-PT-4-CTLCardinality-04

FORMULA_NAME Peterson-PT-4-CTLCardinality-05

FORMULA_NAME Peterson-PT-4-CTLCardinality-06

FORMULA_NAME Peterson-PT-4-CTLCardinality-07

FORMULA_NAME Peterson-PT-4-CTLCardinality-08

FORMULA_NAME Peterson-PT-4-CTLCardinality-09

FORMULA_NAME Peterson-PT-4-CTLCardinality-10

FORMULA_NAME Peterson-PT-4-CTLCardinality-11

FORMULA_NAME Peterson-PT-4-CTLCardinality-12

FORMULA_NAME Peterson-PT-4-CTLCardinality-13

FORMULA_NAME Peterson-PT-4-CTLCardinality-14

FORMULA_NAME Peterson-PT-4-CTLCardinality-15

=== Now, execution of the tool begins

BK_START 1527331423893

BK_STOP 1527331648469

--------------------

content from stderr:

Prefix is 75f5f979.

Reading known information in /usr/share/mcc4mcc/75f5f979-known.json.

Reading learned information in /usr/share/mcc4mcc/75f5f979-learned.json.

Reading value translations in /usr/share/mcc4mcc/75f5f979-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using Peterson-PT-4 as instance name.

Using Peterson as model name.

Using algorithm or tool bmdt.

Model characteristics are: {'Examination': 'CTLCardinality', 'Place/Transition': True, 'Colored': True, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': True, 'Source Place': False, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': False, 'Conservative': True, 'Sub-Conservative': True, 'Nested Units': False, 'Safe': True, 'Deadlock': False, 'Reversible': True, 'Quasi Live': None, 'Live': None}.

Known tools are: [{'Time': 1351828, 'Memory': 15936.59, 'Tool': 'lola'}, {'Time': 1509035, 'Memory': 5607.04, 'Tool': 'lola'}].

Learned tools are: [{'Tool': 'lola'}].

Learned tool lola is 1.0x far from the best tool lola.

CTLCardinality lola Peterson-PT-4...

Time: 3600 - MCC

----- Start make prepare stdout -----

----- Start make prepare stderr -----

===========================================================================================

Peterson-PT-4: translating PT Petri net model.pnml into LoLA format

===========================================================================================

translating PT Petri net complete

checking for too many tokens

===========================================================================================

Peterson-PT-4: translating PT formula CTLCardinality into LoLA format

===========================================================================================

translating formula complete

touch formulae;

----- Start make result stdout -----

----- Start make result stderr -----

CTLCardinality @ Peterson-PT-4 @ 3540 seconds

Makefile:222: recipe for target 'verify' failed

make: [verify] Error 134 (ignored)

----- Start make result stdout -----

----- Start make result stderr -----

lola: LoLA will run for 3540 seconds at most (--timelimit)

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 1170/65536 symbol table entries, 0 collisions

lola: preprocessing...

lola: finding significant places

lola: 480 places, 690 transitions, 461 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 1055 transition conflict sets

lola: TASK

lola: reading formula from Peterson-PT-4-CTLCardinality.task

lola: ((TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 + 1 <= AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2) OR A (G ((((1 <= IsEndLoop_0_0_0 + IsEndLoop_0_0_1 + IsEndLoop_0_0_2 + IsEndLoop_0_0_3 + IsEndLoop_0_0_4 + IsEndLoop_0_1_0 + IsEndLoop_0_1_1 + IsEndLoop_0_1_2 + IsEndLoop_0_1_3 + IsEndLoop_0_1_4 + IsEndLoop_3_0_0 + IsEndLoop_3_0_1 + IsEndLoop_3_0_2 + IsEndLoop_3_0_3 + IsEndLoop_3_0_4 + IsEndLoop_0_2_0 + IsEndLoop_0_2_1 + IsEndLoop_0_2_2 + IsEndLoop_0_2_3 + IsEndLoop_0_2_4 + IsEndLoop_3_1_0 + IsEndLoop_3_1_1 + IsEndLoop_3_1_2 + IsEndLoop_3_1_3 + IsEndLoop_3_1_4 + IsEndLoop_0_3_0 + IsEndLoop_0_3_1 + IsEndLoop_0_3_2 + IsEndLoop_0_3_3 + IsEndLoop_0_3_4 + IsEndLoop_3_2_0 + IsEndLoop_3_2_1 + IsEndLoop_3_2_2 + IsEndLoop_3_2_3 + IsEndLoop_3_2_4 + IsEndLoop_3_3_0 + IsEndLoop_3_3_1 + IsEndLoop_3_3_2 + IsEndLoop_3_3_3 + IsEndLoop_3_3_4 + IsEndLoop_1_0_0 + IsEndLoop_1_0_1 + IsEndLoop_1_0_2 + IsEndLoop_1_0_3 + IsEndLoop_1_0_4 + IsEndLoop_1_1_0 + IsEndLoop_1_1_1 + IsEndLoop_1_1_2 + IsEndLoop_1_1_3 + IsEndLoop_1_1_4 + IsEndLoop_4_0_0 + IsEndLoop_4_0_1 + IsEndLoop_4_0_2 + IsEndLoop_4_0_3 + IsEndLoop_4_0_4 + IsEndLoop_1_2_0 + IsEndLoop_1_2_1 + IsEndLoop_1_2_2 + IsEndLoop_1_2_3 + IsEndLoop_1_2_4 + IsEndLoop_4_1_0 + IsEndLoop_4_1_1 + IsEndLoop_4_1_2 + IsEndLoop_4_1_3 + IsEndLoop_4_1_4 + IsEndLoop_1_3_0 + IsEndLoop_1_3_1 + IsEndLoop_1_3_2 + IsEndLoop_1_3_3 + IsEndLoop_1_3_4 + IsEndLoop_4_2_0 + IsEndLoop_4_2_1 + IsEndLoop_4_2_2 + IsEndLoop_4_2_3 + IsEndLoop_4_2_4 + IsEndLoop_4_3_0 + IsEndLoop_4_3_1 + IsEndLoop_4_3_2 + IsEndLoop_4_3_3 + IsEndLoop_4_3_4 + IsEndLoop_2_0_0 + IsEndLoop_2_0_1 + IsEndLoop_2_0_2 + IsEndLoop_2_0_3 + IsEndLoop_2_0_4 + IsEndLoop_2_1_0 + IsEndLoop_2_1_1 + IsEndLoop_2_1_2 + IsEndLoop_2_1_3 + IsEndLoop_2_1_4 + IsEndLoop_2_2_0 + IsEndLoop_2_2_1 + IsEndLoop_2_2_2 + IsEndLoop_2_2_3 + IsEndLoop_2_2_4 + IsEndLoop_2_3_0 + IsEndLoop_2_3_1 + IsEndLoop_2_3_2 + IsEndLoop_2_3_3 + IsEndLoop_2_3_4) AND (CS_0 + CS_1 + CS_2 + CS_3 + CS_4 <= EndTurn_0_2 + EndTurn_1_0 + EndTurn_1_1 + EndTurn_1_2 + EndTurn_1_3 + EndTurn_0_1 + EndTurn_2_0 + EndTurn_2_1 + EndTurn_2_2 + EndTurn_2_3 + EndTurn_3_0 + EndTurn_3_1 + EndTurn_3_2 + EndTurn_3_3 + EndTurn_4_0 + EndTurn_4_1 + EndTurn_4_2 + EndTurn_4_3 + EndTurn_0_0 + EndTurn_0_3)) OR (CS_0 + CS_1 + CS_2 + CS_3 + CS_4 <= 1))))) : E (G (((TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 <= CS_0 + CS_1 + CS_2 + CS_3 + CS_4) OR (2 <= TestAlone_4_3_0 + TestAlone_4_3_1 + TestAlone_4_3_2 + TestAlone_4_3_3 + TestAlone_2_0_0 + TestAlone_2_0_1 + TestAlone_2_0_3 + TestAlone_2_0_4 + TestAlone_2_1_0 + TestAlone_2_1_1 + TestAlone_2_1_3 + TestAlone_2_1_4 + TestAlone_2_2_0 + TestAlone_2_2_1 + TestAlone_2_2_3 + TestAlone_2_2_4 + TestAlone_2_3_0 + TestAlone_2_3_1 + TestAlone_2_3_3 + TestAlone_2_3_4 + TestAlone_0_0_1 + TestAlone_0_0_2 + TestAlone_0_0_3 + TestAlone_0_0_4 + TestAlone_0_1_1 + TestAlone_0_1_2 + TestAlone_0_1_3 + TestAlone_0_1_4 + TestAlone_3_0_0 + TestAlone_3_0_1 + TestAlone_3_0_2 + TestAlone_3_0_4 + TestAlone_4_2_2 + TestAlone_0_2_1 + TestAlone_0_2_2 + TestAlone_0_2_3 + TestAlone_0_2_4 + TestAlone_3_1_0 + TestAlone_3_1_1 + TestAlone_3_1_2 + TestAlone_3_1_4 + TestAlone_4_2_1 + TestAlone_4_2_0 + TestAlone_0_3_1 + TestAlone_0_3_2 + TestAlone_0_3_3 + TestAlone_0_3_4 + TestAlone_3_2_0 + TestAlone_3_2_1 + TestAlone_3_2_2 + TestAlone_3_2_4 + TestAlone_3_3_0 + TestAlone_3_3_1 + TestAlone_3_3_2 + TestAlone_3_3_4 + TestAlone_1_0_0 + TestAlone_1_0_2 + TestAlone_1_0_3 + TestAlone_1_0_4 + TestAlone_1_1_0 + TestAlone_1_1_2 + TestAlone_1_1_3 + TestAlone_1_1_4 + TestAlone_4_0_0 + TestAlone_4_0_1 + TestAlone_4_0_2 + TestAlone_4_0_3 + TestAlone_1_2_0 + TestAlone_1_2_2 + TestAlone_1_2_3 + TestAlone_1_2_4 + TestAlone_4_1_0 + TestAlone_4_1_1 + TestAlone_4_1_2 + TestAlone_4_1_3 + TestAlone_1_3_0 + TestAlone_1_3_2 + TestAlone_1_3_3 + TestAlone_1_3_4 + TestAlone_4_2_3) OR (3 <= BeginLoop_4_3_0 + BeginLoop_4_3_1 + BeginLoop_4_3_2 + BeginLoop_4_3_3 + BeginLoop_4_3_4 + BeginLoop_2_0_0 + BeginLoop_2_0_1 + BeginLoop_2_0_2 + BeginLoop_2_0_3 + BeginLoop_2_0_4 + BeginLoop_2_1_0 + BeginLoop_2_1_1 + BeginLoop_2_1_2 + BeginLoop_2_1_3 + BeginLoop_2_1_4 + BeginLoop_2_2_0 + BeginLoop_2_2_1 + BeginLoop_2_2_2 + BeginLoop_2_2_3 + BeginLoop_2_2_4 + BeginLoop_2_3_0 + BeginLoop_2_3_1 + BeginLoop_2_3_2 + BeginLoop_2_3_3 + BeginLoop_2_3_4 + BeginLoop_0_0_0 + BeginLoop_0_0_1 + BeginLoop_0_0_2 + BeginLoop_0_0_3 + BeginLoop_0_0_4 + BeginLoop_0_1_0 + BeginLoop_0_1_1 + BeginLoop_0_1_2 + BeginLoop_0_1_3 + BeginLoop_0_1_4 + BeginLoop_3_0_0 + BeginLoop_3_0_1 + BeginLoop_3_0_2 + BeginLoop_3_0_3 + BeginLoop_3_0_4 + BeginLoop_0_2_0 + BeginLoop_0_2_1 + BeginLoop_0_2_2 + BeginLoop_0_2_3 + BeginLoop_0_2_4 + BeginLoop_3_1_0 + BeginLoop_3_1_1 + BeginLoop_3_1_2 + BeginLoop_3_1_3 + BeginLoop_3_1_4 + BeginLoop_0_3_0 + BeginLoop_0_3_1 + BeginLoop_0_3_2 + BeginLoop_0_3_3 + BeginLoop_0_3_4 + BeginLoop_3_2_0 + BeginLoop_3_2_1 + BeginLoop_3_2_2 + BeginLoop_3_2_3 + BeginLoop_3_2_4 + BeginLoop_3_3_0 + BeginLoop_3_3_1 + BeginLoop_3_3_2 + BeginLoop_3_3_3 + BeginLoop_3_3_4 + BeginLoop_4_2_4 + BeginLoop_4_2_3 + BeginLoop_1_0_0 + BeginLoop_1_0_1 + BeginLoop_1_0_2 + BeginLoop_1_0_3 + BeginLoop_1_0_4 + BeginLoop_1_1_0 + BeginLoop_1_1_1 + BeginLoop_1_1_2 + BeginLoop_1_1_3 + BeginLoop_1_1_4 + BeginLoop_4_0_0 + BeginLoop_4_0_1 + BeginLoop_4_0_2 + BeginLoop_4_0_3 + BeginLoop_4_0_4 + BeginLoop_1_2_0 + BeginLoop_1_2_1 + BeginLoop_1_2_2 + BeginLoop_1_2_3 + BeginLoop_1_2_4 + BeginLoop_4_1_0 + BeginLoop_4_1_1 + BeginLoop_4_1_2 + BeginLoop_4_1_3 + BeginLoop_4_1_4 + BeginLoop_4_2_2 + BeginLoop_1_3_0 + BeginLoop_1_3_1 + BeginLoop_1_3_2 + BeginLoop_1_3_3 + BeginLoop_1_3_4 + BeginLoop_4_2_1 + BeginLoop_4_2_0) OR (((TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 <= EndTurn_0_2 + EndTurn_1_0 + EndTurn_1_1 + EndTurn_1_2 + EndTurn_1_3 + EndTurn_0_1 + EndTurn_2_0 + EndTurn_2_1 + EndTurn_2_2 + EndTurn_2_3 + EndTurn_3_0 + EndTurn_3_1 + EndTurn_3_2 + EndTurn_3_3 + EndTurn_4_0 + EndTurn_4_1 + EndTurn_4_2 + EndTurn_4_3 + EndTurn_0_0 + EndTurn_0_3) OR (AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2 <= TestIdentity_1_0_0 + TestIdentity_1_0_1 + TestIdentity_1_0_2 + TestIdentity_1_0_3 + TestIdentity_1_0_4 + TestIdentity_1_1_0 + TestIdentity_1_1_1 + TestIdentity_1_1_2 + TestIdentity_1_1_3 + TestIdentity_1_1_4 + TestIdentity_4_0_0 + TestIdentity_4_0_1 + TestIdentity_4_0_2 + TestIdentity_4_0_3 + TestIdentity_4_0_4 + TestIdentity_1_2_0 + TestIdentity_1_2_1 + TestIdentity_1_2_2 + TestIdentity_1_2_3 + TestIdentity_1_2_4 + TestIdentity_4_1_0 + TestIdentity_4_1_1 + TestIdentity_4_1_2 + TestIdentity_4_1_3 + TestIdentity_4_1_4 + TestIdentity_1_3_0 + TestIdentity_1_3_1 + TestIdentity_1_3_2 + TestIdentity_1_3_3 + TestIdentity_1_3_4 + TestIdentity_4_2_0 + TestIdentity_4_2_1 + TestIdentity_4_2_2 + TestIdentity_4_2_3 + TestIdentity_4_2_4 + TestIdentity_4_3_0 + TestIdentity_4_3_1 + TestIdentity_4_3_2 + TestIdentity_4_3_3 + TestIdentity_4_3_4 + TestIdentity_2_0_0 + TestIdentity_2_0_1 + TestIdentity_2_0_2 + TestIdentity_2_0_3 + TestIdentity_2_0_4 + TestIdentity_2_1_0 + TestIdentity_2_1_1 + TestIdentity_2_1_2 + TestIdentity_2_1_3 + TestIdentity_2_1_4 + TestIdentity_2_2_0 + TestIdentity_2_2_1 + TestIdentity_2_2_2 + TestIdentity_2_2_3 + TestIdentity_2_2_4 + TestIdentity_2_3_0 + TestIdentity_2_3_1 + TestIdentity_2_3_2 + TestIdentity_2_3_3 + TestIdentity_2_3_4 + TestIdentity_0_0_0 + TestIdentity_0_0_1 + TestIdentity_0_0_2 + TestIdentity_0_0_3 + TestIdentity_0_0_4 + TestIdentity_0_1_0 + TestIdentity_0_1_1 + TestIdentity_0_1_2 + TestIdentity_0_1_3 + TestIdentity_0_1_4 + TestIdentity_3_0_0 + TestIdentity_3_0_1 + TestIdentity_3_0_2 + TestIdentity_3_0_3 + TestIdentity_3_0_4 + TestIdentity_0_2_0 + TestIdentity_0_2_1 + TestIdentity_0_2_2 + TestIdentity_0_2_3 + TestIdentity_0_2_4 + TestIdentity_3_1_0 + TestIdentity_3_1_1 + TestIdentity_3_1_2 + TestIdentity_3_1_3 + TestIdentity_3_1_4 + TestIdentity_0_3_0 + TestIdentity_0_3_1 + TestIdentity_0_3_2 + TestIdentity_0_3_3 + TestIdentity_0_3_4 + TestIdentity_3_2_0 + TestIdentity_3_2_1 + TestIdentity_3_2_2 + TestIdentity_3_2_3 + TestIdentity_3_2_4 + TestIdentity_3_3_0 + TestIdentity_3_3_1 + TestIdentity_3_3_2 + TestIdentity_3_3_3 + TestIdentity_3_3_4)) AND (AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2 <= TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3))))) : (((1 <= TestIdentity_1_0_0 + TestIdentity_1_0_1 + TestIdentity_1_0_2 + TestIdentity_1_0_3 + TestIdentity_1_0_4 + TestIdentity_1_1_0 + TestIdentity_1_1_1 + TestIdentity_1_1_2 + TestIdentity_1_1_3 + TestIdentity_1_1_4 + TestIdentity_4_0_0 + TestIdentity_4_0_1 + TestIdentity_4_0_2 + TestIdentity_4_0_3 + TestIdentity_4_0_4 + TestIdentity_1_2_0 + TestIdentity_1_2_1 + TestIdentity_1_2_2 + TestIdentity_1_2_3 + TestIdentity_1_2_4 + TestIdentity_4_1_0 + TestIdentity_4_1_1 + TestIdentity_4_1_2 + TestIdentity_4_1_3 + TestIdentity_4_1_4 + TestIdentity_1_3_0 + TestIdentity_1_3_1 + TestIdentity_1_3_2 + TestIdentity_1_3_3 + TestIdentity_1_3_4 + TestIdentity_4_2_0 + TestIdentity_4_2_1 + TestIdentity_4_2_2 + TestIdentity_4_2_3 + TestIdentity_4_2_4 + TestIdentity_4_3_0 + TestIdentity_4_3_1 + TestIdentity_4_3_2 + TestIdentity_4_3_3 + TestIdentity_4_3_4 + TestIdentity_2_0_0 + TestIdentity_2_0_1 + TestIdentity_2_0_2 + TestIdentity_2_0_3 + TestIdentity_2_0_4 + TestIdentity_2_1_0 + TestIdentity_2_1_1 + TestIdentity_2_1_2 + TestIdentity_2_1_3 + TestIdentity_2_1_4 + TestIdentity_2_2_0 + TestIdentity_2_2_1 + TestIdentity_2_2_2 + TestIdentity_2_2_3 + TestIdentity_2_2_4 + TestIdentity_2_3_0 + TestIdentity_2_3_1 + TestIdentity_2_3_2 + TestIdentity_2_3_3 + TestIdentity_2_3_4 + TestIdentity_0_0_0 + TestIdentity_0_0_1 + TestIdentity_0_0_2 + TestIdentity_0_0_3 + TestIdentity_0_0_4 + TestIdentity_0_1_0 + TestIdentity_0_1_1 + TestIdentity_0_1_2 + TestIdentity_0_1_3 + TestIdentity_0_1_4 + TestIdentity_3_0_0 + TestIdentity_3_0_1 + TestIdentity_3_0_2 + TestIdentity_3_0_3 + TestIdentity_3_0_4 + TestIdentity_0_2_0 + TestIdentity_0_2_1 + TestIdentity_0_2_2 + TestIdentity_0_2_3 + TestIdentity_0_2_4 + TestIdentity_3_1_0 + TestIdentity_3_1_1 + TestIdentity_3_1_2 + TestIdentity_3_1_3 + TestIdentity_3_1_4 + TestIdentity_0_3_0 + TestIdentity_0_3_1 + TestIdentity_0_3_2 + TestIdentity_0_3_3 + TestIdentity_0_3_4 + TestIdentity_3_2_0 + TestIdentity_3_2_1 + TestIdentity_3_2_2 + TestIdentity_3_2_3 + TestIdentity_3_2_4 + TestIdentity_3_3_0 + TestIdentity_3_3_1 + TestIdentity_3_3_2 + TestIdentity_3_3_3 + TestIdentity_3_3_4)) OR (A (G ((AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2 <= WantSection_4_T + WantSection_4_F + WantSection_3_T + WantSection_3_F + WantSection_2_T + WantSection_2_F + WantSection_1_T + WantSection_1_F + WantSection_0_T + WantSection_0_F))) OR NOT(A (X ((3 <= Idle_0 + Idle_1 + Idle_2 + Idle_3 + Idle_4)))))) : ((E (F ((3 <= IsEndLoop_0_0_0 + IsEndLoop_0_0_1 + IsEndLoop_0_0_2 + IsEndLoop_0_0_3 + IsEndLoop_0_0_4 + IsEndLoop_0_1_0 + IsEndLoop_0_1_1 + IsEndLoop_0_1_2 + IsEndLoop_0_1_3 + IsEndLoop_0_1_4 + IsEndLoop_3_0_0 + IsEndLoop_3_0_1 + IsEndLoop_3_0_2 + IsEndLoop_3_0_3 + IsEndLoop_3_0_4 + IsEndLoop_0_2_0 + IsEndLoop_0_2_1 + IsEndLoop_0_2_2 + IsEndLoop_0_2_3 + IsEndLoop_0_2_4 + IsEndLoop_3_1_0 + IsEndLoop_3_1_1 + IsEndLoop_3_1_2 + IsEndLoop_3_1_3 + IsEndLoop_3_1_4 + IsEndLoop_0_3_0 + IsEndLoop_0_3_1 + IsEndLoop_0_3_2 + IsEndLoop_0_3_3 + IsEndLoop_0_3_4 + IsEndLoop_3_2_0 + IsEndLoop_3_2_1 + IsEndLoop_3_2_2 + IsEndLoop_3_2_3 + IsEndLoop_3_2_4 + IsEndLoop_3_3_0 + IsEndLoop_3_3_1 + IsEndLoop_3_3_2 + IsEndLoop_3_3_3 + IsEndLoop_3_3_4 + IsEndLoop_1_0_0 + IsEndLoop_1_0_1 + IsEndLoop_1_0_2 + IsEndLoop_1_0_3 + IsEndLoop_1_0_4 + IsEndLoop_1_1_0 + IsEndLoop_1_1_1 + IsEndLoop_1_1_2 + IsEndLoop_1_1_3 + IsEndLoop_1_1_4 + IsEndLoop_4_0_0 + IsEndLoop_4_0_1 + IsEndLoop_4_0_2 + IsEndLoop_4_0_3 + IsEndLoop_4_0_4 + IsEndLoop_1_2_0 + IsEndLoop_1_2_1 + IsEndLoop_1_2_2 + IsEndLoop_1_2_3 + IsEndLoop_1_2_4 + IsEndLoop_4_1_0 + IsEndLoop_4_1_1 + IsEndLoop_4_1_2 + IsEndLoop_4_1_3 + IsEndLoop_4_1_4 + IsEndLoop_1_3_0 + IsEndLoop_1_3_1 + IsEndLoop_1_3_2 + IsEndLoop_1_3_3 + IsEndLoop_1_3_4 + IsEndLoop_4_2_0 + IsEndLoop_4_2_1 + IsEndLoop_4_2_2 + IsEndLoop_4_2_3 + IsEndLoop_4_2_4 + IsEndLoop_4_3_0 + IsEndLoop_4_3_1 + IsEndLoop_4_3_2 + IsEndLoop_4_3_3 + IsEndLoop_4_3_4 + IsEndLoop_2_0_0 + IsEndLoop_2_0_1 + IsEndLoop_2_0_2 + IsEndLoop_2_0_3 + IsEndLoop_2_0_4 + IsEndLoop_2_1_0 + IsEndLoop_2_1_1 + IsEndLoop_2_1_2 + IsEndLoop_2_1_3 + IsEndLoop_2_1_4 + IsEndLoop_2_2_0 + IsEndLoop_2_2_1 + IsEndLoop_2_2_2 + IsEndLoop_2_2_3 + IsEndLoop_2_2_4 + IsEndLoop_2_3_0 + IsEndLoop_2_3_1 + IsEndLoop_2_3_2 + IsEndLoop_2_3_3 + IsEndLoop_2_3_4))) OR ((3 <= TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3) AND ((Turn_2_0 + Turn_2_1 + Turn_2_2 + Turn_2_3 + Turn_3_0 + Turn_3_1 + Turn_3_2 + Turn_3_3 + Turn_1_3 + Turn_1_2 + Turn_1_1 + Turn_1_0 + Turn_0_0 + Turn_0_1 + Turn_0_2 + Turn_0_3 + Turn_0_4 + Turn_1_4 + Turn_3_4 + Turn_2_4 <= WantSection_4_T + WantSection_4_F + WantSection_3_T + WantSection_3_F + WantSection_2_T + WantSection_2_F + WantSection_1_T + WantSection_1_F + WantSection_0_T + WantSection_0_F) OR (TestIdentity_1_0_0 + TestIdentity_1_0_1 + TestIdentity_1_0_2 + TestIdentity_1_0_3 + TestIdentity_1_0_4 + TestIdentity_1_1_0 + TestIdentity_1_1_1 + TestIdentity_1_1_2 + TestIdentity_1_1_3 + TestIdentity_1_1_4 + TestIdentity_4_0_0 + TestIdentity_4_0_1 + TestIdentity_4_0_2 + TestIdentity_4_0_3 + TestIdentity_4_0_4 + TestIdentity_1_2_0 + TestIdentity_1_2_1 + TestIdentity_1_2_2 + TestIdentity_1_2_3 + TestIdentity_1_2_4 + TestIdentity_4_1_0 + TestIdentity_4_1_1 + TestIdentity_4_1_2 + TestIdentity_4_1_3 + TestIdentity_4_1_4 + TestIdentity_1_3_0 + TestIdentity_1_3_1 + TestIdentity_1_3_2 + TestIdentity_1_3_3 + TestIdentity_1_3_4 + TestIdentity_4_2_0 + TestIdentity_4_2_1 + TestIdentity_4_2_2 + TestIdentity_4_2_3 + TestIdentity_4_2_4 + TestIdentity_4_3_0 + TestIdentity_4_3

_1 + TestIdentity_4_3_2 + TestIdentity_4_3_3 + TestIdentity_4_3_4 + TestIdentity_2_0_0 + TestIdentity_2_0_1 + TestIdentity_2_0_2 + TestIdentity_2_0_3 + TestIdentity_2_0_4 + TestIdentity_2_1_0 + TestIdentity_2_1_1 + TestIdentity_2_1_2 + TestIdentity_2_1_3 + TestIdentity_2_1_4 + TestIdentity_2_2_0 + TestIdentity_2_2_1 + TestIdentity_2_2_2 + TestIdentity_2_2_3 + TestIdentity_2_2_4 + TestIdentity_2_3_0 + TestIdentity_2_3_1 + TestIdentity_2_3_2 + TestIdentity_2_3_3 + TestIdentity_2_3_4 + TestIdentity_0_0_0 + TestIdentity_0_0_1 + TestIdentity_0_0_2 + TestIdentity_0_0_3 + TestIdentity_0_0_4 + TestIdentity_0_1_0 + TestIdentity_0_1_1 + TestIdentity_0_1_2 + TestIdentity_0_1_3 + TestIdentity_0_1_4 + TestIdentity_3_0_0 + TestIdentity_3_0_1 + TestIdentity_3_0_2 + TestIdentity_3_0_3 + TestIdentity_3_0_4 + TestIdentity_0_2_0 + TestIdentity_0_2_1 + TestIdentity_0_2_2 + TestIdentity_0_2_3 + TestIdentity_0_2_4 + TestIdentity_3_1_0 + TestIdentity_3_1_1 + TestIdentity_3_1_2 + TestIdentity_3_1_3 + TestIdentity_3_1_4 + TestIdentity_0_3_0 + TestIdentity_0_3_1 + TestIdentity_0_3_2 + TestIdentity_0_3_3 + TestIdentity_0_3_4 + TestIdentity_3_2_0 + TestIdentity_3_2_1 + TestIdentity_3_2_2 + TestIdentity_3_2_3 + TestIdentity_3_2_4 + TestIdentity_3_3_0 + TestIdentity_3_3_1 + TestIdentity_3_3_2 + TestIdentity_3_3_3 + TestIdentity_3_3_4 <= Turn_2_0 + Turn_2_1 + Turn_2_2 + Turn_2_3 + Turn_3_0 + Turn_3_1 + Turn_3_2 + Turn_3_3 + Turn_1_3 + Turn_1_2 + Turn_1_1 + Turn_1_0 + Turn_0_0 + Turn_0_1 + Turn_0_2 + Turn_0_3 + Turn_0_4 + Turn_1_4 + Turn_3_4 + Turn_2_4) OR (1 <= WantSection_4_T + WantSection_4_F + WantSection_3_T + WantSection_3_F + WantSection_2_T + WantSection_2_F + WantSection_1_T + WantSection_1_F + WantSection_0_T + WantSection_0_F)))) OR NOT(E (F ((TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 <= IsEndLoop_0_0_0 + IsEndLoop_0_0_1 + IsEndLoop_0_0_2 + IsEndLoop_0_0_3 + IsEndLoop_0_0_4 + IsEndLoop_0_1_0 + IsEndLoop_0_1_1 + IsEndLoop_0_1_2 + IsEndLoop_0_1_3 + IsEndLoop_0_1_4 + IsEndLoop_3_0_0 + IsEndLoop_3_0_1 + IsEndLoop_3_0_2 + IsEndLoop_3_0_3 + IsEndLoop_3_0_4 + IsEndLoop_0_2_0 + IsEndLoop_0_2_1 + IsEndLoop_0_2_2 + IsEndLoop_0_2_3 + IsEndLoop_0_2_4 + IsEndLoop_3_1_0 + IsEndLoop_3_1_1 + IsEndLoop_3_1_2 + IsEndLoop_3_1_3 + IsEndLoop_3_1_4 + IsEndLoop_0_3_0 + IsEndLoop_0_3_1 + IsEndLoop_0_3_2 + IsEndLoop_0_3_3 + IsEndLoop_0_3_4 + IsEndLoop_3_2_0 + IsEndLoop_3_2_1 + IsEndLoop_3_2_2 + IsEndLoop_3_2_3 + IsEndLoop_3_2_4 + IsEndLoop_3_3_0 + IsEndLoop_3_3_1 + IsEndLoop_3_3_2 + IsEndLoop_3_3_3 + IsEndLoop_3_3_4 + IsEndLoop_1_0_0 + IsEndLoop_1_0_1 + IsEndLoop_1_0_2 + IsEndLoop_1_0_3 + IsEndLoop_1_0_4 + IsEndLoop_1_1_0 + IsEndLoop_1_1_1 + IsEndLoop_1_1_2 + IsEndLoop_1_1_3 + IsEndLoop_1_1_4 + IsEndLoop_4_0_0 + IsEndLoop_4_0_1 + IsEndLoop_4_0_2 + IsEndLoop_4_0_3 + IsEndLoop_4_0_4 + IsEndLoop_1_2_0 + IsEndLoop_1_2_1 + IsEndLoop_1_2_2 + IsEndLoop_1_2_3 + IsEndLoop_1_2_4 + IsEndLoop_4_1_0 + IsEndLoop_4_1_1 + IsEndLoop_4_1_2 + IsEndLoop_4_1_3 + IsEndLoop_4_1_4 + IsEndLoop_1_3_0 + IsEndLoop_1_3_1 + IsEndLoop_1_3_2 + IsEndLoop_1_3_3 + IsEndLoop_1_3_4 + IsEndLoop_4_2_0 + IsEndLoop_4_2_1 + IsEndLoop_4_2_2 + IsEndLoop_4_2_3 + IsEndLoop_4_2_4 + IsEndLoop_4_3_0 + IsEndLoop_4_3_1 + IsEndLoop_4_3_2 + IsEndLoop_4_3_3 + IsEndLoop_4_3_4 + IsEndLoop_2_0_0 + IsEndLoop_2_0_1 + IsEndLoop_2_0_2 + IsEndLoop_2_0_3 + IsEndLoop_2_0_4 + IsEndLoop_2_1_0 + IsEndLoop_2_1_1 + IsEndLoop_2_1_2 + IsEndLoop_2_1_3 + IsEndLoop_2_1_4 + IsEndLoop_2_2_0 + IsEndLoop_2_2_1 + IsEndLoop_2_2_2 + IsEndLoop_2_2_3 + IsEndLoop_2_2_4 + IsEndLoop_2_3_0 + IsEndLoop_2_3_1 + IsEndLoop_2_3_2 + IsEndLoop_2_3_3 + IsEndLoop_2_3_4))))) : E (G (E (F ((WantSection_4_T + WantSection_4_F + WantSection_3_T + WantSection_3_F + WantSection_2_T + WantSection_2_F + WantSection_1_T + WantSection_1_F + WantSection_0_T + WantSection_0_F <= 1))))) : A (G (E (F (((1 <= Idle_0 + Idle_1 + Idle_2 + Idle_3 + Idle_4) AND (AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2 <= Idle_0 + Idle_1 + Idle_2 + Idle_3 + Idle_4)))))) : A (G (E (((EndTurn_0_2 + EndTurn_1_0 + EndTurn_1_1 + EndTurn_1_2 + EndTurn_1_3 + EndTurn_0_1 + EndTurn_2_0 + EndTurn_2_1 + EndTurn_2_2 + EndTurn_2_3 + EndTurn_3_0 + EndTurn_3_1 + EndTurn_3_2 + EndTurn_3_3 + EndTurn_4_0 + EndTurn_4_1 + EndTurn_4_2 + EndTurn_4_3 + EndTurn_0_0 + EndTurn_0_3 <= Idle_0 + Idle_1 + Idle_2 + Idle_3 + Idle_4) U (CS_0 + CS_1 + CS_2 + CS_3 + CS_4 <= AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_1_0 + AskForSection_1_1 + AskForSection_1_2 + AskForSection_1_3 + AskForSection_2_0 + AskForSection_2_1 + AskForSection_2_2 + AskForSection_2_3 + AskForSection_3_0 + AskForSection_3_1 + AskForSection_3_2 + AskForSection_3_3 + AskForSection_4_3 + AskForSection_4_0 + AskForSection_4_1 + AskForSection_4_2))))) : (E (F (((1 <= TestAlone_4_3_0 + TestAlone_4_3_1 + TestAlone_4_3_2 + TestAlone_4_3_3 + TestAlone_2_0_0 + TestAlone_2_0_1 + TestAlone_2_0_3 + TestAlone_2_0_4 + TestAlone_2_1_0 + TestAlone_2_1_1 + TestAlone_2_1_3 + TestAlone_2_1_4 + TestAlone_2_2_0 + TestAlone_2_2_1 + TestAlone_2_2_3 + TestAlone_2_2_4 + TestAlone_2_3_0 + TestAlone_2_3_1 + TestAlone_2_3_3 + TestAlone_2_3_4 + TestAlone_0_0_1 + TestAlone_0_0_2 + TestAlone_0_0_3 + TestAlone_0_0_4 + TestAlone_0_1_1 + TestAlone_0_1_2 + TestAlone_0_1_3 + TestAlone_0_1_4 + TestAlone_3_0_0 + TestAlone_3_0_1 + TestAlone_3_0_2 + TestAlone_3_0_4 + TestAlone_4_2_2 + TestAlone_0_2_1 + TestAlone_0_2_2 + TestAlone_0_2_3 + TestAlone_0_2_4 + TestAlone_3_1_0 + TestAlone_3_1_1 + TestAlone_3_1_2 + TestAlone_3_1_4 + TestAlone_4_2_1 + TestAlone_4_2_0 + TestAlone_0_3_1 + TestAlone_0_3_2 + TestAlone_0_3_3 + TestAlone_0_3_4 + TestAlone_3_2_0 + TestAlone_3_2_1 + TestAlone_3_2_2 + TestAlone_3_2_4 + TestAlone_3_3_0 + TestAlone_3_3_1 + TestAlone_3_3_2 + TestAlone_3_3_4 + TestAlone_1_0_0 + TestAlone_1_0_2 + TestAlone_1_0_3 + TestAlone_1_0_4 + TestAlone_1_1_0 + TestAlone_1_1_2 + TestAlone_1_1_3 + TestAlone_1_1_4 + TestAlone_4_0_0 + TestAlone_4_0_1 + TestAlone_4_0_2 + TestAlone_4_0_3 + TestAlone_1_2_0 + TestAlone_1_2_2 + TestAlone_1_2_3 + TestAlone_1_2_4 + TestAlone_4_1_0 + TestAlone_4_1_1 + TestAlone_4_1_2 + TestAlone_4_1_3 + TestAlone_1_3_0 + TestAlone_1_3_2 + TestAlone_1_3_3 + TestAlone_1_3_4 + TestAlone_4_2_3) AND (BeginLoop_4_3_0 + BeginLoop_4_3_1 + BeginLoop_4_3_2 + BeginLoop_4_3_3 + BeginLoop_4_3_4 + BeginLoop_2_0_0 + BeginLoop_2_0_1 + BeginLoop_2_0_2 + BeginLoop_2_0_3 + BeginLoop_2_0_4 + BeginLoop_2_1_0 + BeginLoop_2_1_1 + BeginLoop_2_1_2 + BeginLoop_2_1_3 + BeginLoop_2_1_4 + BeginLoop_2_2_0 + BeginLoop_2_2_1 + BeginLoop_2_2_2 + BeginLoop_2_2_3 + BeginLoop_2_2_4 + BeginLoop_2_3_0 + BeginLoop_2_3_1 + BeginLoop_2_3_2 + BeginLoop_2_3_3 + BeginLoop_2_3_4 + BeginLoop_0_0_0 + BeginLoop_0_0_1 + BeginLoop_0_0_2 + BeginLoop_0_0_3 + BeginLoop_0_0_4 + BeginLoop_0_1_0 + BeginLoop_0_1_1 + BeginLoop_0_1_2 + BeginLoop_0_1_3 + BeginLoop_0_1_4 + BeginLoop_3_0_0 + BeginLoop_3_0_1 + BeginLoop_3_0_2 + BeginLoop_3_0_3 + BeginLoop_3_0_4 + BeginLoop_0_2_0 + BeginLoop_0_2_1 + BeginLoop_0_2_2 + BeginLoop_0_2_3 + BeginLoop_0_2_4 + BeginLoop_3_1_0 + BeginLoop_3_1_1 + BeginLoop_3_1_2 + BeginLoop_3_1_3 + BeginLoop_3_1_4 + BeginLoop_0_3_0 + BeginLoop_0_3_1 + BeginLoop_0_3_2 + BeginLoop_0_3_3 + BeginLoop_0_3_4 + BeginLoop_3_2_0 + BeginLoop_3_2_1 + BeginLoop_3_2_2 + BeginLoop_3_2_3 + BeginLoop_3_2_4 + BeginLoop_3_3_0 + BeginLoop_3_3_1 + BeginLoop_3_3_2 + BeginLoop_3_3_3 + BeginLoop_3_3_4 + BeginLoop_4_2_4 + BeginLoop_4_2_3 + BeginLoop_1_0_0 + BeginLoop_1_0_1 + BeginLoop_1_0_2 + BeginLoop_1_0_3 + BeginLoop_1_0_4 + BeginLoop_1_1_0 + BeginLoop_1_1_1 + BeginLoop_1_1_2 + BeginLoop_1_1_3 + BeginLoop_1_1_4 + BeginLoop_4_0_0 + BeginLoop_4_0_1 + BeginLoop_4_0_2 + BeginLoop_4_0_3 + BeginLoop_4_0_4 + BeginLoop_1_2_0 + BeginLoop_1_2_1 + BeginLoop_1_2_2 + BeginLoop_1_2_3 + BeginLoop_1_2_4 + BeginLoop_4_1_0 + BeginLoop_4_1_1 + BeginLoop_4_1_2 + BeginLoop_4_1_3 + BeginLoop_4_1_4 + BeginLoop_4_2_2 + BeginLoop_1_3_0 + BeginLoop_1_3_1 + BeginLoop_1_3_2 + BeginLoop_1_3_3 + BeginLoop_1_3_4 + BeginLoop_4_2_1 + BeginLoop_4_2_0 <= Idle_0 + Idle_1 + Idle_2 + Idle_3 + Idle_4) AND (TestIdentity_1_0_0 + TestIdentity_1_0_1 + TestIdentity_1_0_2 + TestIdentity_1_0_3 + TestIdentity_1_0_4 + TestIdentity_1_1_0 + TestIdentity_1_1_1 + TestIdentity_1_1_2 + TestIdentity_1_1_3 + TestIdentity_1_1_4 + TestIdentity_4_0_0 + TestIdentity_4_0_1 + TestIdentity_4_0_2 + TestIdentity_4_0_3 + TestIdentity_4_0_4 + TestIdentity_1_2_0 + TestIdentity_1_2_1 + TestIdentity_1_2_2 + TestIdentity_1_2_3 + TestIdentity_1_2_4 + TestIdentity_4_1_0 + TestIdentity_4_1_1 + TestIdentity_4_1_2 + TestIdentity_4_1_3 + TestIdentity_4_1_4 + TestIdentity_1_3_0 + TestIdentity_1_3_1 + TestIdentity_1_3_2 + TestIdentity_1_3_3 + TestIdentity_1_3_4 + TestIdentity_4_2_0 + TestIdentity_4_2_1 + TestIdentity_4_2_2 + TestIdentity_4_2_3 + TestIdentity_4_2_4 + TestIdentity_4_3_0 + TestIdentity_4_3_1 + TestIdentity_4_3_2 + TestIdentity_4_3_3 + TestIdentity_4_3_4 + TestIdentity_2_0_0 + TestIdentity_2_0_1 + TestIdentity_2_0_2 + TestIdentity_2_0_3 + TestIdentity_2_0_4 + TestIdentity_2_1_0 + TestIdentity_2_1_1 + TestIdentity_2_1_2 + TestIdentity_2_1_3 + TestIdentity_2_1_4 + TestIdentity_2_2_0 + TestIdentity_2_2_1 + TestIdentity_2_2_2 + TestIdentity_2_2_3 + TestIdentity_2_2_4 + TestIdentity_2_3_0 + TestIdentity_2_3_1 + TestIdentity_2_3_2 + TestIdentity_2_3_3 + TestIdentity_2_3_4 + TestIdentity_0_0_0 + TestIdentity_0_0_1 + TestIdentity_0_0_2 + TestIdentity_0_0_3 + TestIdentity_0_0_4 + TestIdentity_0_1_0 + TestIdentity_0_1_1 + TestIdentity_0_1_2 + TestIdentity_0_1_3 + TestIdentity_0_1_4 + TestIdentity_3_0_0 + TestIdentity_3_0_1 + TestIdentity_3_0_2 + TestIdentity_3_0_3 + TestIdentity_3_0_4 + TestIdentity_0_2_0 + TestIdentity_0_2_1 + TestIdentity_0_2_2 + TestIdentity_0_2_3 + TestIdentity_0_2_4 + TestIdentity_3_1_0 + TestIdentity_3_1_1 + TestIdentity_3_1_2 + TestIdentity_3_1_3 + TestIdentity_3_1_4 + TestIdentity_0_3_0 + TestIdentity_0_3_1 + TestIdentity_0_3_2 + TestIdentity_0_3_3 + TestIdentity_0_3_4 + TestIdentity_3_2_0 + TestIdentity_3_2_1 + TestIdentity_3_2_2 + TestIdentity_3_2_3 + TestIdentity_3_2_4 + TestIdentity_3_3_0 + TestIdentity_3_3_1 + TestIdentity_3_3_2 + TestIdentity_3_3_3 + TestIdentity_3_3_4 <= 1)))) AND (((TestAlone_4_3_0 + TestAlone_4_3_1 + TestAlone_4_3_2 + TestAlone_4_3_3 + TestAlone_2_0_0 + TestAlone_2_0_1 + TestAlone_2_0_3 + TestAlone_2_0_4 + TestAlone_2_1_0 + TestAlone_2_1_1 + TestAlone_2_1_3 + TestAlone_2_1_4 + TestAlone_2_2_0 + TestAlone_2_2_1 + TestAlone_2_2_3 + TestAlone_2_2_4 + TestAlone_2_3_0 + TestAlone_2_3_1 + TestAlone_2_3_3 + TestAlone_2_3_4 + TestAlone_0_0_1 + TestAlone_0_0_2 + TestAlone_0_0_3 + TestAlone_0_0_4 + TestAlone_0_1_1 + TestAlone_0_1_2 + TestAlone_0_1_3 + TestAlone_0_1_4 + TestAlone_3_0_0 + TestAlone_3_0_1 + TestAlone_3_0_2 + TestAlone_3_0_4 + TestAlone_4_2_2 + TestAlone_0_2_1 + TestAlone_0_2_2 + TestAlone_0_2_3 + TestAlone_0_2_4 + TestAlone_3_1_0 + TestAlone_3_1_1 + TestAlone_3_1_2 + TestAlone_3_1_4 + TestAlone_4_2_1 + TestAlone_4_2_0 + TestAlone_0_3_1 + TestAlone_0_3_2 + TestAlone_0_3_3 + TestAlone_0_3_4 + TestAlone_3_2_0 + TestAlone_3_2_1 + TestAlone_3_2_2 + TestAlone_3_2_4 + TestAlone_3_3_0 + TestAlone_3_3_1 + TestAlone_3_3_2 + TestAlone_3_3_4 + TestAlone_1_0_0 + TestAlone_1_0_2 + TestAlone_1_0_3 + TestAlone_1_0_4 + TestAlone_1_1_0 + TestAlone_1_1_2 + TestAlone_1_1_3 + TestAlone_1_1_4 + TestAlone_4_0_0 + TestAlone_4_0_1 + TestAlone_4_0_2 + TestAlone_4_0_3 + TestAlone_1_2_0 + TestAlone_1_2_2 + TestAlone_1_2_3 + TestAlone_1_2_4 + TestAlone_4_1_0 + TestAlone_4_1_1 + TestAlone_4_1_2 + TestAlone_4_1_3 + TestAlone_1_3_0 + TestAlone_1_3_2 + TestAlone_1_3_3 + TestAlone_1_3_4 + TestAlone_4_2_3 <= Turn_2_0 + Turn_2_1 + Turn_2_2 + Turn_2_3 + Turn_3_0 + Turn_3_1 + Turn_3_2 + Turn_3_3 + Turn_1_3 + Turn_1_2 + Turn_1_1 + Turn_1_0 + Turn_0_0 + Turn_0_1 + Turn_0_2 + Turn_0_3 + Turn_0_4 + Turn_1_4 + Turn_3_4 + Turn_2_4) OR (TestIdentity_1_0_0 + TestIdentity_1_0_1 + TestIdentity_1_0_2 + TestIdentity_1_0_3 + TestIdentity_1_0_4 + TestIdentity_1_1_0 + TestIdentity_1_1_1 + TestIdentity_1_1_2 + TestIdentity_1_1_3 + TestIdentity_1_1_4 + TestIdentity_4_0_0 + TestIdentity_4_0_1 + TestIdentity_4_0_2 + TestIdentity_4_0_3 + TestIdentity_4_0_4 + TestIdentity_1_2_0 + TestIdentity_1_2_1 + TestIdentity_1_2_2 + TestIdentity_1_2_3 + TestIdentity_1_2_4 + TestIdentity_4_1_0 + TestIdentity_4_1_1 + TestIdentity_4_1_2 + TestIdentity_4_1_3 + TestIdentity_4_1_4 + TestIdentity_1_3_0 + TestIdentity_1_3_1 + TestIdentity_1_3_2 + TestIdentity_1_3_3 + TestIdentity_1_3_4 + TestIdentity_4_2_0 + TestIdentity_4_2_1 + TestIdentity_4_2_2 + TestIdentity_4_2_3 + TestIdentity_4_2_4 + TestIdentity_4_3_0 + TestIdentity_4_3_1 + TestIdentity_4_3_2 + TestIdentity_4_3_3 + TestIdentity_4_3_4 + TestIdentity_2_0_0 + TestIdentity_2_0_1 + TestIdentity_2_0_2 + TestIdentity_2_0_3 + TestIdentity_2_0_4 + TestIdentity_2_1_0 + TestIdentity_2_1_1 + TestIdentity_2_1_2 + TestIdentity_2_1_3 + TestIdentity_2_1_4 + TestIdentity_2_2_0 + TestIdentity_2_2_1 + TestIdentity_2_2_2 + TestIdentity_2_2_3 + TestIdentity_2_2_4 + TestIdentity_2_3_0 + TestIdentity_2_3_1 + TestIdentity_2_3_2 + TestIdentity_2_3_3 + TestIdentity_2_3_4 + TestIdentity_0_0_0 + TestIdentity_0_0_1 + TestIdentity_0_0_2 + TestIdentity_0_0_3 + TestIdentity_0_0_4 + TestIdentity_0_1_0 + TestIdentity_0_1_1 + TestIdentity_0_1_2 + TestIdentity_0_1_3 + TestIdentity_0_1_4 + TestIdentity_3_0_0 + TestIdentity_3_0_1 + TestIdentity_3_0_2 + TestIdentity_3_0_3 + TestIdentity_3_0_4 + TestIdentity_0_2_0 + TestIdentity_0_2_1 + TestIdentity_0_2_2 + TestIdentity_0_2_3 + TestIdentity_0_2_4 + TestIdentity_3_1_0 + TestIdentity_3_1_1 + TestIdentity_3_1_2 + TestIdentity_3_1_3 + TestIdentity_3_1_4 + TestIdentity_0_3_0 + TestIdentity_0_3_1 + TestIdentity_0_3_2 + TestIdentity_0_3_3 + TestIdentity_0_3_4 + TestIdentity_3_2_0 + TestIdentity_3_2_1 + TestIdentity_3_2_2 + TestIdentity_3_2_3 + TestIdentity_3_2_4 + TestIdentity_3_3_0 + TestIdentity_3_3_1 + TestIdentity_3_3_2 + TestIdentity_3_3_3 + TestIdentity_3_3_4 <= IsEndLoop_0_0_0 + IsEndLoop_0_0_1 + IsEndLoop_0_0_2 + IsEndLoop_0_0_3 + IsEndLoop_0_0_4 + IsEndLoop_0_1_0 + IsEndLoop_0_1_1 + IsEndLoop_0_1_2 + IsEndLoop_0_1_3 + IsEndLoop_0_1_4 + IsEndLoop_3_0_0 + IsEndLoop_3_0_1 + IsEndLoop_3_0_2 + IsEndLoop_3_0_3 + IsEndLoop_3_0_4 + IsEndLoop_0_2_0 + IsEndLoop_0_2_1 + IsEndLoop_0_2_2 + IsEndLoop_0_2_3 + IsEndLoop_0_2_4 + IsEndLoop_3_1_0 + IsEndLoop_3_1_1 + IsEndLoop_3_1_2 + IsEndLoop_3_1_3 + IsEndLoop_3_1_4 + IsEndLoop_0_3_0 + IsEndLoop_0_3_1 + IsEndLoop_0_3_2 + IsEndLoop_0_3_3 + IsEndLoop_0_3_4 + IsEndLoop_3_2_0 + IsEndLoop_3_2_1 + IsEndLoop_3_2_2 + IsEndLoop_3_2_3 + IsEndLoop_3_2_4 + IsEndLoop_3_3_0 + IsEndLoop_3_3_1 + IsEndLoop_3_3_2 + IsEndLoop_3_3_3 + IsEndLoop_3_3_4 + IsEndLoop_1_0_0 + IsEndLoop_1_0_1 + IsEndLoop_1_0_2 + IsEndLoop_1_0_3 + IsEndLoop_1_0_4 + IsEndLoop_1_1_0 + IsEndLoop_1_1_1 + IsEndLoop_1_1_2 + IsEndLoop_1_1_3 + IsEndLoop_1_1_4 + IsEndLoop_4_0_0 + IsEndLoop_4_0_1 + IsEndLoop_4_0_2 + IsEndLoop_4_0_3 + IsEndLoop_4_0_4 + IsEndLoop_1_2_0 + IsEndLoop_1_2_1 + IsEndLoop_1_2_2 + IsEndLoop_1_2_3 + IsEndLoop_1_2_4 + IsEndLoop_4_1_0 + IsEndLoop_4_1_1 + IsEndLoop_4_1_2 + IsEndLoop_4_1_3 + IsEndLoop_4_1_4 + IsEndLoop_1_3_0 + IsEndLoop_1_3_1 + IsEndLoop_1_3_2 + IsEndLoop_1_3_3 + IsEndLoop_1_3_4 + IsEndLoop_4_2_0 + IsEndLoop_4_2_1 + IsEndLoop_4_2_2 + IsEndLoop_4_2_3 + IsEndLoop_4_2_4 + IsEndLoop_4_3_0 + IsEndLoop_4_3_1 + IsEndLoop_4_3_2 + IsEndLoop_4_3_3 + IsEndLoop_4_3_4 + IsEndLoop_2_0_0 + IsEndLoop_2_0_1 + IsEndLoop_2_0_2 + IsEndLoop_2_0_3 + IsEndLoop_2_0_4 + IsEndLoop_2_1_0 + IsEndLoop_2_1_1 + IsEndLoop_2_1_2 + IsEndLoop_2_1_3 + IsEndLoop_2_1_4 + IsEndLoop_2_2_0 + IsEndLoop_2_2_1 + IsEndLoop_2_2_2 + IsEndLoop_2_2_3 + IsEndLoop_2_2_4 + IsEndLoop_2_3_0 + IsEndLoop_2_3_1 + IsEndLoop_2_3_2 + IsEndLoop_2_3_3 + IsEndLoop_2_3_4)) AND NOT(A (G ((TestAlone_4_3_0 +

TestAlone_4_3_1 + TestAlone_4_3_2 + TestAlone_4_3_3 + TestAlone_2_0_0 + TestAlone_2_0_1 + TestAlone_2_0_3 + TestAlone_2_0_4 + TestAlone_2_1_0 + TestAlone_2_1_1 + TestAlone_2_1_3 + TestAlone_2_1_4 + TestAlone_2_2_0 + TestAlone_2_2_1 + TestAlone_2_2_3 + TestAlone_2_2_4 + TestAlone_2_3_0 + TestAlone_2_3_1 + TestAlone_2_3_3 + TestAlone_2_3_4 + TestAlone_0_0_1 + TestAlone_0_0_2 + TestAlone_0_0_3 + TestAlone_0_0_4 + TestAlone_0_1_1 + TestAlone_0_1_2 + TestAlone_0_1_3 + TestAlone_0_1_4 + TestAlone_3_0_0 + TestAlone_3_0_1 + TestAlone_3_0_2 + TestAlone_3_0_4 + TestAlone_4_2_2 + TestAlone_0_2_1 + TestAlone_0_2_2 + TestAlone_0_2_3 + TestAlone_0_2_4 + TestAlone_3_1_0 + TestAlone_3_1_1 + TestAlone_3_1_2 + TestAlone_3_1_4 + TestAlone_4_2_1 + TestAlone_4_2_0 + TestAlone_0_3_1 + TestAlone_0_3_2 + TestAlone_0_3_3 + TestAlone_0_3_4 + TestAlone_3_2_0 + TestAlone_3_2_1 + TestAlone_3_2_2 + TestAlone_3_2_4 + TestAlone_3_3_0 + TestAlone_3_3_1 + TestAlone_3_3_2 + TestAlone_3_3_4 + TestAlone_1_0_0 + TestAlone_1_0_2 + TestAlone_1_0_3 + TestAlone_1_0_4 + TestAlone_1_1_0 + TestAlone_1_1_2 + TestAlone_1_1_3 + TestAlone_1_1_4 + TestAlone_4_0_0 + TestAlone_4_0_1 + TestAlone_4_0_2 + TestAlone_4_0_3 + TestAlone_1_2_0 + TestAlone_1_2_2 + TestAlone_1_2_3 + TestAlone_1_2_4 + TestAlone_4_1_0 + TestAlone_4_1_1 + TestAlone_4_1_2 + TestAlone_4_1_3 + TestAlone_1_3_0 + TestAlone_1_3_2 + TestAlone_1_3_3 + TestAlone_1_3_4 + TestAlone_4_2_3 <= Turn_2_0 + Turn_2_1 + Turn_2_2 + Turn_2_3 + Turn_3_0 + Turn_3_1 + Turn_3_2 + Turn_3_3 + Turn_1_3 + Turn_1_2 + Turn_1_1 + Turn_1_0 + Turn_0_0 + Turn_0_1 + Turn_0_2 + Turn_0_3 + Turn_0_4 + Turn_1_4 + Turn_3_4 + Turn_2_4)))))) : (((TestIdentity_4_3_3 <= TestIdentity_4_2_1) AND E (F (((3 <= TestAlone_3_0_1) AND (BeginLoop_4_2_4 <= BeginLoop_4_3_1))))) OR (IsEndLoop_4_1_3 + 1 <= BeginLoop_2_3_1)) : A (F ((BeginLoop_4_1_2 + 1 <= WantSection_0_T))) : NOT((NOT(E (F ((1 <= TestIdentity_0_3_3)))) AND ((IsEndLoop_3_2_3 <= TestAlone_3_3_4) OR (3 <= BeginLoop_0_1_1)))) : (A (G (A (F ((2 <= IsEndLoop_0_1_2))))) OR (((AskForSection_0_0 <= TestIdentity_3_2_1) AND (EndTurn_4_1 <= Idle_1) AND ((1 <= TestIdentity_4_2_3) OR (3 <= IsEndLoop_4_0_1)) AND (3 <= EndTurn_3_1)) OR (A (G ((TestAlone_3_2_2 <= TestAlone_0_1_4))) OR (((AskForSection_0_1 <= TestIdentity_4_0_2) AND (2 <= TestAlone_2_3_4)) OR (1 <= IsEndLoop_1_0_4))))) : E (G (E (((TestAlone_4_0_0 <= TestIdentity_3_3_1) U (3 <= TestIdentity_3_3_3))))) : NOT(A (F (((Idle_0 <= TestAlone_4_3_0) AND (IsEndLoop_3_2_0 <= TestIdentity_3_3_1) AND (EndTurn_2_1 <= IsEndLoop_2_2_4))))) : (E (G ((2 <= TestIdentity_4_1_4))) OR A (G (E (F ((BeginLoop_0_2_4 <= BeginLoop_2_2_0)))))) : E ((((TestIdentity_1_3_1 <= IsEndLoop_0_2_3) AND (BeginLoop_1_0_4 <= IsEndLoop_4_0_3) AND ((IsEndLoop_2_2_1 <= WantSection_3_F) OR (1 <= AskForSection_3_2))) U (((3 <= BeginLoop_3_3_4) AND (TestAlone_2_2_1 <= TestIdentity_3_0_0)) OR (3 <= BeginLoop_2_1_4))))

lola: computing a collection of formulas

lola: RUNNING

lola: subprocess 0 will run for 221 seconds at most (--localtimelimit=-1)

lola: ========================================

lola: ...considering subproblem: ((TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 + 1 <= AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking a Boolean combination of formulas

lola: RUNNING

lola: subprocess 0 will run for 221 seconds at most (--localtimelimit=-1)

lola: ========================================

lola: ...considering subproblem: (TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 + 1 <= AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking initial satisfaction

lola: processed formula: (TestTurn_0_0 + TestTurn_0_1 + TestTurn_0_2 + TestTurn_0_3 + TestTurn_1_0 + TestTurn_1_1 + TestTurn_1_2 + TestTurn_1_3 + TestTurn_2_0 + TestTurn_2_1 + TestTurn_2_2 + TestTurn_2_3 + TestTurn_3_0 + TestTurn_3_1 + TestTurn_3_2 + TestTurn_3_3 + TestTurn_4_0 + TestTurn_4_1 + TestTurn_4_2 + TestTurn_4_3 + 1 <= AskForSection_0_0 + AskForSection_0_1 + AskForSection_0_2 + AskForSection_0_3 + AskForSection_... (shortened)

lola: processed formula length: 704

lola: 0 rewrites

lola: formula mentions 0 of 480 places; total mentions: 0

lola: closed formula file Peterson-PT-4-CTLCardinality.task

lola: processed formula with 1 atomic propositions

lola: RUNNING

lola: SUBRESULT

lola: result: no

lola: produced by: preprocessing

lola: The net violates the given property already in its initial state.

lola: 0 markings, 0 edges

lola: ========================================

lola: subprocess 1 will run for 236 seconds at most (--localtimelimit=-1)

lola: ========================================

lola: ...considering subproblem: A (G ((((1 <= IsEndLoop_0_0_0 + IsEndLoop_0_0_1 + IsEndLoop_0_0_2 + IsEndLoop_0_0_3 + IsEndLoop_0_0_4 + IsEndLoop_0_1_0 + IsEndLoop_0_1_1 + IsEndLoop_0_1_2 + IsEndLoop_0_1_3 + IsEndLoop_0_1_4 + IsEndLoop_3_0_0 + IsEndLoop_3_0_1 + IsEndLoop_3_0_2 + IsEndLoop_3_0_3 + IsEndLoop_3_0_4 + IsEndLoop_0_2_0 + IsEndLoop_0_2_1 + IsEndLoop_0_2_2 + IsEndLoop_0_2_3 + IsEndLoop_0_2_4 + IsEndLoop_3_1_0 + IsEndLoo... (shortened)

lola: ========================================

lola: SUBTASK

lola: checking invariance

lola: Planning: workflow for reachability check: stateequation||search (--findpath=off)

lola: STORE

lola: using a bit-perfect encoder (--encoder=bit)

lola: using 60 bytes per marking, with 19 unused bits

lola: using a prefix tree store (--store=prefix)

lola: SEARCH (state space)

lola: state space: using reachability graph (--search=depth)

lola: state space: using reachability preserving stubborn set method with insertion algorithm (--stubborn=tarjan)

lola: RUNNING

lola: state equation: Generated DNF with 4 literals and 2 conjunctive subformulas

lola: state equation: write sara problem file to Peterson-PT-4-CTLCardinality.sara

lola: state equation: calling and running sara

sara: try reading problem file Peterson-PT-4-CTLCardinality.sara.

sara: place or transition ordering is non-deterministic

lola: sara is running 0 secs || 236757 markings, 941955 edges, 47351 markings/sec, 0 secs

lola: sara is running 5 secs || 472353 markings, 1896800 edges, 47119 markings/sec, 5 secs

lola: sara is running 10 secs || 704109 markings, 2822983 edges, 46351 markings/sec, 10 secs

lola: sara is running 15 secs || 928486 markings, 3760394 edges, 44875 markings/sec, 15 secs

lola: sara is running 20 secs || 1154490 markings, 4656023 edges, 45201 markings/sec, 20 secs

sara: warning, failure of lp_solve (at job 3690)

lola: sara is running 25 secs || 1370777 markings, 5563052 edges, 43257 markings/sec, 25 secs

lola: sara is running 30 secs || 1594998 markings, 6466420 edges, 44844 markings/sec, 30 secs

lola: sara is running 35 secs || 1822190 markings, 7388255 edges, 45438 markings/sec, 35 secs

lola: sara is running 40 secs || 2043680 markings, 8312993 edges, 44298 markings/sec, 40 secs

lola: sara is running 45 secs || 2265064 markings, 9210625 edges, 44277 markings/sec, 45 secs

lola: sara is running 50 secs || 2481168 markings, 10124279 edges, 43221 markings/sec, 50 secs

lola: sara is running 55 secs || 2695375 markings, 10984922 edges, 42841 markings/sec, 55 secs

lola: sara is running 60 secs || 2914430 markings, 11923252 edges, 43811 markings/sec, 60 secs

lola: sara is running 65 secs || 3135628 markings, 12803891 edges, 44240 markings/sec, 65 secs

lola: sara is running 70 secs || 3357021 markings, 13685250 edges, 44279 markings/sec, 70 secs

lola: sara is running 75 secs || 3570303 markings, 14564795 edges, 42656 markings/sec, 75 secs

lola: sara is running 80 secs || 3794175 markings, 15477677 edges, 44774 markings/sec, 80 secs

lola: sara is running 85 secs || 4015462 markings, 16378638 edges, 44257 markings/sec, 85 secs

lola: sara is running 90 secs || 4246860 markings, 17305700 edges, 46280 markings/sec, 90 secs

lola: sara is running 95 secs || 4466999 markings, 18203082 edges, 44028 markings/sec, 95 secs

lola: sara is running 100 secs || 4692873 markings, 19124090 edges, 45175 markings/sec, 100 secs

lola: sara is running 105 secs || 4906038 markings, 19988143 edges, 42633 markings/sec, 105 secs

lola: sara is running 110 secs || 5123827 markings, 20864030 edges, 43558 markings/sec, 110 secs

lola: sara is running 115 secs || 5339450 markings, 21778408 edges, 43125 markings/sec, 115 secs

lola: sara is running 120 secs || 5558411 markings, 22697346 edges, 43792 markings/sec, 120 secs

lola: sara is running 125 secs || 5772808 markings, 23551522 edges, 42879 markings/sec, 125 secs

lola: sara is running 130 secs || 5984747 markings, 24435800 edges, 42388 markings/sec, 130 secs

lola: sara is running 135 secs || 6190179 markings, 25334363 edges, 41086 markings/sec, 135 secs

lola: sara is running 140 secs || 6413161 markings, 26239484 edges, 44596 markings/sec, 140 secs

lola: sara is running 145 secs || 6638139 markings, 27155192 edges, 44996 markings/sec, 145 secs

lola: sara is running 150 secs || 6867236 markings, 28062370 edges, 45819 markings/sec, 150 secs

lola: sara is running 155 secs || 7087052 markings, 28950505 edges, 43963 markings/sec, 155 secs

lola: sara is running 160 secs || 7303268 markings, 29846108 edges, 43243 markings/sec, 160 secs

lola: sara is running 165 secs || 7513785 markings, 30743076 edges, 42103 markings/sec, 165 secs

lola: sara is running 170 secs || 7723018 markings, 31647666 edges, 41847 markings/sec, 170 secs

lola: sara is running 175 secs || 7929756 markings, 32566192 edges, 41348 markings/sec, 175 secs

lola: sara is running 180 secs || 8133289 markings, 33450523 edges, 40707 markings/sec, 180 secs

lola: sara is running 185 secs || 8331967 markings, 34358846 edges, 39736 markings/sec, 185 secs

lola: sara is running 190 secs || 8537739 markings, 35262638 edges, 41154 markings/sec, 190 secs

lola: sara is running 195 secs || 8741918 markings, 36145413 edges, 40836 markings/sec, 195 secs

lola: sara is running 200 secs || 8940013 markings, 37035904 edges, 39619 markings/sec, 200 secs

lola: sara is running 205 secs || 9134142 markings, 37911074 edges, 38826 markings/sec, 205 secs

lola: sara is running 210 secs || 9329730 markings, 38767362 edges, 39118 markings/sec, 210 secs

lola: sara is running 215 secs || 9529334 markings, 39653032 edges, 39921 markings/sec, 215 secs

lola: local time limit reached - aborting

lola: caught signal User defined signal 1 - aborting LoLA

lola: Child process aborted or communication problem between parent and child process

terminate called after throwing an instance of 'std::runtime_error'

what(): parse error at position 0: unexpected character, last read: '\ufffd'

Aborted (core dumped)

FORMULA Peterson-PT-4-CTLCardinality-0 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-1 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-2 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-3 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-4 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-5 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-6 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-7 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-8 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-9 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-10 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-11 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-12 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-13 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-14 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA Peterson-PT-4-CTLCardinality-15 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

----- Kill lola and sara stdout -----

----- Kill lola and sara stderr -----

----- Finished stderr -----

----- Finished stdout -----

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="Peterson-PT-4"

export BK_EXAMINATION="CTLCardinality"

export BK_TOOL="mcc4mcc-structural"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/Peterson-PT-4.tgz

mv Peterson-PT-4 execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool mcc4mcc-structural"

echo " Input is Peterson-PT-4, examination is CTLCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r119-csrt-152666480100570"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;