About the Execution of ITS-Tools for JoinFreeModules-PT-0005

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15753.640 | 7329.00 | 8841.00 | 415.20 | FTFFTFFFTFTTFFFT | normal |

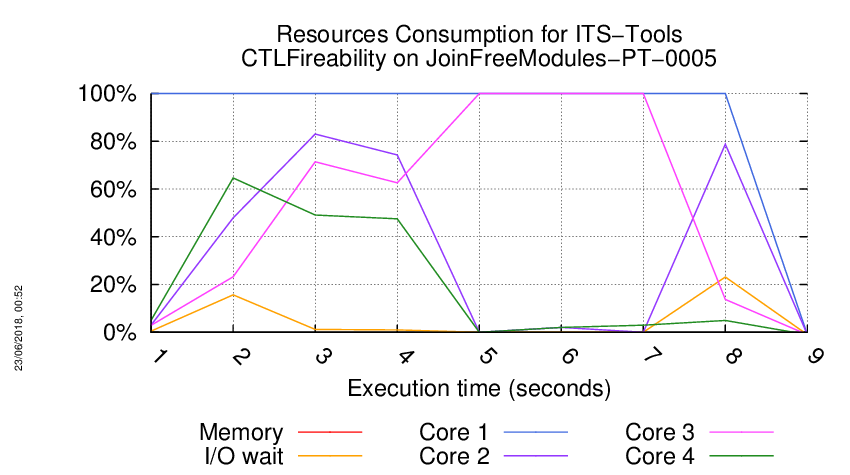

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

...................

/home/mcc/execution

total 192K

-rw-r--r-- 1 mcc users 2.7K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 14K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.7K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 9.9K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.0K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 9.7K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 4.3K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 24K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 114 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 352 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 12K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 5 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 29K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstools

Input is JoinFreeModules-PT-0005, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r104-smll-152658634400242

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-00

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-01

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-02

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-03

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-04

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-05

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-06

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-07

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-08

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-09

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-10

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-11

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-12

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-13

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-14

FORMULA_NAME JoinFreeModules-PT-0005-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1526840300540

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 16 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,1.15927e+10,0.024178,4820,2,192,5,2786,6,0,219,2454,0

Converting to forward existential form...Done !

original formula: AF(AG(EX((p8>=2))))

=> equivalent forward existential formula: [FwdG(Init,!(!(E(TRUE U !(EX((p8>=2)))))))] = FALSE

Reverse transition relation is NOT exact ! Due to transitions t1, t2, t3, t4, t9, t10, t11, t12, t17, t18, t19, t20, t25, t26, t27, t28, t33, t34, t35, t36, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :0/21/20/41

(forward)formula 0,0,0.111309,8012,1,0,115,20904,106,55,1358,18299,109

FORMULA JoinFreeModules-PT-0005-CTLFireability-00 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EF((AG((p8>=1)) + A((p9>=4) U (p25>=5))))

=> equivalent forward existential formula: ([(FwdU(Init,TRUE) * !(E(TRUE U !((p8>=1)))))] != FALSE + [((FwdU(Init,TRUE) * !(EG(!((p25>=5))))) * !(E(!((p25>=5)) U (!((p9>=4)) * !((p25>=5))))))] != FALSE)

(forward)formula 1,1,1.47572,45112,1,0,976,229521,118,497,1363,330605,1029

FORMULA JoinFreeModules-PT-0005-CTLFireability-01 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: EF((!(EF((p21>=3))) * (EG((((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5))) * (p18>=1))))

=> equivalent forward existential formula: [FwdG(((FwdU(Init,TRUE) * !(E(TRUE U (p21>=3)))) * (p18>=1)),(((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5)))] != FALSE

(forward)formula 2,0,1.48002,45376,1,0,987,229973,125,506,1365,331047,1046

FORMULA JoinFreeModules-PT-0005-CTLFireability-02 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: E(EF(((p6>=5)&&(p9>=4))) U (p22>=2))

=> equivalent forward existential formula: [(FwdU(Init,E(TRUE U ((p6>=5)&&(p9>=4)))) * (p22>=2))] != FALSE

(forward)formula 3,0,1.48091,45640,1,0,989,229976,131,507,1366,331051,1051

FORMULA JoinFreeModules-PT-0005-CTLFireability-03 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EG(EF((p6>=5)))

=> equivalent forward existential formula: [FwdG(Init,E(TRUE U (p6>=5)))] != FALSE

(forward)formula 4,1,2.1058,59648,1,0,1185,306816,135,709,1366,446555,1289

FORMULA JoinFreeModules-PT-0005-CTLFireability-04 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: AG(AF(!((p11>=5))))

=> equivalent forward existential formula: [FwdG(FwdU(Init,TRUE),!(!((p11>=5))))] = FALSE

Hit Full ! (commute/partial/dont) 36/0/5

(forward)formula 5,0,2.10989,59912,1,0,1186,307298,142,710,1401,447238,1293

FORMULA JoinFreeModules-PT-0005-CTLFireability-05 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: E(!(AF((p21>=3))) U AG(((p9>=4)||(p17>=2))))

=> equivalent forward existential formula: [(FwdU(Init,!(!(EG(!((p21>=3)))))) * !(E(TRUE U !(((p9>=4)||(p17>=2))))))] != FALSE

(forward)formula 6,0,2.12343,60176,1,0,1197,309754,144,716,1404,449688,1309

FORMULA JoinFreeModules-PT-0005-CTLFireability-06 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: !(AX(EG((p13>=1))))

=> equivalent forward existential formula: [(EY(Init) * !(EG((p13>=1))))] != FALSE

(forward)formula 7,0,2.14883,60704,1,0,1257,314645,149,748,1404,455708,1400

FORMULA JoinFreeModules-PT-0005-CTLFireability-07 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EG((((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5)))

=> equivalent forward existential formula: [FwdG(Init,(((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5)))] != FALSE

Hit Full ! (commute/partial/dont) 20/80/21

(forward)formula 8,1,2.15101,61232,1,0,1257,314645,150,750,1483,455735,1403

FORMULA JoinFreeModules-PT-0005-CTLFireability-08 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: EX(!(EF(((p21>=5)&&(p14>=3)))))

=> equivalent forward existential formula: [(EY(Init) * !(E(TRUE U ((p21>=5)&&(p14>=3)))))] != FALSE

(forward)formula 9,0,2.17982,61760,1,0,1297,319837,151,777,1484,461502,1469

FORMULA JoinFreeModules-PT-0005-CTLFireability-09 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EF((p1>=5))

=> equivalent forward existential formula: [(FwdU(Init,TRUE) * (p1>=5))] != FALSE

(forward)formula 10,1,2.18056,62024,1,0,1299,319858,152,778,1484,461648,1470

FORMULA JoinFreeModules-PT-0005-CTLFireability-10 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: E(E((p25>=5) U (p3>=1)) U (EX((((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5))) * EG((p1>=3))))

=> equivalent forward existential formula: [FwdG((FwdU(Init,E((p25>=5) U (p3>=1))) * EX((((((p3>=5)&&(p8>=5))&&(p13>=5))&&(p18>=5))&&(p23>=5)))),(p1>=3))] != FALSE

Hit Full ! (commute/partial/dont) 36/0/5

(forward)formula 11,1,3.21727,84728,1,0,1508,425931,167,978,1530,663995,1799

FORMULA JoinFreeModules-PT-0005-CTLFireability-11 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: ((p21>=3) + !(EF(((p16>=5)&&(!(p10>=5))))))

=> equivalent forward existential formula: [(FwdU((Init * !((p21>=3))),TRUE) * ((p16>=5)&&(!(p10>=5))))] = FALSE

(forward)formula 12,0,3.2186,84992,1,0,1510,426047,169,979,1533,664089,1801

FORMULA JoinFreeModules-PT-0005-CTLFireability-12 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: !(EX(EF(((p11>=5)&&(p23>=2)))))

=> equivalent forward existential formula: [(FwdU(EY(Init),TRUE) * ((p11>=5)&&(p23>=2)))] = FALSE

(forward)formula 13,0,3.22062,84992,1,0,1512,426184,170,980,1534,664256,1804

FORMULA JoinFreeModules-PT-0005-CTLFireability-13 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: AG(A(((p24>=4)||(p18>=2)) U (p3>=1)))

=> equivalent forward existential formula: ([(FwdU(FwdU(Init,TRUE),!((p3>=1))) * (!(((p24>=4)||(p18>=2))) * !((p3>=1))))] = FALSE * [FwdG(FwdU(Init,TRUE),!((p3>=1)))] = FALSE)

Hit Full ! (commute/partial/dont) 36/0/5

(forward)formula 14,0,3.22879,85256,1,0,1513,427522,177,982,1578,665748,1808

FORMULA JoinFreeModules-PT-0005-CTLFireability-14 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: AG(((EX((p14>=3)) + (((p12>=2)||(p3>=1))||(!(p12>=2)))) + (!(((p14>=4)||(p12>=2))) * EF((p20>=5)))))

=> equivalent forward existential formula: [(((FwdU(Init,TRUE) * !((!(((p14>=4)||(p12>=2))) * E(TRUE U (p20>=5))))) * !((((p12>=2)||(p3>=1))||(!(p12>=2))))) * !(EX((p14>=3))))] = FALSE

(forward)formula 15,1,3.23726,85520,1,0,1518,429102,180,985,1581,667598,1814

FORMULA JoinFreeModules-PT-0005-CTLFireability-15 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

BK_STOP 1526840307869

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution CTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination CTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

May 20, 2018 6:18:22 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

May 20, 2018 6:18:22 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

May 20, 2018 6:18:22 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 55 ms

May 20, 2018 6:18:22 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 26 places.

May 20, 2018 6:18:23 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 41 transitions.

May 20, 2018 6:18:23 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 8 ms

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.DomainAnalyzer computeVariableDomains

INFO: Found a total of 1 fixed domain variables (out of 26 variables) in GAL type JoinFreeModules_PT_0005

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.Simplifier printConstantVars

INFO: Found a total of 1 constant array cells/variables (out of 26 variables) in type JoinFreeModules_PT_0005

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.Simplifier printConstantVars

INFO: p,

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.Simplifier simplifyConstantVariables

INFO: Removed 1 constant variables :p=1

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.Simplifier simplifyConstantVariables

INFO: Simplified 4 expressions due to constant valuations.

May 20, 2018 6:18:23 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 51 ms

May 20, 2018 6:18:23 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 2 ms

May 20, 2018 6:18:23 PM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSCTLTools

INFO: Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 2 ms

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="JoinFreeModules-PT-0005"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/JoinFreeModules-PT-0005.tgz

mv JoinFreeModules-PT-0005 execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstools"

echo " Input is JoinFreeModules-PT-0005, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r104-smll-152658634400242"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;