About the Execution of M4M.full for DLCshifumi-PT-3b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 2097.480 | 227413.00 | 226826.00 | 1198.00 | ???????????????? | normal |

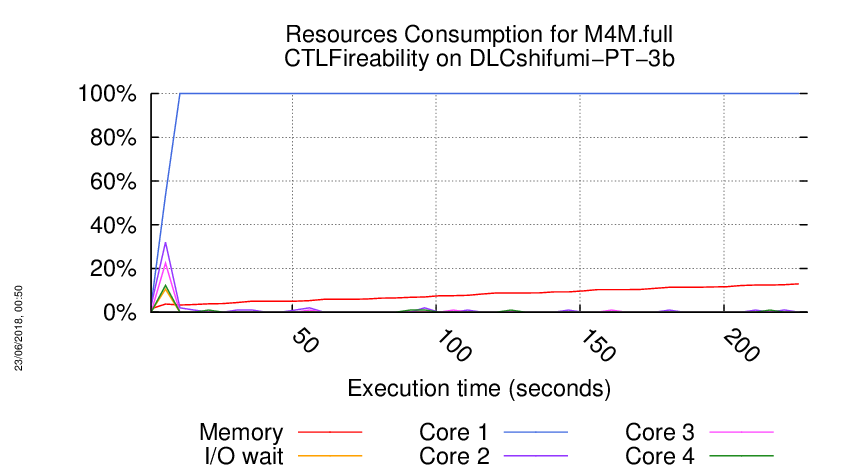

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 2.4M

-rw-r--r-- 1 mcc users 3.2K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 18K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 12K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 9.8K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.4K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 20K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 107 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 345 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.4K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 3 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 2.3M May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool mcc4mcc-full

Input is DLCshifumi-PT-3b, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r070-smll-152649743000179

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-00

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-01

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-02

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-03

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-04

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-05

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-06

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-07

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-08

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-09

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-10

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-11

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-12

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-13

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-14

FORMULA_NAME DLCshifumi-PT-3b-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1526724208650

BK_STOP 1526724436063

--------------------

content from stderr:

Prefix is 65b80f64.

Reading known information in /usr/share/mcc4mcc/65b80f64-known.json.

Reading learned information in /usr/share/mcc4mcc/65b80f64-learned.json.

Reading value translations in /usr/share/mcc4mcc/65b80f64-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using DLCshifumi-PT-3b as instance name.

Using DLCshifumi as model name.

Using algorithm or tool voting-classifier.

Model characteristics are: {'Examination': 'CTLFireability', 'Place/Transition': True, 'Colored': False, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': False, 'Source Place': True, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': None, 'Conservative': False, 'Sub-Conservative': False, 'Nested Units': True, 'Safe': True, 'Deadlock': None, 'Reversible': None, 'Quasi Live': None, 'Live': None}.

/usr/local/lib/python3.6/dist-packages/sklearn/preprocessing/label.py:151: DeprecationWarning: The truth value of an empty array is ambiguous. Returning False, but in future this will result in an error. Use `array.size > 0` to check that an array is not empty.

if diff:

Known tools are: [{'Time': 496152, 'Memory': 2885.35, 'Tool': 'lola'}, {'Time': 496331, 'Memory': 2876.92, 'Tool': 'lola'}].

Learned tools are: [{'Tool': 'lola'}].

Learned tool lola is 1.0x far from the best tool lola.

CTLFireability lola DLCshifumi-PT-3b...

Time: 3600 - MCC

----- Start make prepare stdout -----

----- Start make prepare stderr -----

===========================================================================================

DLCshifumi-PT-3b: translating PT Petri net model.pnml into LoLA format

===========================================================================================

translating PT Petri net complete

checking for too many tokens

===========================================================================================

DLCshifumi-PT-3b: translating PT formula CTLFireability into LoLA format

===========================================================================================

translating formula complete

touch formulae;

----- Start make result stdout -----

----- Start make result stderr -----

CTLFireability @ DLCshifumi-PT-3b @ 3540 seconds

Makefile:222: recipe for target 'verify' failed

make: [verify] Error 134 (ignored)

----- Start make result stderr -----

----- Start make result stdout -----

lola: LoLA will run for 3540 seconds at most (--timelimit)

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 16669/65536 symbol table entries, 5526 collisions

lola: preprocessing...

lola: finding significant places

lola: 7058 places, 9611 transitions, 6776 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 12409 transition conflict sets

lola: TASK

lola: reading formula from DLCshifumi-PT-3b-CTLFireability.task

lola: NOT(NOT(A (G (E (F (FIREABLE(t8634))))))) : E (F (FIREABLE(t4569))) : A (G (E (F (FIREABLE(t1939))))) : E (G ((FIREABLE(t5842) OR E (F ((FIREABLE(t717) AND FIREABLE(t4067))))))) : A (G (E (G ((NOT FIREABLE(t1585) OR NOT FIREABLE(t1773)))))) : A (G (NOT FIREABLE(t3022))) : E ((E (G (NOT FIREABLE(t7872))) U (A (G (FIREABLE(t7173))) AND A (X (FIREABLE(t2884)))))) : (A (G (FIREABLE(t8830))) OR E (F ((NOT FIREABLE(t3223) AND NOT FIREABLE(t1718) AND FIREABLE(t6594))))) : A ((((NOT FIREABLE(t8494) OR NOT FIREABLE(t3091)) OR E (F (FIREABLE(t1775)))) U A (X (FIREABLE(t3323))))) : E (X (A (X (E (F (FIREABLE(t1381))))))) : A (F (E (F (A (G (FIREABLE(t4706))))))) : (E ((E (G (FIREABLE(t3587))) U NOT FIREABLE(t1756))) AND NOT((A ((FIREABLE(t7490) U FIREABLE(t8117))) OR A (G (NOT FIREABLE(t1583)))))) : A (F (FIREABLE(t3141))) : (E (F (FIREABLE(t8614))) OR (FIREABLE(t2630) AND NOT FIREABLE(t7262) AND ((FIREABLE(t2167) AND FIREABLE(t8003)) OR FIREABLE(t5760)))) : A (F (FIREABLE(t1658))) : A (X (E (F (FIREABLE(t3785)))))

lola: computing a collection of formulas

lola: RUNNING

lola: subprocess 0 will run for 221 seconds at most (--localtimelimit=-1)

lola: ========================================

lola: ...considering subproblem: NOT(NOT(A (G (E (F (FIREABLE(t8634)))))))

lola: ========================================

lola: SUBTASK

lola: checking liveness

lola: liveness not yet implemented, converting to CTL...

lola: processed formula: NOT(E(TRUE U NOT(E(TRUE U FIREABLE(t8634)))))

lola: processed formula length: 45

lola: 12 rewrites

lola: formula mentions 0 of 7058 places; total mentions: 0

lola: closed formula file DLCshifumi-PT-3b-CTLFireability.task

lola: STORE

lola: using a bit-perfect encoder (--encoder=bit)

lola: using 848 bytes per marking, with 8 unused bits

lola: using a prefix tree store (--store=prefix)

lola: Using CTL preserving stubborn sets

lola: RUNNING

lola: CTL formula contains 2 significant temporal operators and needs 9 bytes of payload

lola: Ignoring fairness constraints (--fair).

lola: 73960 markings, 200838 edges, 3689348869717491712 markings/sec, 0 secs

lola: 133137 markings, 415211 edges, 11835 markings/sec, 5 secs

lola: 232895 markings, 618111 edges, 19952 markings/sec, 10 secs

lola: 289131 markings, 835289 edges, 11247 markings/sec, 15 secs

lola: 451208 markings, 1024165 edges, 32415 markings/sec, 20 secs

lola: 589365 markings, 1219137 edges, 27631 markings/sec, 25 secs

lola: 589365 markings, 1447186 edges, 0 markings/sec, 30 secs

lola: 589365 markings, 1677007 edges, 0 markings/sec, 35 secs

lola: 589365 markings, 1912196 edges, 0 markings/sec, 40 secs

lola: 723509 markings, 2111898 edges, 26829 markings/sec, 45 secs

lola: 884863 markings, 2303277 edges, 32271 markings/sec, 50 secs

lola: 884863 markings, 2536085 edges, 0 markings/sec, 55 secs

lola: 884863 markings, 2771905 edges, 0 markings/sec, 60 secs

lola: 932811 markings, 2994556 edges, 9590 markings/sec, 65 secs

lola: 1021305 markings, 3203939 edges, 17699 markings/sec, 70 secs

lola: 1054996 markings, 3430928 edges, 6738 markings/sec, 75 secs

lola: 1139988 markings, 3645516 edges, 16998 markings/sec, 80 secs

lola: 1169649 markings, 3870098 edges, 5932 markings/sec, 85 secs

lola: 1326075 markings, 4064869 edges, 31285 markings/sec, 90 secs

lola: 1336737 markings, 4295138 edges, 2132 markings/sec, 95 secs

lola: 1384047 markings, 4517911 edges, 9462 markings/sec, 100 secs

lola: 1551651 markings, 4712225 edges, 33521 markings/sec, 105 secs

lola: 1669268 markings, 4909702 edges, 23523 markings/sec, 110 secs

lola: 1669268 markings, 5144722 edges, 0 markings/sec, 115 secs

lola: 1669268 markings, 5377829 edges, 0 markings/sec, 120 secs

lola: 1699066 markings, 5599700 edges, 5960 markings/sec, 125 secs

lola: 1824443 markings, 5797604 edges, 25075 markings/sec, 130 secs

lola: 1824443 markings, 6027236 edges, 0 markings/sec, 135 secs

lola: 1967212 markings, 6221151 edges, 28554 markings/sec, 140 secs

lola: 2121138 markings, 6408035 edges, 30785 markings/sec, 145 secs

lola: 2121138 markings, 6635665 edges, 0 markings/sec, 150 secs

lola: 2121138 markings, 6864250 edges, 0 markings/sec, 155 secs

lola: 2158255 markings, 7084055 edges, 7423 markings/sec, 160 secs

lola: 2320594 markings, 7273162 edges, 32468 markings/sec, 165 secs

lola: 2433967 markings, 7469575 edges, 22675 markings/sec, 170 secs

lola: 2433967 markings, 7698225 edges, 0 markings/sec, 175 secs

lola: 2433967 markings, 7927130 edges, 0 markings/sec, 180 secs

lola: 2486320 markings, 8141706 edges, 10471 markings/sec, 185 secs

lola: 2519668 markings, 8359900 edges, 6670 markings/sec, 190 secs

lola: 2676919 markings, 8547992 edges, 31450 markings/sec, 195 secs

lola: 2727793 markings, 8761562 edges, 10175 markings/sec, 200 secs

lola: 2727793 markings, 8990791 edges, 0 markings/sec, 205 secs

lola: 2774012 markings, 9208417 edges, 9244 markings/sec, 210 secs

lola: 2911943 markings, 9401489 edges, 27586 markings/sec, 215 secs

lola: local time limit reached - aborting

lola: Child process aborted or communication problem between parent and child process

terminate called after throwing an instance of 'std::runtime_error'

what(): parse error at position 0: unexpected character, last read: '

Aborted (core dumped)

FORMULA DLCshifumi-PT-3b-CTLFireability-0 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-1 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-2 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-3 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-4 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-5 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-6 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-7 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-8 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-9 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-10 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-11 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-12 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-13 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-14 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

FORMULA DLCshifumi-PT-3b-CTLFireability-15 CANNOT_COMPUTE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT STATE_COMPRESSION STUBBORN_SETS TOPOLOGICAL USE_NUPN

----- Kill lola and sara stdout -----

----- Kill lola and sara stderr -----

----- Finished stdout -----

----- Finished stderr -----

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCshifumi-PT-3b"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="mcc4mcc-full"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCshifumi-PT-3b.tgz

mv DLCshifumi-PT-3b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool mcc4mcc-full"

echo " Input is DLCshifumi-PT-3b, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r070-smll-152649743000179"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;