About the Execution of M4M.full for DLCround-PT-03a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 1013.430 | 218314.00 | 390511.00 | 1038.30 | F | normal |

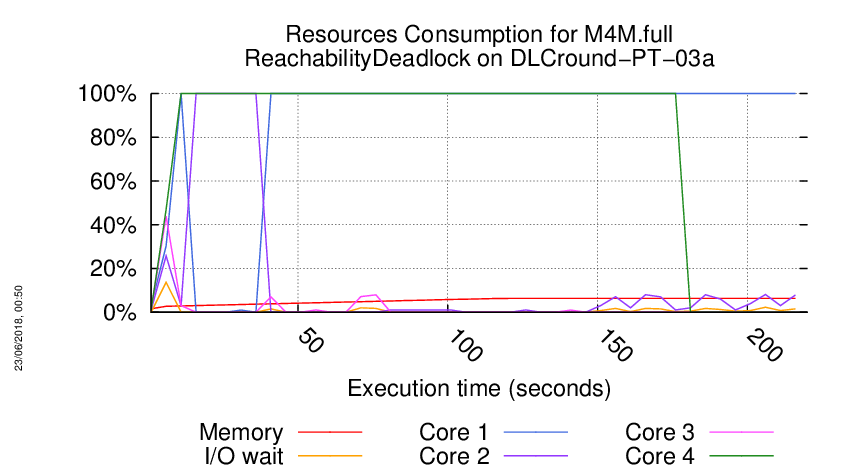

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 316K

-rw-r--r-- 1 mcc users 3.2K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 17K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 11K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 9.1K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.3K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 17K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 106 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 344 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 3.0K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 20K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 4 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 148K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool mcc4mcc-full

Input is DLCround-PT-03a, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r070-smll-152649742700006

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-03a-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1526639198404

BK_STOP 1526639416718

--------------------

content from stderr:

Prefix is 65b80f64.

Reading known information in /usr/share/mcc4mcc/65b80f64-known.json.

Reading learned information in /usr/share/mcc4mcc/65b80f64-learned.json.

Reading value translations in /usr/share/mcc4mcc/65b80f64-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using DLCround-PT-03a as instance name.

Using DLCround as model name.

Using algorithm or tool bmdt.

Model characteristics are: {'Examination': 'ReachabilityDeadlock', 'Place/Transition': True, 'Colored': False, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': False, 'Source Place': True, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': None, 'Conservative': False, 'Sub-Conservative': False, 'Nested Units': True, 'Safe': True, 'Deadlock': None, 'Reversible': None, 'Quasi Live': None, 'Live': None}.

Known tools are: [{'Time': 2641, 'Memory': 2207.29, 'Tool': 'marcie'}, {'Time': 3116, 'Memory': 266.59, 'Tool': 'itstools'}, {'Time': 4593, 'Memory': 179.88, 'Tool': 'gspn'}, {'Time': 146024, 'Memory': 697.21, 'Tool': 'lola'}].

Learned tools are: [{'Tool': 'lola'}].

Learned tool lola is 55.29117758424839x far from the best tool marcie.

ReachabilityDeadlock lola DLCround-PT-03a...

----- Start make prepare stderr -----

Time: 3600 - MCC

----- Start make prepare stdout -----

===========================================================================================

DLCround-PT-03a: translating PT Petri net model.pnml into LoLA format

===========================================================================================

translating PT Petri net complete

checking for too many tokens

===========================================================================================

DLCround-PT-03a: translating PT formula ReachabilityDeadlock into LoLA format

===========================================================================================

translating formula complete

touch formulae;

----- Start make result stdout -----

----- Start make result stderr -----

ReachabilityDeadlock @ DLCround-PT-03a @ 3540 seconds

----- Start make result stdout -----

----- Start make result stderr -----

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 730/65536 symbol table entries, 0 collisions

lola: preprocessing...

lola: finding significant places

lola: 113 places, 617 transitions, 61 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 518 transition conflict sets

lola: TASK

lola: reading formula from DLCround-PT-03a-ReachabilityDeadlock.task

lola: E (F (DEADLOCK))

lola: E (F (DEADLOCK))

lola: checking reachability of deadlocks

lola: Planning: workflow for deadlock check: siphon||findpath||search) (--findpath=par,--siphontrap=par)

lola: STORE

lola: using a bit-perfect encoder (--encoder=bit)

lola: using 8 bytes per marking, with 3 unused bits

lola: using a prefix tree store (--store=prefix)

lola: SEARCH (state space)

lola: state space: using reachability graph (--search=depth)

lola: state space: using deadlock preserving stubborn set method with insertion algorithm(--stubborn=tarjan)

lola: SEARCH (findpath)

lola: findpath: using deadlock preserving stubborn set method with insertion algorithm (--stubborn=tarjan)

lola: RUNNING

lola: findpath: starting randomized, memory-less exploration (--search=findpath)

lola: findpath: searching for paths with maximal depth 1000000 (--depthlimit)

lola: findpath: no retry limit given (--retrylimit)

lola: findpath: transitions are chosen randomly

lola: computing symmetries (--symmetry)

lola: time limit for symmetry computation of 300 seconds given (--symmtimelimit)

lola: STP: formula with 9266 variables and 37713 clauses shipped to Minisat

lola: computed 22 generators (10 in search tree, 12 by composition)

lola: representing 9216 symmetries

lola: 0 dead branches visited in search tree

lola: stp: The siphon/trap property does not hold

lola: STP completed || 1 tries, 73575 fired transitions, 0 secs || 136399 markings, 1512408 edges, 27280 markings/sec, 0 secs

lola: STP completed || 1 tries, 147676 fired transitions, 5 secs || 277989 markings, 3110247 edges, 28318 markings/sec, 5 secs

lola: STP completed || 1 tries, 224492 fired transitions, 10 secs || 422928 markings, 4719733 edges, 28988 markings/sec, 10 secs

lola: STP completed || 1 tries, 300838 fired transitions, 15 secs || 566484 markings, 6340291 edges, 28711 markings/sec, 15 secs

lola: STP completed || 1 tries, 377783 fired transitions, 20 secs || 708389 markings, 7941450 edges, 28381 markings/sec, 20 secs

lola: STP completed || 1 tries, 454491 fired transitions, 25 secs || 852127 markings, 9560540 edges, 28748 markings/sec, 25 secs

lola: STP completed || 1 tries, 527783 fired transitions, 30 secs || 993625 markings, 11169390 edges, 28300 markings/sec, 30 secs

lola: STP completed || 1 tries, 605055 fired transitions, 35 secs || 1138644 markings, 12782957 edges, 29004 markings/sec, 35 secs

lola: STP completed || 1 tries, 682142 fired transitions, 40 secs || 1282587 markings, 14393410 edges, 28789 markings/sec, 40 secs

lola: STP completed || 1 tries, 759163 fired transitions, 45 secs || 1426027 markings, 16015916 edges, 28688 markings/sec, 45 secs

lola: STP completed || 1 tries, 836355 fired transitions, 50 secs || 1571096 markings, 17643498 edges, 29014 markings/sec, 50 secs

lola: STP completed || 1 tries, 913369 fired transitions, 55 secs || 1714017 markings, 19284774 edges, 28584 markings/sec, 55 secs

lola: STP completed || 1 tries, 990272 fired transitions, 60 secs || 1858628 markings, 20933104 edges, 28922 markings/sec, 60 secs

lola: STP completed || 2 tries, 1067560 fired transitions, 65 secs || 2003146 markings, 22589315 edges, 28904 markings/sec, 65 secs

lola: STP completed || 2 tries, 1144800 fired transitions, 70 secs || 2149955 markings, 24266068 edges, 29362 markings/sec, 70 secs

lola: STP completed || 2 tries, 1222197 fired transitions, 75 secs || 2297916 markings, 25953312 edges, 29592 markings/sec, 75 secs

lola: STP completed || 2 tries, 1299710 fired transitions, 80 secs || 2442815 markings, 27640706 edges, 28980 markings/sec, 80 secs

lola: STP completed || 2 tries, 1377165 fired transitions, 85 secs || 2589174 markings, 29321328 edges, 29272 markings/sec, 85 secs

lola: STP completed || 2 tries, 1454664 fired transitions, 90 secs || 2732681 markings, 31012283 edges, 28701 markings/sec, 90 secs

lola: STP completed || 2 tries, 1532612 fired transitions, 95 secs || 2878858 markings, 32753508 edges, 29235 markings/sec, 95 secs

lola: STP completed || 2 tries, 1610383 fired transitions, 100 secs || 3028147 markings, 34511743 edges, 29858 markings/sec, 100 secs

lola: STP completed || 2 tries, 1688183 fired transitions, 105 secs || 3177865 markings, 36393451 edges, 29944 markings/sec, 105 secs

lola: STP completed || 2 tries, 1768059 fired transitions, 110 secs || 3287400 markings, 39671659 edges, 21907 markings/sec, 110 secs

lola: STP completed || 2 tries, 1848893 fired transitions, 115 secs || 3371976 markings, 43811255 edges, 16915 markings/sec, 115 secs

lola: STP completed || 2 tries, 1930237 fired transitions, 120 secs || 3450271 markings, 47969127 edges, 15659 markings/sec, 120 secs

lola: STP completed || 3 tries, 2011483 fired transitions, 125 secs || 3527688 markings, 52144086 edges, 15483 markings/sec, 125 secs

lola: STP completed || 3 tries, 2092710 fired transitions, 130 secs || 3602827 markings, 56217298 edges, 15028 markings/sec, 130 secs

lola: STP completed || 3 tries, 2174065 fired transitions, 135 secs || 3678540 markings, 60224318 edges, 15143 markings/sec, 135 secs

lola: STP completed || 3 tries, 2255264 fired transitions, 140 secs || 3750257 markings, 64208664 edges, 14343 markings/sec, 140 secs

lola: STP completed || 3 tries, 2336360 fired transitions, 145 secs || 3819225 markings, 68234147 edges, 13794 markings/sec, 145 secs

lola: STP completed || 3 tries, 2417371 fired transitions, 150 secs || 3889588 markings, 72267639 edges, 14073 markings/sec, 150 secs

lola: STP completed || 3 tries, 2498533 fired transitions, 155 secs || 3960463 markings, 76371639 edges, 14175 markings/sec, 155 secs

lola: STP completed || 3 tries, 2579657 fired transitions, 160 secs || 4026555 markings, 80524732 edges, 13218 markings/sec, 160 secs

lola: STP completed || 3 tries, 2660817 fired transitions, 165 secs || 4091939 markings, 84853006 edges, 13077 markings/sec, 165 secs

lola: RESULT

lola: result: no

lola: produced by: state space

lola: The net does not have deadlocks.

lola: 4126465 markings, 87132673 edges

FORMULA DLCround-PT-03a-ReachabilityDeadlock-0 FALSE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT SAT_SMT STATE_COMPRESSION STUBBORN_SETS SYMMETRIES TOPOLOGICAL USE_NUPN

----- Kill lola and sara stdout -----

----- Kill lola and sara stderr -----

----- Finished stderr -----

----- Finished stdout -----

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-03a"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="mcc4mcc-full"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-03a.tgz

mv DLCround-PT-03a execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool mcc4mcc-full"

echo " Input is DLCround-PT-03a, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r070-smll-152649742700006"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;