About the Execution of ITS-Tools.L for DLCround-PT-04b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15752.700 | 541126.00 | 556964.00 | 1831.70 | [undef] | Cannot compute |

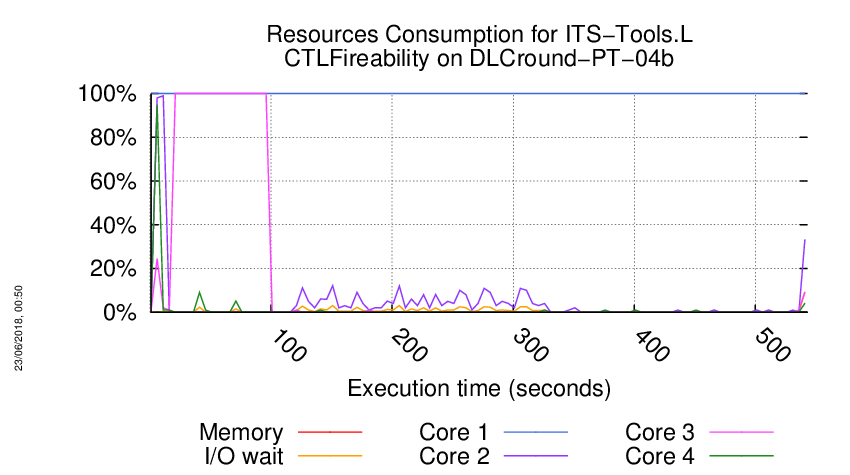

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 708K

-rw-r--r-- 1 mcc users 3.5K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 18K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 9.5K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 9.7K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.2K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 15K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 106 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 344 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.4K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 4 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 547K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstoolsl

Input is DLCround-PT-04b, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r069-smll-152649741700025

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-04b-CTLFireability-00

FORMULA_NAME DLCround-PT-04b-CTLFireability-01

FORMULA_NAME DLCround-PT-04b-CTLFireability-02

FORMULA_NAME DLCround-PT-04b-CTLFireability-03

FORMULA_NAME DLCround-PT-04b-CTLFireability-04

FORMULA_NAME DLCround-PT-04b-CTLFireability-05

FORMULA_NAME DLCround-PT-04b-CTLFireability-06

FORMULA_NAME DLCround-PT-04b-CTLFireability-07

FORMULA_NAME DLCround-PT-04b-CTLFireability-08

FORMULA_NAME DLCround-PT-04b-CTLFireability-09

FORMULA_NAME DLCround-PT-04b-CTLFireability-10

FORMULA_NAME DLCround-PT-04b-CTLFireability-11

FORMULA_NAME DLCround-PT-04b-CTLFireability-12

FORMULA_NAME DLCround-PT-04b-CTLFireability-13

FORMULA_NAME DLCround-PT-04b-CTLFireability-14

FORMULA_NAME DLCround-PT-04b-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1527235201724

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/CTLFireability.pnml.gal, -t, CGAL, -ctl, /home/mcc/execution/CTLFireability.ctl], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.pnml.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 16 CTL formulae.

built 4 ordering constraints for composite.

built 689 ordering constraints for composite.

built 584 ordering constraints for composite.

built 479 ordering constraints for composite.

built 374 ordering constraints for composite.

built 269 ordering constraints for composite.

built 164 ordering constraints for composite.

built 123 ordering constraints for composite.

built 82 ordering constraints for composite.

built 740 ordering constraints for composite.

built 726 ordering constraints for composite.

built 712 ordering constraints for composite.

built 698 ordering constraints for composite.

built 684 ordering constraints for composite.

built 670 ordering constraints for composite.

built 656 ordering constraints for composite.

built 642 ordering constraints for composite.

built 628 ordering constraints for composite.

built 614 ordering constraints for composite.

built 600 ordering constraints for composite.

built 586 ordering constraints for composite.

built 572 ordering constraints for composite.

built 558 ordering constraints for composite.

built 544 ordering constraints for composite.

built 530 ordering constraints for composite.

built 516 ordering constraints for composite.

built 502 ordering constraints for composite.

built 488 ordering constraints for composite.

built 474 ordering constraints for composite.

built 460 ordering constraints for composite.

built 445 ordering constraints for composite.

built 437 ordering constraints for composite.

built 422 ordering constraints for composite.

built 414 ordering constraints for composite.

built 399 ordering constraints for composite.

built 391 ordering constraints for composite.

built 376 ordering constraints for composite.

built 368 ordering constraints for composite.

built 353 ordering constraints for composite.

built 345 ordering constraints for composite.

built 330 ordering constraints for composite.

built 322 ordering constraints for composite.

built 307 ordering constraints for composite.

built 299 ordering constraints for composite.

built 284 ordering constraints for composite.

built 276 ordering constraints for composite.

built 261 ordering constraints for composite.

built 253 ordering constraints for composite.

built 238 ordering constraints for composite.

built 230 ordering constraints for composite.

built 215 ordering constraints for composite.

built 207 ordering constraints for composite.

built 192 ordering constraints for composite.

built 184 ordering constraints for composite.

built 169 ordering constraints for composite.

built 161 ordering constraints for composite.

built 146 ordering constraints for composite.

built 138 ordering constraints for composite.

built 123 ordering constraints for composite.

built 115 ordering constraints for composite.

built 100 ordering constraints for composite.

built 92 ordering constraints for composite.

built 77 ordering constraints for composite.

built 69 ordering constraints for composite.

built 54 ordering constraints for composite.

built 46 ordering constraints for composite.

built 31 ordering constraints for composite.

built 23 ordering constraints for composite.

terminate called after throwing an instance of 'std::bad_alloc'

what(): std::bad_alloc

BK_STOP 1527235742850

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution CTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination CTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

May 25, 2018 8:00:04 AM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, CTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -louvain, -smt]

May 25, 2018 8:00:04 AM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

May 25, 2018 8:00:04 AM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 308 ms

May 25, 2018 8:00:04 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1680 places.

May 25, 2018 8:00:05 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 2364 transitions.

May 25, 2018 8:00:05 AM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

May 25, 2018 8:00:05 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 81 ms

May 25, 2018 8:00:05 AM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

May 25, 2018 8:00:05 AM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 527 ms

May 25, 2018 8:00:06 AM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 326 ms

May 25, 2018 8:00:06 AM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

May 25, 2018 8:00:06 AM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 273 ms

May 25, 2018 8:00:06 AM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

May 25, 2018 8:00:15 AM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 1143 redundant transitions.

May 25, 2018 8:00:15 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/CTLFireability.pnml.gal : 68 ms

May 25, 2018 8:00:15 AM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSCTLTools

INFO: Time to serialize properties into /home/mcc/execution/CTLFireability.ctl : 4 ms

ITS-tools command line returned an error code 134

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-04b"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="itstoolsl"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-04b.tgz

mv DLCround-PT-04b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstoolsl"

echo " Input is DLCround-PT-04b, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r069-smll-152649741700025"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;